采用MCU拯救嵌入式系统设计新集成度

描述

嵌入式系统已成为生活中不可或缺的一部分。嵌入式系统的各种创新开辟了几个新的商机,吸引了行业巨头和创业公司的关注。不断增长的业务潜力促使公司投资于未来的产品创新。嵌入式设计师一直面临着创新的压力,以满足这些市场需求。

随着商业潜力的增加,许多公司已经进入这个领域,创造了激烈的竞争。为了实现差异化,公司正专注于增强产品供应和优化成本竞争力。

微控制器是嵌入式系统的关键组件,必须跟上不断变化的系统需求的挑战。这导致PIC®微控制器的推出与Microchip Technology的集成度达到了新的水平。

具有内核独立外设的PIC单片机

这些新型PIC单片机引入了 - 芯片独立核心外设(CIP)提供灵活性,可扩展性和增强性能,以满足不断变化的创新需求,同时仍保持低功耗和成本竞争力。

CIP提供增强的性能,灵活性和可扩展性具有以下功能:

独立模块,无需中央处理单元(CPU)的持续监控即可运行

高吞吐量和接近零延迟的专用硬件

与其他片上外设直接交互以实现自持式闭环系统,提供更高的集成度

智能模块几乎不需要处理器资源即可运行

低功耗消费与capabi在节能模式下运行,使其成为低功耗设计的理想选择

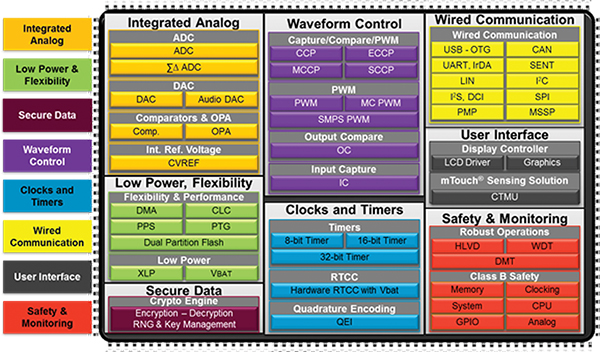

图1:Microchip的带有CIP的PIC单片机提供多种功能优势

CIP采用硬件设计,以经济高效的方式实现目标功能。与需要闪存,RAM,必要处理器带宽和外部组件的用户固件类似的实现相比,使用CIP设计系统功能的增量成本要低得多。 CIP允许PIC MCU执行极其复杂和专用的任务,几乎不与CPU交互。这样可以降低整体功耗,同时还可以释放CPU来执行其他任务。此外,通过使用集成外设替换片外分立元件,CIP可显着节省BOM成本。此外,CIP使并行处理能够与CPU一起实现,以实现复杂的功能,而无需具有更高处理能力的更昂贵的MCU。

PIC微控制器中的外设集成

CIP存在于许多PIC MCU上,包括PIC16,PIC18,PIC24,dsPIC33和PIC32MM系列。 16位PIC24和dsPIC33器件中包含的一些CIP包括外设触发发生器(PTG),可配置逻辑单元(CLC),带随机数发生器(RNG)的加密引擎,带有消隐和数字滤波器功能的高速比较器,和多个捕捉/比较/PWM(MCCP)。

图2:新PIC MCU中的外设集成

使用CIP提高性能

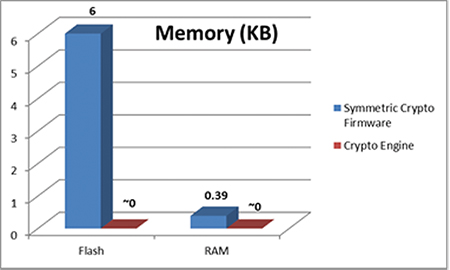

核心独立外设降低了处理器资源需求并允许并行处理的实现,从而导致增强性能。例如,加密引擎能够支持AES,DES和3DES对称加密和解密。为了在软件中实现这些例程,它需要大约1-6 KB的Flash和100-400字节的RAM。通过使用加密引擎CIP,几乎没有Flash或RAM要求,这些资源可用于执行最终应用程序的其他功能。

图3:加密/解密的闪存和RAM要求

作为硬件模块的加密引擎与软件中的类似实现相比具有非常高的吞吐量。加密引擎CIP执行加密和解密的速度大约是软件加密实现的十倍,同时消耗的功率几乎相同。这些是需要高度安全数据吞吐量的功耗敏感应用的重要因素。几乎相同功耗下的高吞吐量将应用的整体能效提高了大约十倍。由于此CPU在CPU处于待机状态时也能够在低功耗模式下运行,因此可以在需要安全性的电池供电应用中实现整体较低的系统功耗,例如物联网(IoT)应用。

用于系统功能扩展和成本节约的CIP

随着需求的发展和促进创新,CIP有助于扩展系统功能。外设触发发生器(PTG)是一个用户可编程的序列发生器,可以生成具有复杂输入的触发器,以协调其他外设的操作。作为“核心独立”,PTG在一个外围设备中满足多个系统需求。 PTG减少了对CPU干预的需求,并带来了将多个外设连接到闭环系统的灵活性和可扩展性,从而扩展了整个系统的功能。

PTG可以有效地用于实现电机控制中的集成功率因数校正等应用。该应用需要三个PWM通道来控制电机功能,另外还需要一个PWM来控制功率因数校正(PFC)操作。可以使用简单的输出比较(OC)外设来增加器件上可用的PWM通道数量,超出高速PWM通道。但是,在PFC等应用中,最佳执行时间对于在给定的时间窗口内完成以下任务非常重要:

同步电机控制PWM和PFC PWM

触发模数转换器(ADC)动作和切换用于电机控制和PFC信号的ADC通道

这些要求,同步以及ADC触发生成都得到有效解决通过单个PTG模块。通过PTG实现PFC与电机控制的集成,它还消除了对双芯片设计的需求,从而显着降低了系统级成本。

能效

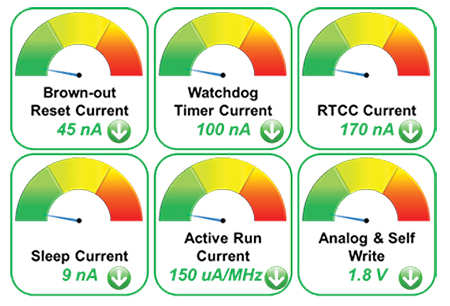

便携式设备,手持设备,可穿戴设备和家庭安全是一些最受欢迎的物联网应用。这些应用由电池供电,必须在充电或更换之间延长使用寿命。在这些应用中使用的微控制器必须经过功率优化和灵活,以实现节能设计。采用CIP的新一代极低功耗(XLP)PIC MCU提供业界最佳的低功耗规范,以满足低功耗设计要求。

图4:XLP PIC MCU提供同类最佳的电源规格

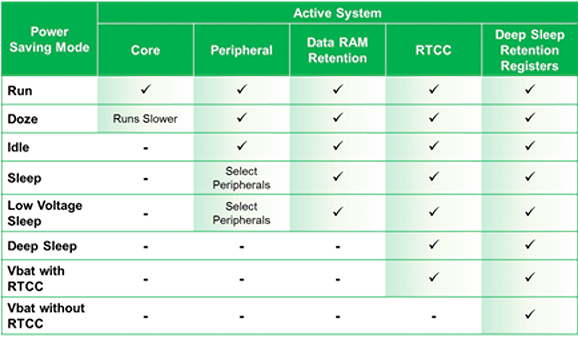

XLP MCU提供一系列低功耗模式,以满足各种设计要求。 XLP模式根据用户配置保持MCU的不同资源处于活动状态,而其余模块则关闭。

图5:省电模式XLP PIC MCU的实现

为了增强功耗,XLP PIC MCU中的CIP也消耗最少的功率,以帮助实现低功耗实现。

使用CIP提升产品

由于激烈的竞争,许多嵌入式公司都在寻求差异化产品和增强产品,同时最大限度地降低成本。多功能CIP可实现产品增强,无需额外开销。例如,在提高无人机的承载能力的情况下,需要更高的每分钟转数(RPM)马达。较高转速的电机控制通常要求MCU具有更高的处理能力和先进的模拟功能,如高采样率和多通道ADC。然而,具有消隐和数字滤波器功能的高速比较器(HS比较器)等CIP的存在以及MCU中的精密电压参考模块消除了迁移到先进,成本更高的MCU的需要。外围组合用作阈值信号监视器并有效地监视电动机参数。由于HS比较器没有正常ADC的低采样率限制,因此无需在MCU中使用高速ADC。如前所述,CIP的所有这些优势减少了对额外处理器资源的需求,并且无需迁移到更昂贵的MCU。

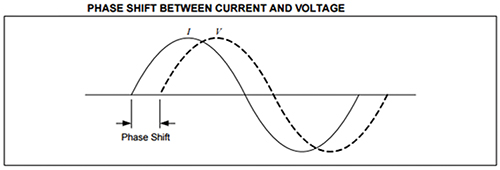

产品增强的另一个方案是提高公用事业电表的准确性。公用事业仪表中的能量测量精度取决于监测电压和电流信号之间的相位差的精度,以计算负载功率因数。测量两个信号之间相位差的最常用方法是比较两个信号的零交叉和外推相位角之间的时间间隔。为了准确估计相位差,采样率应足够高,以最大限度地减少外插误差,如高速ADC。当单个ADC需要采用时分复用方法对所有三个信号(电压,电流和中性信号)进行采样时,情况会变得更加复杂。在这种情况下,有效采样率要求增加了三倍。

图6:在公用事业仪表中测量相移以确定功率因数

可配置逻辑单元(CLC)等CIP通过扩展其实现硬件相位检测器的能力,有助于提高相位差测量的精度。具有输入捕捉(IC)外设的CLC可以测量相同频率的两个信号之间的相位差。 CIP的组合提供更好的分辨率并提供超前/滞后信息。这扩展了CLC使能增强功能,无需迁移到更昂贵,更高性能的MCU。

图7:相位检测器CIP有助于提高相位差测量的准确度

设计优化

嵌入式公司的差异化,系统级成本优化的目标不能受到影响。 PIC MCU通过各种功能实现了这一目标。

Microchip的PIC MCU与CIP一起,还包括集成模拟外设,如片内sigma-delta ADC,高速SAR ADC和集成运算放大器具有内置控制功能的芯片可在不需要CPU干预的情况下做出明智的决策。这些集成的模拟模块无需创建多芯片外部组件设计。集成的单芯片解决方案显着降低了系统级成本,节省了PCB空间,提供了更好的优化。该解决方案占地面积小,甚至可以满足空间受限应用(如可穿戴设备和传感器应用)的要求。

此外,片上CIP有助于实现多个扩展应用并卸载许多应用。来自CPU的确定性例程。因此,使用CIP的应用程序实现需要较少的处理器资源,如带宽,闪存和RAM。通过从CPU中移除负载,CIP可以在没有昂贵的多核MCU的情况下实现多个并行进程。作为硬件模块的CIP对刺激响应更快,并以更高的吞吐量实现目标功能。 CIP的所有这些属性减少了迁移到更高内存,更高处理能力的MCU的需求,并优化了设计成本。

结论

随着Microchip专注于创新,PIC MCU不断发展更好地满足客户现在和未来的需求。目标不仅是解决未来嵌入式系统的技术要求,还要解决整体业务挑战。 PIC单片机中的核心独立外设解决了嵌入式系统中的新兴需求和挑战,并为开发人员提供了创建突破性应用的灵活性。

-

汽车嵌入式系统的发展如何?2019-08-02 0

-

如何开发基于OSEK/VDX平台的汽车嵌入式系统?2019-11-01 0

-

嵌入式系统11个必须了解的知识2020-06-16 0

-

如何采用FPGA提高广播应用的集成度?2021-04-29 0

-

嵌入式控制系统的ARM处理器概述2021-10-27 0

-

嵌入式MCU与MPU的误区有哪些2021-11-03 0

-

嵌入式系统中的MCU有何功能2021-11-03 0

-

GX3000 高集成度的数字电视解码系统芯片2008-09-24 1035

-

嵌入式系统电源的设计与调试2009-03-29 592

-

实现嵌入式系统集成射频:ZigBee的设计考虑因素2012-11-13 1220

-

集成度是什么意思_集成度的概念2017-11-10 17883

-

基于SoPC的FPGA集成嵌入式系统设计2017-11-23 1490

-

基于SoPC的嵌入式系统设计方法阐述2020-01-25 1661

-

DSP与MCU在嵌入式系统中的应用2021-07-30 736

-

嵌入式控制系统的ARM处理器2021-10-20 841

全部0条评论

快来发表一下你的评论吧 !