RISC-V究竟有何不同之处?RISC-V的生态现状

描述

壹. RISC-V的简单介绍

RISC-V(念做 Risk-Five)是一种起源于UC Berkeley大学,具有High Quality(高质量)、No license fee(无授权费)、No Royalty(无权利金)等主要特点的RISC ISA(指令集架构标准)。

RISC-V标准是由非营利性组织RISC-V基金会维护。RISC-V ISA适用于从微控制器到超级计算机的各种计算体系。在现今的RISC-V业界已经有了很多商用及开源的CPU core,工业界及学术界都在迅速采用该指令集架构,更重要是获得越来越多高速成长且用户共享的软件生态支持。更有趣的是,RISC-V生态是一个不断演进的,开放,灵活共生的社区型“生命体”。

贰. RISC-V究竟有何不同之处

1、简洁

相较于其它商用的ISAs,RISC-V ISA要小很多

2、从零开始的设计

明确的分离了User及privileged ISA

具有避免对micro-architecture及技术依赖性的特征

3、为了扩展性及客制化而设计的模块化ISA

小的标准化基本ISA,在此基础上具有多种标准的扩展

用于大量opcode space的sparse和variable-length instruction encoding

4、稳定性

基本及标准扩展ISA是固定不变的

通过可选扩展而非更新ISA的方式来增加指令

5、通过社区进行设计

由领先的行业或学术专家以及软件开发者组成的社区进行设计

RISC-V的发展历程

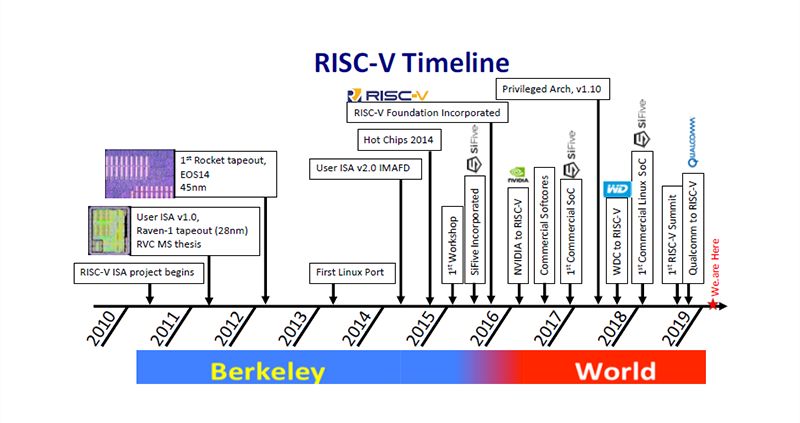

叁. RISC-V按照时间轴的演进路线

从2015年8月成立RISC-V基金会后,RISC-V ISA正式从UC Berkeley开始走向全世界,在世界范围内得到了极大的关注,下图为RISC-V的演进过程中重要的事件。

肆. RISC-V越来越流行的原因

工程技术人员有时候是“见木不见林”,RISC-V流行的趋势不是因为在有一些Benchmark方面有10%的提升或者在某一些应用情况下能节省30%的功耗。这个趋势的原因是新的商业模式的正在改变一切,新的模式是开发者先选择ISA,然后选择一个Processor的合作伙伴或者干脆选择自行开发,在此基础上可以自主选择是否添加自己的指令扩展甚至做功能裁剪。

Moore’s law(摩尔定律)正逐渐在失效,因为晶片的PPA(性能,功耗及面积)的提升,不再仅仅依靠芯片制造工艺的持续演进,从Intel,AMD等传统处理器提供商最近新产品的发布就能明显感觉得到。当前PPA的提升很多都是基于晶片架构的创新,各种AI处理器就是最好的例子, 当前的AI晶片的架构上有很多Coprocessor(协处理器),但似乎不需要在一颗芯片上有好多不同的ISA的Coprocessor(据统计,今天的SoC平均采用6种不同的ISA),如果采用RISC-V ISA的Coprocessor,工程人员可以自由实现不同特定应用的Coprocessor,添加不同的功能和标准扩展指令,而全栈软件依然可以在其上兼容运行。在ISA发展的历史上,也出现过开源的ISA,例如很多年前Sun公司开源了Sparc ISA,但是没有像现在RISC-V那么受到关注和应用,因为在那个时代,Moore’s law依然有效,市场还是没有对新的计算体系架构有那么多的需求。

在现实中,围绕着私有ISA所建立起来的软件生态,绝大部分都是ISA所有公司之外的开发者或者公司完成的,而不是拥有ISA的公司自己实现的。

一个优秀ISA的定义和不断优化不是靠一家公司的技术专家和经验积累能够完成的,通常需要巨量的工作和知识经验。对于一个开放,自由的ISA,会有很多公司甚至是个人参与标准的制定,设计和维护提升,而不会像Intel,AMD,ARM公司那样,只有他们公司的人员才能进行其私有ISA的设计和相关工作。即便是某一家公司设计出来了ISA,但是ISA的验证工作量是难以估量的,我们面对的现实状况是,在我们看来像Intel这样的大公司所采用的如此成熟的私有化ISA设计出的处理器,依然会有很多严重的ISA层面的漏洞,这是因为Intel一家公司和技术团队是无法完成所有的验证工作的,而且私有的ISA是很难得到开放社区共同的、透明的验证的。就像在开源软件的生态中,公司几个人能够利用社区中已经成熟的开源的软件设计或者模块,这样就能大大缩短设计开发周期和成本投入,真正得推动新应用的实现。

如果一个ISA是私有的话,人们无法保证它的延续性,它将和拥有它的公司所绑定,如果这家公司不再存在,那么大部分情况下这个私有化ISA也将随之失去延续性,Alpha以及VAX ISA就是一个非常好的例子,他们随着DEC公司的消亡而失去了延续性。

所以综上所述,我们看不出除了出于知识产权保护的原因之外,从技术的角度来讲没理由需要一个封闭的私有化的ISA,需要请各位注意的是,ISA和Processor IP是有区别,不能等同来看待。我们为什么需要用那么多不同的ISA,特别是那么多不同的私有化ISA呢?我们为什么不考虑使用同一个自由、开放的ISA用于所有的应用呢?我们认为这就是RISC-V ISA越来越流行的原因。

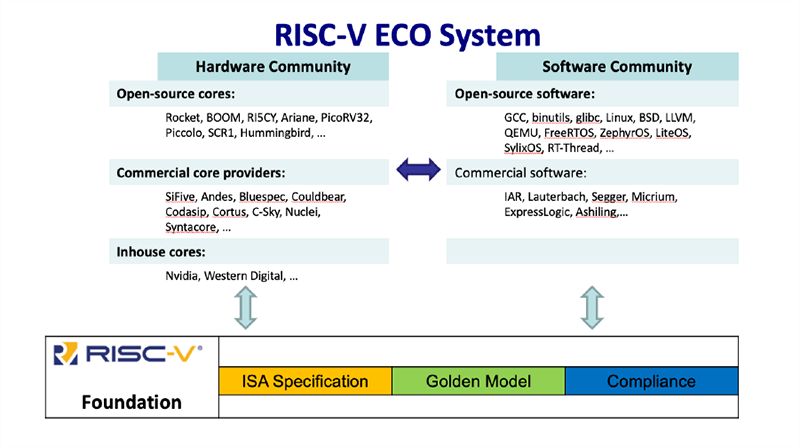

伍. RISC-V的生态现状

RISC-V的生态现状

陆. RISC-V ISA设计认证及扩展的过程

RISC-V的生态是如何通过基金会运营组织及社区讨论及共同开发的方式进行演进的,这也决定RISC-V ISA所获得的参与度必将飞速成长。以下,我们将通过RISC-V基金会运做方式进行分别说明。

RISC-V ISA标准的形成过程

RISC-V ISA 标准的形成总结来讲其实就是“大家一起来,不断迭代反复实践,最终一起标准化”,过程步骤如下:

定义需求

收集输入,举行会议,“白板级”参数设计,完成并公开发布稳定的标准初稿

根据标准初稿进行设计硬件实现

根据实施的硬件进行软件实现

进行软硬件的联合评估,可能需要重新回到以上第2步进行多次迭代

RISC-V技术研究小组决定推进该ISA标准的批准工作

RISC-V技术委员会将该ISA标准提交RISC-V基金会董事会

RISC-V基金会董事会进行投票批准

RISC-V社区设计按照批准后的标准进行实现,并进行合规性测试

最终完成ISA标准的替换

柒. Edge Computing(边缘计算)对处理器的需求

机器学习在当前的AI应用中快速的发展,系统也会增加更多智能功能。但是在云端的系统(例如数据中心)和边缘系统(例如IoT设备)对运算能力的需求是不同的,在云端可以采用大型高效的GPU来提供千万亿次的浮点运算能力,Google的TPU 3.0的单芯片的浮点运算能力远远超过100 Petaflops (一千万亿的浮点运算),用于深度学习或者进行推理。但是在边缘系统中,就很难采用功耗高的类似GPU或TPU的方案。系统开发人员必须要考虑采用效率更加高的解决方案,除了满足计算精度问题外,必须考虑实际应用场景对设备功耗,安装尺寸以及综合成本的问题。

将AI优势扩展至边缘设备,取代以云端为基础的资源,能够大幅降低功耗,同时缩短反应时间。 同时,本地数据储存和处理不仅提高安全性,更节省宝贵的带宽。通过将 AI整合至边缘设备中,即使在网络关闭以节省功耗的情况下,也能实现实时工作的智能功能。

低功耗解决方案可于网络边缘实现各类应用。例如,智能门铃可通过嵌入式AI功能自动进入待机模式,直到感应到有人出现;智能电视在没有观众观看的情况下自动关机;AI安防摄像头,只在出现入侵者时才发出警报,而不是因为自己家里或者邻居家里狗、猫等其他动物经过而出现在摄像头前的误报。搭载脸部识别的移动设备和平板电脑需要用户在进行脸部识别前唤醒装置。该解决方案让这一类设备能够在低功耗的状况下持续侦测人脸,再唤醒高功耗应用处理器执行深度识别任务。

在边缘设备的芯片中很多都是以神经网络(NN)硬件进行机器学期,这样就有需求为神经网络配置硬件加速器,RISC-V CPU中的ALU(算数逻辑单元) 就可以达到这样的需求。在这样的应用中,RISC-V体现出了非常精简高效的基础指令的特点,用最少的资源进行运算。在基础指令之上,开发人员通常采用各种标准的ISA Extension。例如采用Vector Extension ISA(向量扩展ISA)来增强RISC-V处理器,神经网络的矩阵运算的效率是通过从RISC-V ALU传输矩阵数据,再通过Vector Extension ISA减少甚至消除循环,memory load store(内存存取)以及address mapping(地址映射)产生的成本等方法来提升的。

捌. Edge Computing中至关重要的Security问题

Security对于边缘计算而言至关重要。那么RISC-V能否为Edge Computing提供可靠安全的整体方案?一个安全的RISC-V系统究竟有哪一些组件?还有哪一些新的安全技术?

当前RISC-V的体系中有哪一些安全组件

RISC-V ISA中有3种模式,分别为User(用户), Supervisor(管理员)以及 Machine(机器) 模式。

PMP(Physical Memory Protection) ,采用基础加边界的方案,没有转换,除非系统重置,否则禁止所有的访问,包括所有模式下程序对锁定memory区域的访问。

有2个保护边界,第一个为在Supervisor和User模式之间具有保护,第二个为PMPs (Physical memory protection) 机制保护所有的访问。

地址转换和保护,是基于标准页面的方案。

RISC-V的一些新的安全技术

传统的计算的安全性不够,因为几乎所有的程序都能获取到程序代码和数据,编译器和连接器将源码模块合并成单个二进制文件;各个功能模块(如Stack,Heap,Buffers)通过共享存储单元来通信;任何bit的源码都能得到任何bit的数据;任何一个错误指令能够瘫痪整个系统(如DOS)。

而RISC-V的Security Technical Group(安全技术组)中的成员 HEX Five公司,他们提出了一个更好的方法,也就是Multi-domain Trusted Execution Environment(多区域信任执行环境),该技术也是基于RISC-V标准扩展指令。在2018年,Hex Five先后宣布完成了基于集成SiFive RISC-V CPU以及Andes RISC-V CPU的晶片开发了类似ARM TrustZone的Trusted Execution Environment。

玖. RISC-V在Edge Computing中的一些应用案例

Canaan发布的Kendryte K210芯片

Kendryte K210芯片是一个非常典型的RISC-V应用于Edge Computing的案例。其应用包括:目标检测,目标识别,声源定位,声场成像,语音识别。该SoC晶片的主要组成模块为:

RISC-V CPU:双核64bit RISC-V处理器,提供了高性能,高带宽,高吞吐能力

KPU:神经网络加速单元,达到1 TOPS 0.35W@400MHz

APU:音频处理器,支持8路麦克风阵列预处理流程

FFT:512点FFT加速,高吞吐能力,支持16位定点运算

FPU:高性能浮点运算处理单元,双精度浮点,单精度浮点加速

Kendryte K210芯片主要组成模组

图片来源:Canaan Creative

Kendryte K210借助RISC-V的开源生态,支持多种即时操作系统(RTOS),包括FreeRTOS,RT-Thread, XBoot, Zephyr, SylixOS等。

BITMAIN发布的Sophon BM1880芯片

BM1880是一个Coprocessor,在实际应用时需要和类似Camera SoC这样的Host进行连接,数据通过USB或者Ethernet进行传输,Edge Inference可以在BM1880上完成。应用场景主要是Camera(摄像头),Robot(机器人),Drone(无人机)。该SoC晶片的的主要组成模块为:

双核ARM A53处理器

单核64bit RISC-V处理器

16/32bit, 1866/3200MHz, DDR3/LPDDR3/DDR4/LPDDR4

TPU: 运算能力达到1 TOPS@INT8,Winograd convolution达到2 TOPS

On chip memory size:2MB

Video Decoder/Image Codec/VPP:支持2 ways 1080p@30fps H264 decode; JPEG Encode/Decode; Hardware video processing

Interface: Ethernet and USB3.0用于视频数据的传输

让我们来分析一下,BM1880使用的RISC-V core,采用了单核64bit CPU core,按照实际应用选择的ISA为RV64 IMAFDC, 最高频率达到1GHz,16KiB L1 I-Cache/16KiB L1 D-Cache, RISC-V CPU和VAD (Voice Automatic Detection)模块配合使用,提供很好的低功耗及VAD的硬件加速能力。我们进一步来分析,RISC-V的模块化,灵活配置的ISA究竟能够给BM1880带来什么好处。

选择了M extension ISA是因为,M extension提供了整数乘法及除法运算能力,能提供高性能的乘法及除法运算的硬件加速功能;

选择A extension是因为应用的软件以及操作系统需要CPU支持Atomic Operation(原子操作);

选择同时支持F及D extension是因为需要用到单精度及双精度浮点运算能力;

选择C extension是因为可以能够通过该压缩指令扩展,在编译器编译代码时得到更高的code density(代码密度)和更高的运行效率;

拾. 总结

RISC-V ISA在当前的行业应用中,主要是嵌入式应用为主,在嵌入式应用中,由以用于边缘计算设备为主,边缘设备的AI及Inference(推理)深度结合的设计架构,在未来很长一段时间内,都将是保持高增长的趋势,这是RISC-V技术与Edge Computing最好的结合点,我们可以预期在2019年RISC-V将Vector Extension ISA 标准批准通过后,有更多的Core以及软体出现,将更有利于边缘计算晶片PPA和灵活度的提升,一定将助力其更上一层楼。

-

rIsc-v的缺的是什么?2024-07-29 0

-

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!2024-08-26 0

-

科普RISC-V生态架构(认识RISC-V)2020-08-02 0

-

RISC-V 生态架构浅析2021-06-18 0

-

分析RISC-V架构的不同之处2021-07-26 0

-

【RISC-V专题】芯昇科技RISC-V生态开发板首发试用2022-04-14 0

-

赛昉科技成立RISC-V Multimedia SIG,推动openKylin on RISC-V生态发展2023-04-03 0

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 3182

-

RISC-V中国峰会:RISC-V产业及生态发展2021-06-22 2967

-

RISC-V有什么软件生态,RISC-V IP在芯片中的应用2021-06-22 4135

-

如何建设RISC-V软件生态?2021-06-23 3290

-

RISC-V学习笔记【1】RISC-V概述2022-11-24 2632

-

openEuler加入RISC-V Landscape2023-03-13 1337

-

RISC-V和RISC-V AI的未来(特邀讲座)2023-07-14 496

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 376

全部0条评论

快来发表一下你的评论吧 !