原理图PCB设计时认真看官网Checklist

电子说

1.3w人已加入

描述

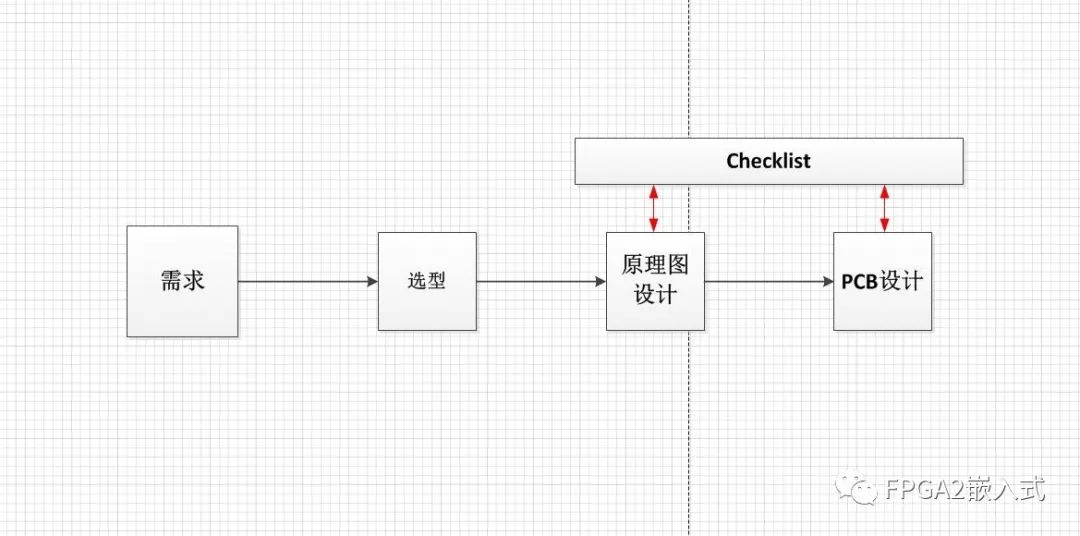

做项目过程中,器件选型确定后开始原理图PCB设计,这其中就包括FPGA的原理图PCB设计,而最终制版会错大多是因为原理图设计时的低级失误造成(之前就有项目遇到过FALSH配置专用引脚随意分配导致无法正常从FLASH中加载程序),特别是刚开始接触一个新的FPGA平台时,第一次打板常会出现一些问题(飞线、配置失败等),多人仔细检查会大概率一次打板成功。

一般我们在官网可以下载对应的数据手册,然后根据数据手册设计检查原理图PCB:电源、配置、LVDS等,设计完成后自己和同事检查错误,一不小心就会出错,而且大多是低级错误和失误。

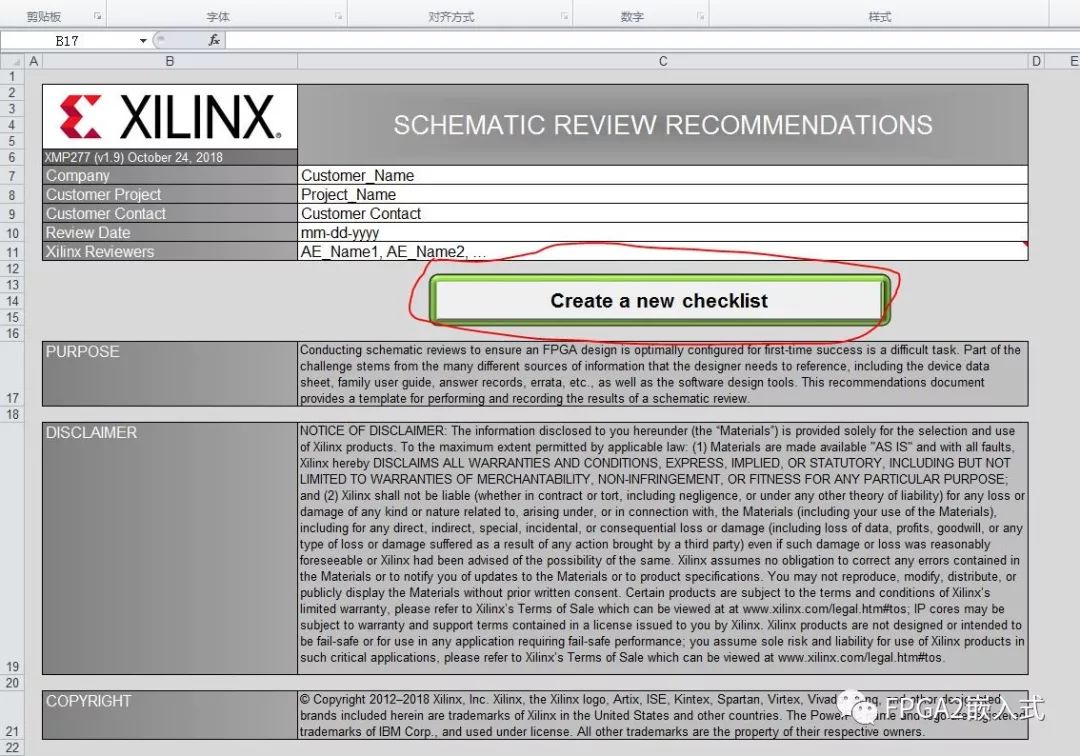

其实,可以通过FPGA官网都对应的Checklist来设计及检查,这样可以大大减少错误和失误,Xilinx有类似XPE(FPGA(Altera/Xilinx/Actel)如何估算分析功耗)的EXCEL形式的Checklist,下面举例Xilinx 7series FPGAs的Checklist操作:

Step1:点击新建一个Checklist

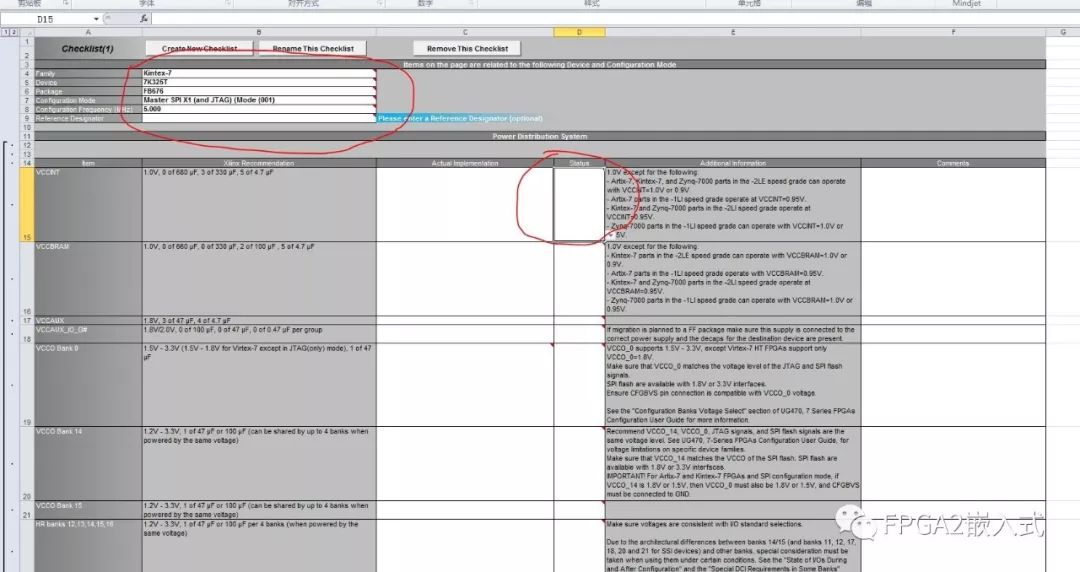

Step2:输入对应的FPGA型号等参数,输入完成后就可Check电源部分

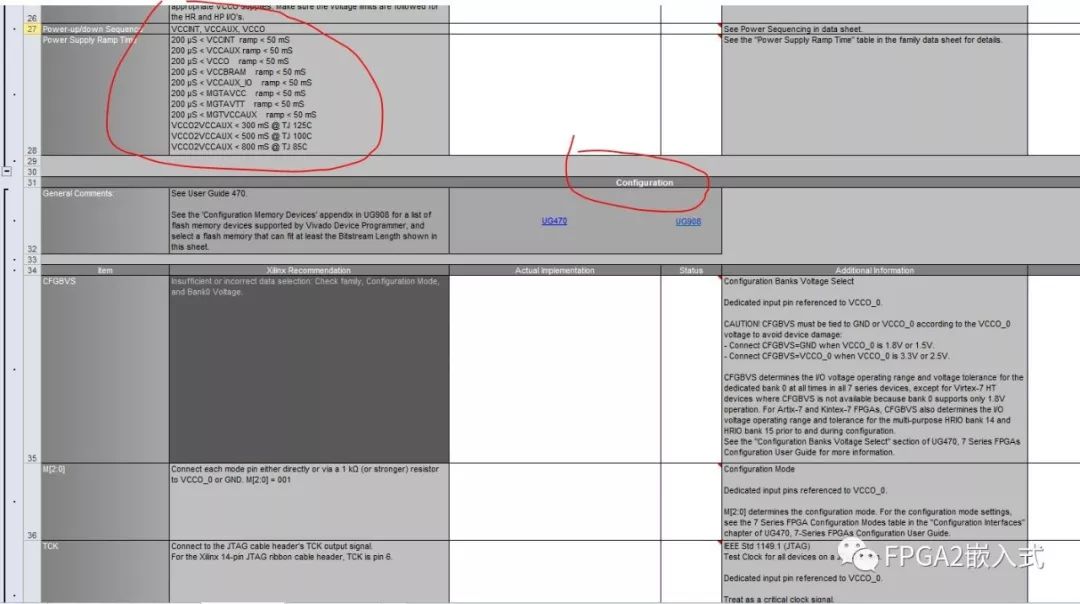

Step3:Check配置部分

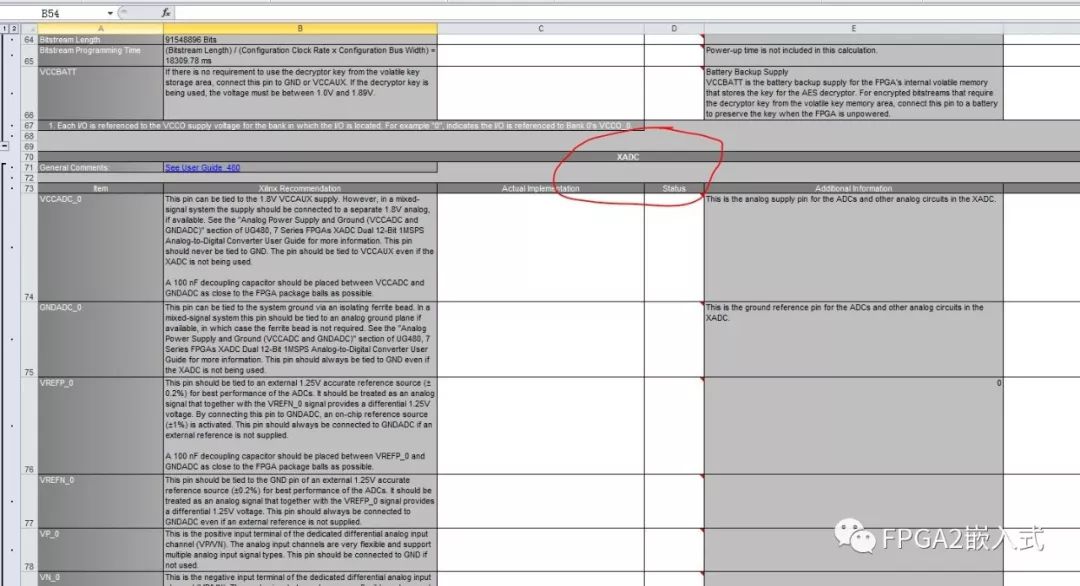

Step4:Check XADC模拟部分

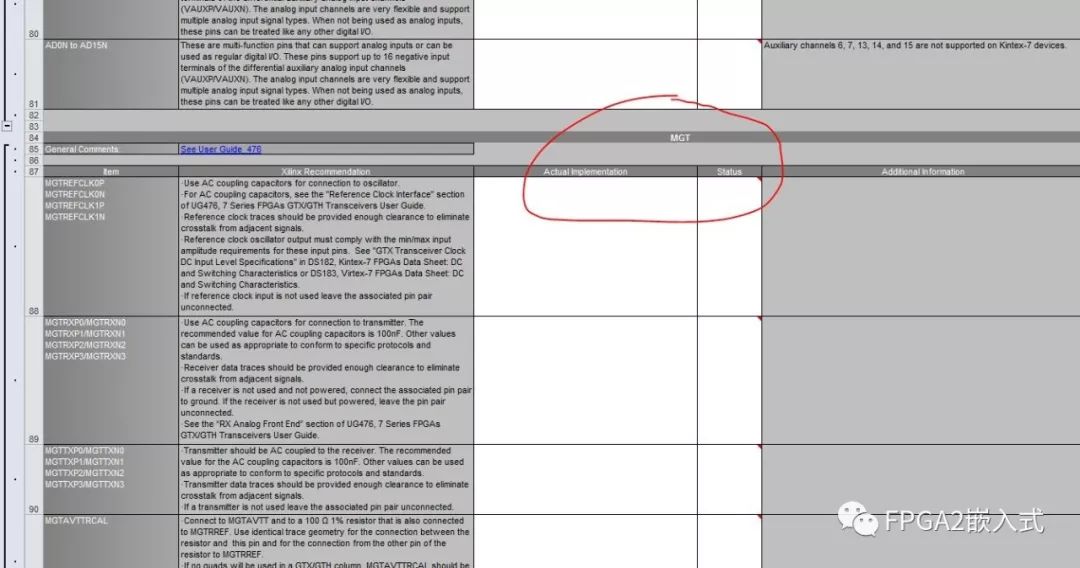

Step5:Check MGT高速接口部分

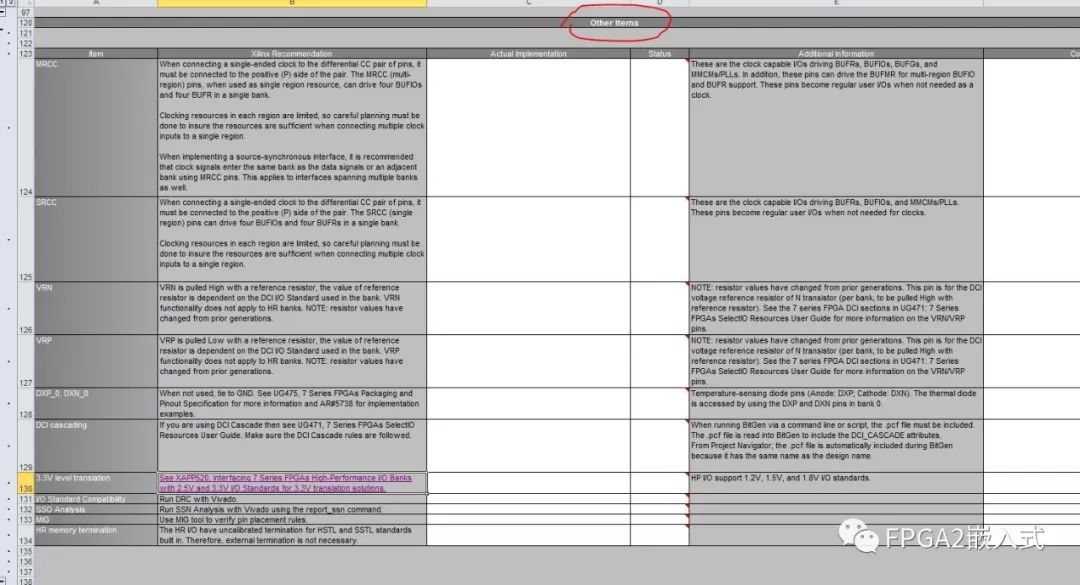

Step6:Check 其它部分,包括时钟、MIG等

注意:1. 原理图PCB设计完成后需要再仔细Checklist下,因为PCB设计时经常由于布线等原因可能会重新随意分配了专用引脚(配置引脚、JTAG、时钟、差分对等);2. 原理图有checklist,其它设计也会有,多去官网看看。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

orcad绘制原理图与放置新元器件#pcb设计凡亿_PCB 2021-07-20

-

capture平台原理图环境设置#pcb设计凡亿_PCB 2021-07-20

-

【转】PCB设计基础知识 | PCB设计流程详解2017-02-22 0

-

FPGA原理图PCB设计时认真看官网Checklist2019-05-08 0

-

PCB威廉希尔官方网站 原理图checklist资料下载2021-03-29 941

-

3步搞定PCB设计checklist资料下载2021-04-15 635

-

EDA工具CADENCE原理图与PCB设计说明2021-07-15 4201

-

ALTIUM DESIGNER原理图与PCB设计资料下载022021-10-08 1084

-

ALTIUM DESIGNER原理图与PCB设计资料下载032021-10-08 1029

-

PCB设计的checklist,简单3步就搞定了!2022-02-09 597

-

Tsi310 原理图 Review Checklist2023-04-19 213

-

PCB原理图与PCB设计文件的区别2023-08-01 4979

-

Allegro原理图与PCB设计.zip2022-12-30 536

-

Altium_Designer_原理图与PCB设计 .zip2022-12-30 749

-

原理图及PCB Checklist大放送~2024-07-24 1075

全部0条评论

快来发表一下你的评论吧 !