SRAM存储器的并行接口和串行接口对比

接口/总线/驱动

描述

外置SRAM通常配有一个并行接口。考虑到大多数基于SRAM的应用的存储器要求,选择并行接口并不令人惊讶。对于已经(和仍在)使用SRAM的高性能(主要是缓存)应用而言,与串行接口相比,并行接口拥有明显优势。但这种情况似乎即将改变。

尽管能够提供高于串行接口的性能,但并行接口也有劣势。其中最明显的是,无论是从威廉希尔官方网站 板空间还是从引脚数要求的角度而言,并行接口的尺寸都远远大于串行接口。例如,一个简单的4Mb SRAM最多可能需要43个引脚才能与一个控制器相连。在使用一个4Mb SRAM时,我们的要求可能如下:

A. 最多存储256K的16位字

B. 最多存储512K的8位字

对于“A”,我们需要使用18个引脚来选择一个地址(因为存在2^18种可能),并另需使用16个引脚来进行实际上的数据输入/输出。除了这34个引脚之外,使能我们还需要更多连接来实现使能芯片、使能使能输出、使能使能写入等功能。对于“B”,我们需要的引脚相对较少:19个引脚用于选择地址,8个用于输入/输入。但开销(使能芯片、使能写入等)保持不变。对于一个容纳这些引脚的封装而言,仅从面积的角度而言,其尺寸已经很大。

一旦地址被选择后,一个字(或其倍数)将被快速读取或写入。对于需要较高存取速度的应用而言,这些SRAM是理想选择。在使用SRAM的大多数常见系统中,这种优势使得“太多引脚”的劣势变得可以忽略不计,这些系统的控制器需要执行极其复杂的功能,因此需要一个很大的缓存。过去,这些控制器通常较大,配有足够的接口引脚。控制器较小、引脚较少的应用不得不凑合使用嵌入式RAM。

在一个配备串行接口的存储器芯片中,位元是被串行存取的(一次存取1位到4位)。与并行接口相比,这使得串行接口更加简单和小巧,但通常吞吐量也更小。这个劣势让大多数使用SRAM的系统弃用了串行接口。尽管如此,新一代应用的存储器要求有可能很快打破引脚数和速度之间的平衡。

行业发展趋势

处理器日趋强大,尺寸越来越小。更加强大的处理器需要缓存进行相应的改进。但与此同时,每一个新的工艺节点让增加嵌入式缓存变得越来越困难。SRAM拥有一个6晶体管架构(逻辑区通常包含4个晶体管/单元)。这意味着,随着工艺节点不断缩小,每平方厘米上的晶体管的数量将会非常多。这种极高的晶体管密度会造成很多问题,其中包括:

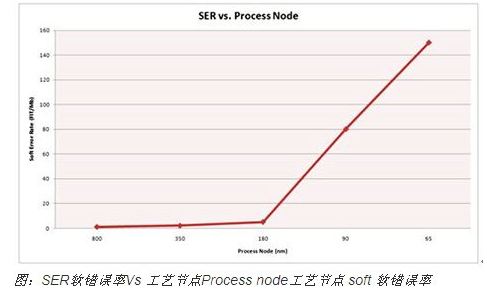

图:SER软错误率Vs 工艺节点Process node工艺节点 soft 软错误率

更易出现软错误: 工艺节点从130nm缩小到22nm后,软错误率预计将增加7倍。

更低的成品率: 由于位单元随着晶体管密度的增加而缩小,SRAM区域更容易因工艺变化出现缺陷。这些缺陷将降低处理器芯片的总成品率。

更高的功耗: 如果SRAM的位单元必需与逻辑位单元的大小相同,那么SRAM的晶体管就必须小于逻辑晶体管。较小的晶体管会导致泄露电流升高,从而增加待机功耗。

另一个技术发展趋势是可穿戴电子产品的出现。对于智能手表、健身手环等可穿戴设备而言,尺寸和功耗是关键因素。由于威廉希尔官方网站 板的空间有限,MCU必须做得很小,而且必须能够使用便携式电池提供的微小电量运行。

片上缓存难以满足上述要求。未来的可穿戴设备将会拥有更多功能。因此,片上缓存将无法满足要求,对外置缓存的需求将会升高。在所有存储器选项中,SRAM最适合被用作外置缓存,因为它们的待机电流小于DRAM,存取速度高于DRAM和闪存。

串行接口的崛起

当我们观察电子产品近些年的演进历程时,我们会注意到一个重要趋势:每一代设备的尺寸越来越小,而性能却保持不变甚至升高。这种缩小现象可以归因于以下事实:威廉希尔官方网站 板上的每个组件都在变小,从而造成了这样的总体效果。早在1965年,高登?摩尔就在他著名的摩尔定律中预测了威廉希尔官方网站 的缩小趋势。但是,这个缩小趋势并未发生在所有类型的威廉希尔官方网站 中。例如,逻辑威廉希尔官方网站 比SRAM威廉希尔官方网站 缩小了很多倍。这造成了一个棘手的问题:即嵌入式SRAM开始占据90%的控制器空间。嵌入式SRAM的有限缩小还阻止了控制器以相应于逻辑区域的程度缩小。因此,成本(与晶粒面积成正比)的降幅并未达到应有的程度。由于处理器/控制器的核心功能由逻辑区执行,将嵌入式SRAM移出芯片并以外置SRAM取而代之开始具有意义。

此外,可穿戴和物联网设备的迅猛发展也是这一趋势的推动因素。与其它任何设计要求相比,这些设备最注重小巧的设计。因此,最小的MCU适合此类威廉希尔官方网站 板,鉴于上述原因,这个“最小的MCU”极有可能不搭载一个嵌入式缓存。同样,它也可能没有太多的引脚。

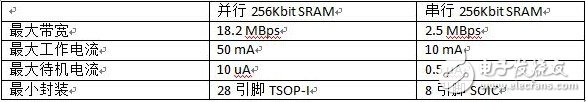

所有这些发展趋势都指向一个要求:一个小巧、能够只扮演缓存的角色、并能使用最小数量的引脚相连的外置SRAM。串行SRAM就是专为满足这个要求而量身定做的。存储器在高速性能并非最重要因素的其它存储器(DRAM、闪存等)中,串行接口已经取代了并行接口。由于存在需要SRAM的应用,串行SRAM在SRAM市场中一直处于小众地位。在空间非常有限的特定应用中,它们一直是低功耗、小尺寸替代方案。目前,在峰值时钟速率为20MHz(10MB/s带宽)条件下,串行SRAM最大容量为1Mbit。相比之下,并行SRAM的带宽高达250MB/s,并支持最大64Mbit的容量。下表对比了一个通用型256Kbit并行SRAM和一个256Kbit串行SRAM。

由于所需驱动的引脚数较少,而且速度更低,串行接口存储器通常比并行接口存储器消耗更少的电能,而且其最大的好处在于较小的尺寸-无论是从设备尺寸还是从引脚数的角度而言。最小的并行SRAM封装是24球BGA,而串行SRAM提供8引脚SOIC封装。但必需注意的是,WL-CSP是最小封装,很多并行和串行存储器厂商支持CSP封装。市场上的并行SRAM胜过串行SRAM的地方是性能-尤其是在存取时间上。凭借宽得多的总线,并行SRAM能够最大支持200MBps的吞吐量,而大多数得到广泛使用的串行SRAM最多只支持40MBps。

如上表所示,存储器存储器串行接口存储器在性能方面落后并行接口存储器。由于数据流是顺序的,它们不能提供相同的吞吐量。因此,串行存储器存储器最适合那些注重尺寸和功耗胜过存取时间的便携式设备,如手持设备和可穿戴设备。

未来将会怎样

在物联网和可穿戴设备兴盛之前,串行 SRAM 的利润还不足以吸引主流SRAM厂商的注意力。实际上,主要的串行SRAM厂商就是Microchip和On-semi。对于这两家公司而言,SRAM并非它们的核心业务,在营收中的占比也很小。另一方面,静态RAM领域的市场领袖(如赛普拉斯、ISSI和Renesas)一直以来只专注于并行SRAM。

这种情况可能会发生改变。随着串行SRAM的商机不断增多,我们很快就会看到传统的SRAM厂商将进军串行SRAM领域。未来几年,串行SRAM的产品路线图注定会出现(因为这些公司拥有积极推动SRAM技术不断进步的悠久历史)。容量和带宽将是两大推动力。静态RAM领域的市场领袖赛普拉斯已经将串行SRAM纳入到其异步SRAM产品路线图中。事实上,赛普拉斯和Spansion的合并意味着,赛普拉斯已经掌握了最新的Hyperbus技术(由Spansion首创),该技术能够通过一个串行接口提供高达400MBps的吞吐量,因此,在这方面完胜DRAM。随着主流SRAM厂商进入该市场,开发人员不久将会获得最先进的串行SRAM。

大吞吐量、小巧的串行接口SRAM给我们带来了无限的可能性。它最终有可能成为众多威廉希尔官方网站 板上当代嵌入式SRAM和并行SRAM的全财产继承者。

-

usb是串行接口吗_串行接口和并行接口有什么区别2018-03-26 67968

-

什么是串行接口,什么是并行接口以及他们的区别2012-10-25 0

-

未来谁主沉浮:串行和并行接口SRAM对比2016-10-29 0

-

串行和并行接口SRAM有什么不同?未来将会怎样发展?2021-04-19 0

-

串行接口为啥比并行接口快?你明白吗2021-05-18 0

-

串行和并行接口SRAM对比分析,看完你就懂了2021-05-19 0

-

串行接口与并行接口相比有何优点2022-02-15 0

-

并行接口2009-03-25 1852

-

并行接口铁电存储器FM1808及其应用2006-03-24 1818

-

PC 并行接口定义2009-02-12 1015

-

串行和并行接口SRAM对比,谁会是未来主流?2015-11-06 1787

-

关于串行和并行接口SRAM的对比分析2019-08-26 4686

-

串行接口和并行接口有什么不同2022-06-21 10305

-

收藏起来!串行接口串行接口和并行接口的区别-科兰2023-06-05 2048

-

串行接口与并行接口的区别2024-08-25 3736

全部0条评论

快来发表一下你的评论吧 !