28335通过74lVC164245电平转换芯片链接三片AD7606,并口运行

ad7606配置如下:

Vdrive —— 5V

输入口:

CS 三片AD7606共用

CONVST 三片AD7606共用

RD 分开

RESET下拉

STBY上拉

REF下拉

PAR下拉

OS下拉

输出口:

BUSY下拉

DB0-DB15 三片AD7606连接到74lVC164245

现在我发现只能其中一片AD7606单独运行,继续焊接任一片后就不能工作?控制pin脚RESET、CONVST、CS、RD、波形也正常。

2018-7-24 08:55:57

/CS 不能共用,否则总线冲突,三片AD7606要分时读数据。

/CS 不能共用,否则总线冲突,三片AD7606要分时读数据。

举报

举报

2018-7-24 09:09:20

三片AD7606的片选CS信号是同时给定,即相互一致的,但是RD/SCK 信号是分开的,即读信号是分开的。

F28335

检测到BUSY

置零之后,控制读的时序,FRD

控制第一块AD7606

读操作,其他AD7606

读引脚置高;共八个正波,对应采样八个通道读取时间。

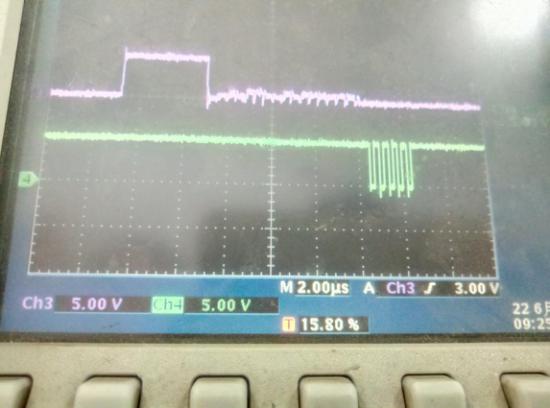

如下图,

如下图,SRD

控制第二块AD7606

读操作,其他AD7606

读引脚置高;共八个正波,对应采样八个通道读取时间。

如下图,

如下图,TRD

控制第三块AD7606

读操作,其他AD7606

读引脚置高;共五个正波,对应采样五个通道读取时间。

1. MCU

主控制器用的是德州仪器的F28335

,3.3V工作电平。数据采集传输利用16位并口总线,信号输入:MADBSY;信号输出:MADRST,MADCVT,MADCS,读控制引脚AREADY,AFRD,ASRD,ATRD

2.

电平转换芯片

利用两片74LVC164245

进行电平转换。第一片74LVC164245

,将DB0

~ DB15

并口数据从AD7606

传给F28335

;另一片74LVC164245

,控制信号ADRESET

、CONVST

、CS

、ADCS

3.

逻辑芯片

逻辑控制芯片(或门)两片:74HCT32D

;

AFRD

、AREADY

进行“

或”

操作,结果送至第一片AD7606

的RD/SCLK

引脚;

ASRD

、AREADY

进行“

或”

操作,结果送至第二片AD7606

的RD/SCLK

引脚;

ATRD

、AREADY

进行“

或”

操作,结果送至第三片AD7606

的RD/SCLK

引脚;

三片AD7606

的BUSY

引脚进行“

或”

操作,结果送至F28335

;

4.

数据采集AD7606

数据采集

数据采集系统采用三片AD7606BSTZ

,第一片AD7607

采集8

个模拟量;第二片AD7607

采集8

个模拟量;第三片AD7607

采集5

个模拟量,多余的三个模拟量短接到AGND

。

- (1)REST信号,三片AD7606共用,设计的是一上电就硬件复位,没采用过采样,转换开始后,一旦BUSY为低开始读取数据,通过I/O口来模仿时序读取数据。

- (2)CONVST信号,三片AD7606共用,采用CONVESTA和CONVESTB连在一起,三片同时转化;

- (3)BUSY信号,三片AD7606的BUSY引脚进行“或”操作,结果送至F28335,BUSY为低后,F28335给出CS和RD控制信号;

- (4)CS片选信号, 三片AD7606共用,三片同时选定;

- (5)RD信号,F28335通过逻辑控制芯片74HCT32D(或门)分别给出FRD、SRD、TRD信号

FRD

控制第一块AD7606

读操作

SRD

控制第二块AD7606

读操作

TRD

控制第三块AD7606

读操作

二、软件控制

[size=10.5000pt]软件启动初始化顺序:

[size=10.5000pt]1. [size=10.5000pt]AD复位信号先清零再置位并延时5个周期,最后清零

[size=10.5000pt]2. [size=10.5000pt]AD启动转换信号清零

[size=10.5000pt]3. [size=10.5000pt]BUSY初始化

[size=10.5000pt]4. [size=10.5000pt]采样CS初始化

[size=10.5000pt]软件工作时序

- [size=10.5000pt]1. [size=10.5000pt]AD启动转换信号先置零并延时50个周期,再置位并延时10个周期

- [size=10.5000pt]2. [size=10.5000pt]判断busy信号

- [size=10.5000pt]3. [size=10.5000pt]当BUSY信号为0时,开始依次读取三块AD的数据

[size=10.5000pt]每条指令的周期为6.67ns,采样周期为156.25μs

三片AD7606的片选CS信号是同时给定,即相互一致的,但是RD/SCK 信号是分开的,即读信号是分开的。

F28335

检测到BUSY

置零之后,控制读的时序,FRD

控制第一块AD7606

读操作,其他AD7606

读引脚置高;共八个正波,对应采样八个通道读取时间。

如下图,

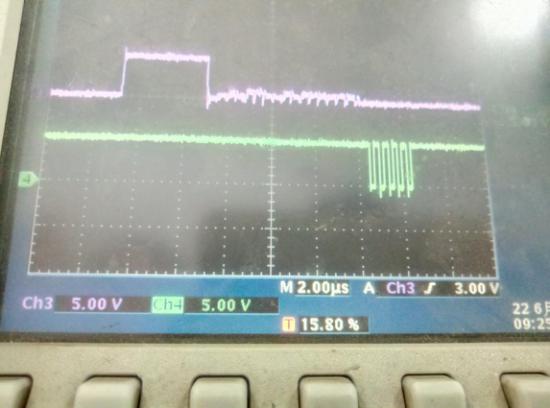

如下图,SRD

控制第二块AD7606

读操作,其他AD7606

读引脚置高;共八个正波,对应采样八个通道读取时间。

如下图,

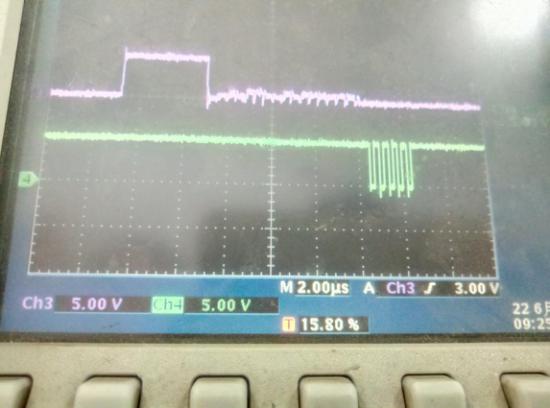

如下图,TRD

控制第三块AD7606

读操作,其他AD7606

读引脚置高;共五个正波,对应采样五个通道读取时间。

1. MCU

主控制器用的是德州仪器的F28335

,3.3V工作电平。数据采集传输利用16位并口总线,信号输入:MADBSY;信号输出:MADRST,MADCVT,MADCS,读控制引脚AREADY,AFRD,ASRD,ATRD

2.

电平转换芯片

利用两片74LVC164245

进行电平转换。第一片74LVC164245

,将DB0

~ DB15

并口数据从AD7606

传给F28335

;另一片74LVC164245

,控制信号ADRESET

、CONVST

、CS

、ADCS

3.

逻辑芯片

逻辑控制芯片(或门)两片:74HCT32D

;

AFRD

、AREADY

进行“

或”

操作,结果送至第一片AD7606

的RD/SCLK

引脚;

ASRD

、AREADY

进行“

或”

操作,结果送至第二片AD7606

的RD/SCLK

引脚;

ATRD

、AREADY

进行“

或”

操作,结果送至第三片AD7606

的RD/SCLK

引脚;

三片AD7606

的BUSY

引脚进行“

或”

操作,结果送至F28335

;

4.

数据采集AD7606

数据采集

数据采集系统采用三片AD7606BSTZ

,第一片AD7607

采集8

个模拟量;第二片AD7607

采集8

个模拟量;第三片AD7607

采集5

个模拟量,多余的三个模拟量短接到AGND

。

- (1)REST信号,三片AD7606共用,设计的是一上电就硬件复位,没采用过采样,转换开始后,一旦BUSY为低开始读取数据,通过I/O口来模仿时序读取数据。

- (2)CONVST信号,三片AD7606共用,采用CONVESTA和CONVESTB连在一起,三片同时转化;

- (3)BUSY信号,三片AD7606的BUSY引脚进行“或”操作,结果送至F28335,BUSY为低后,F28335给出CS和RD控制信号;

- (4)CS片选信号, 三片AD7606共用,三片同时选定;

- (5)RD信号,F28335通过逻辑控制芯片74HCT32D(或门)分别给出FRD、SRD、TRD信号

FRD

控制第一块AD7606

读操作

SRD

控制第二块AD7606

读操作

TRD

控制第三块AD7606

读操作

二、软件控制

[size=10.5000pt]软件启动初始化顺序:

[size=10.5000pt]1. [size=10.5000pt]AD复位信号先清零再置位并延时5个周期,最后清零

[size=10.5000pt]2. [size=10.5000pt]AD启动转换信号清零

[size=10.5000pt]3. [size=10.5000pt]BUSY初始化

[size=10.5000pt]4. [size=10.5000pt]采样CS初始化

[size=10.5000pt]软件工作时序

- [size=10.5000pt]1. [size=10.5000pt]AD启动转换信号先置零并延时50个周期,再置位并延时10个周期

- [size=10.5000pt]2. [size=10.5000pt]判断busy信号

- [size=10.5000pt]3. [size=10.5000pt]当BUSY信号为0时,开始依次读取三块AD的数据

[size=10.5000pt]每条指令的周期为6.67ns,采样周期为156.25μs

1

1

举报

举报

举报

举报

举报

举报

1

1

举报

举报