你好:

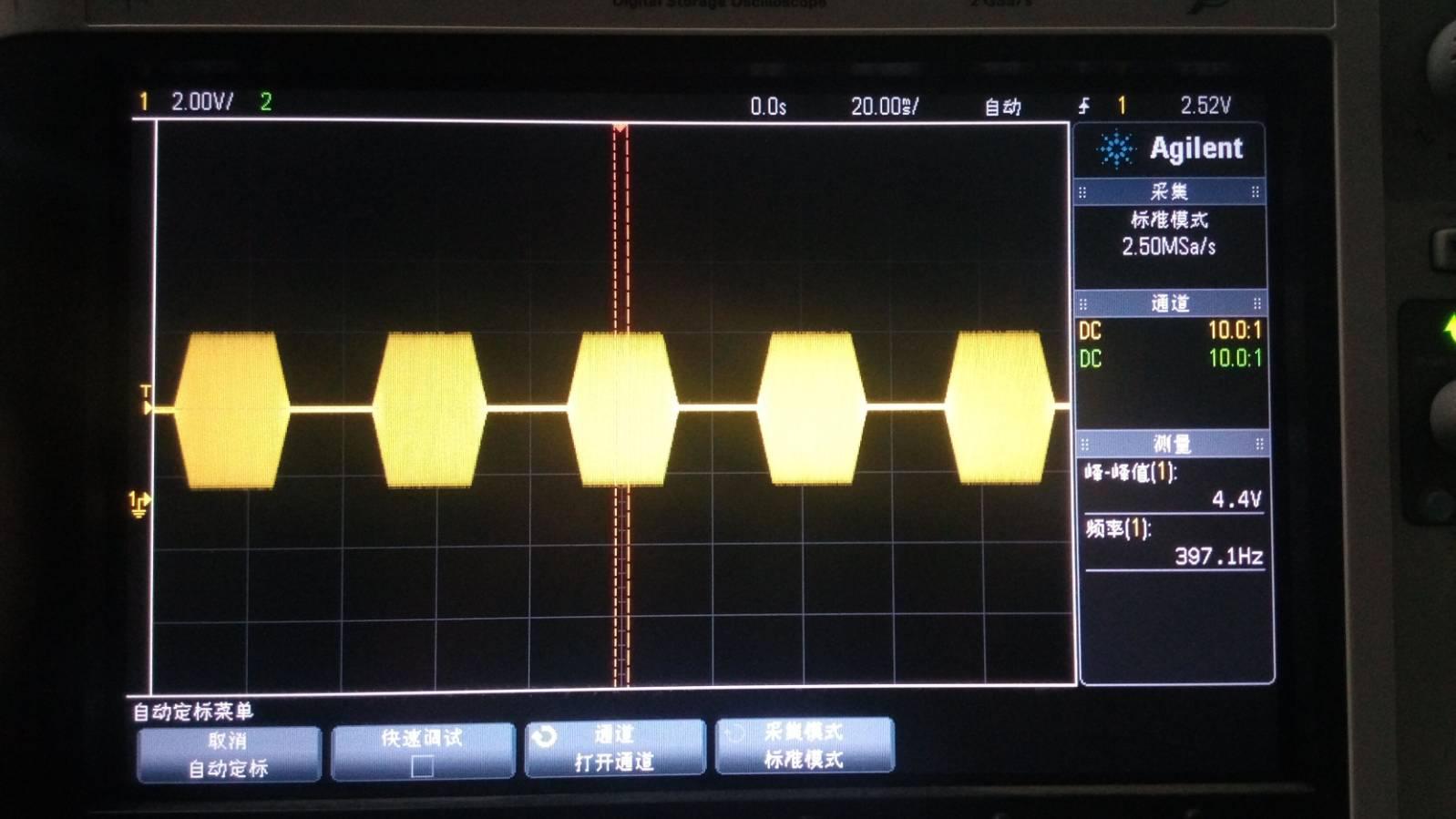

我们在配置AD9854工作在ASK模式下,梯形可以正常输出,

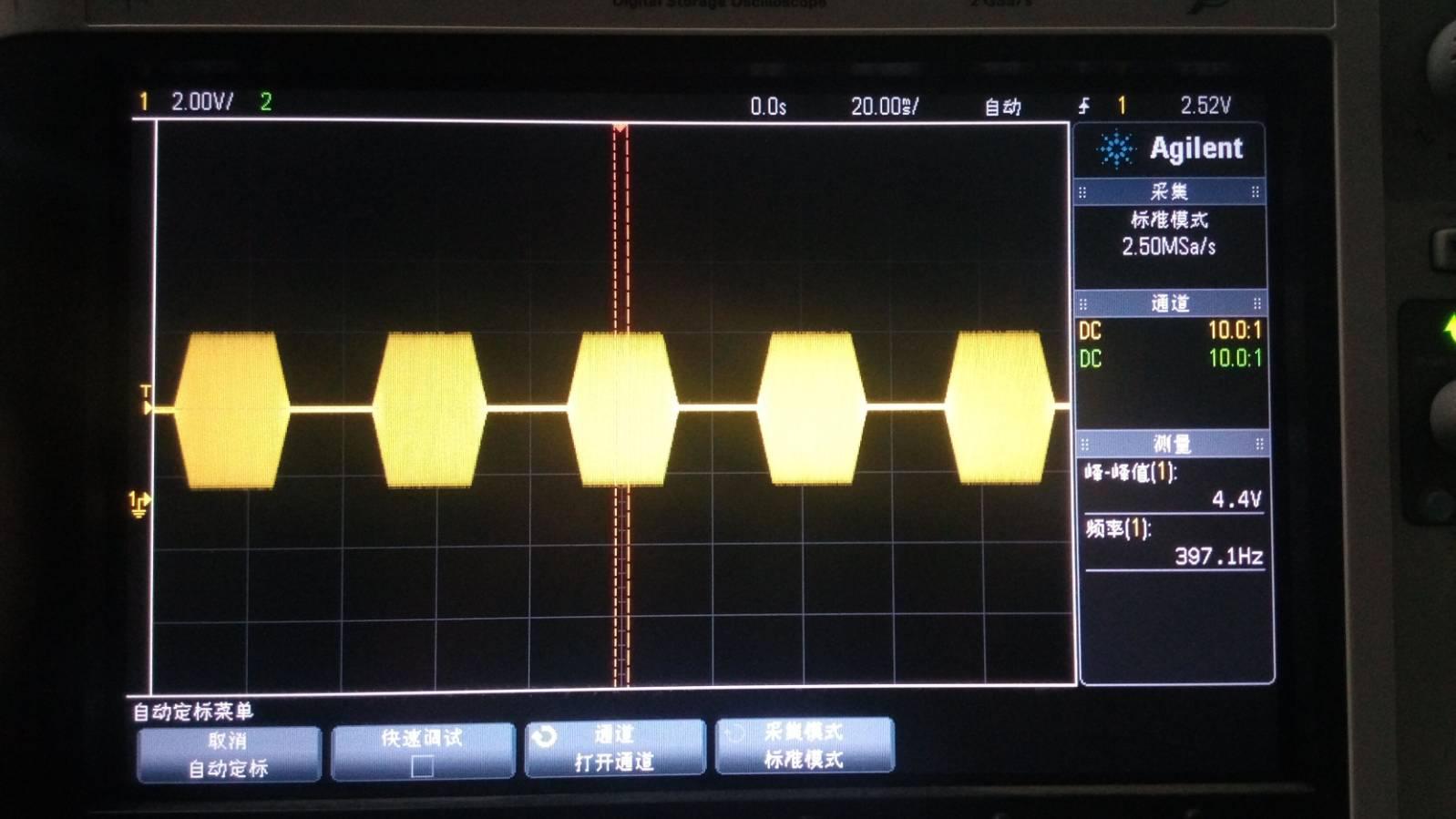

矩形输出不了,按程序配置后输出的是正弦波。

给你发的程序UD_CLK都是外部更新的,内部更新的程序我也做了,效果和这个一样。

我们是用FPGA配置的,代码使用verilog实现。

麻烦看哈我是那个寄存器配置的有问题或者那不对,非常感谢。。。。谢谢。。

always @(posedge CLK)

if(RST)

mst_rst_cnt <= 8'h00;

else if(mst_rst_cnt == 8'h13)

mst_rst_cnt <= 8'h13;

else

mst_rst_cnt <= mst_rst_cnt + 1'b1;

always@(posedge CLK)

if(RST)

mst_rst<=1'b0;

else if(mst_rst_cnt >= 8'h01 && mst_rst_cnt <= 8'h12)

mst_rst<=1'b1;

else

mst_rst<=1'b0;

always@(posedge CLK)

if(RST)

mst_rst_ok <= 1'b0;

else if(mst_rst_cnt > 8'h12)

mst_rst_ok <= 1'b1;

else;

// -----------------------------------------------------

reg [1:0] wrb_cnt;

always@(posedge CLK)

if(RST)

wrb_cnt <= 2'b00;

else if(ad_9854_init_ok)

wrb_cnt <= 2'b00;

else if(mst_rst_ok)

wrb_cnt <= wrb_cnt + 1'b1;

else;

assign wrb = wrb_cnt[1];

// ----------------------------------------------------

always@(posedge CLK)

if(RST)

ctrl_cnt <= 8'h0;

else if(mst_rst_ok)

if(ctrl_cnt == 8'd49)

ctrl_cnt <= 8'd49;

else if(wrb_cnt == 2'b00)

ctrl_cnt <= ctrl_cnt+ 1'b1;

else;

else;

always@(posedge CLK)

if(RST)

io_ud <= 1'b0;

else if(ctrl_cnt== 8'd40)

io_ud <= 1'b1;

else if(ctrl_cnt== 8'd48)

io_ud <= 1'b0;

else;

always@(posedge CLK)

if(RST)

ad_9854_init_ok <= 1'b0;

else if(ctrl_cnt== 8'd48)

ad_9854_init_ok <= 1'b1;

else;

// --------------- 输出 AD_FSK_BPSK_HOLD 信号--------------------------

// 0 --- FTW1; 1 --- FTW2;

always@(posedge CLK) // 25M

if(RST)

fsk_div_cnt <= 16'h0;

else if(ad_9854_init_ok)

if(fsk_div_cnt == SPEED_DELAY_CNT)

fsk_div_cnt <= 16'h0;

else

fsk_div_cnt <= fsk_div_cnt + 1'b1;

else

fsk_div_cnt <= 16'h0;

// 0 --- FTW1; 1 --- FTW2;

always@(posedge CLK)

if(RST)

need_mod_out <= 1'b1;

else if(fsk_div_cnt > SPEED_DELAY_DIVID2)

need_mod_out <= 1'b1;

else

need_mod_out <= 1'b0;

// -----------------------------------------------------------------------

///*

always@(posedge CLK)

if(RST)

state <= 20'h0;

else

state <= state + 1'b1;

assign ask_out_range = 16'h0FF0;

assign AD_SHAPEDK = state[19];

// -----------------------------------------------------------------------

// FSK F1 = 70.5M F2 = 69.5M

always@(posedge CLK)

if(RST)

address <=6'b00_0000;

else if(mst_rst_ok)

case(ctrl_cnt)

// ************** 写寄存器 ***********************

// FTW1

8'd2 : address <= 6'b00_0100; //0x04 FTW1_5

8'd3 : address <= 6'b00_0101; //0x05 FTW1_4

8'd4 : address <= 6'b00_0110; //0x06 FTW1_3

8'd5 : address <= 6'b00_0111; //0x07 FTW1_2

8'd6 : address <= 6'b00_1000; //0x08 FTW1_1

8'd7 : address <= 6'b00_1001; //0x09 FTW1_0

// 输出幅度乘法器

8'd8 : address <= 6'b10_0001; //0x21

8'd9 : address <= 6'b10_0010; //0x22

8'd10 : address <= 6'b10_0011; //0x23

8'd11 : address <= 6'b10_0100; //0x24

// 写控制寄存器

8'd14 : address <= 6'b01_1101; //0x1D

8'd15 : address <= 6'b01_1110; //0x1E 配置PLL时钟

8'd16 : address <= 6'b01_1111; //0x1F

8'd17 : address <= 6'b10_0000; //0x20

// 输出边沿变化率控制器

//8'd19 : address <= 6'b10_0101; //0x25

default:address <= 6'b00_0000;

endcase

else;

always@(posedge CLK)

if(RST)

data <=8'b1111_1011;

else if(mst_rst_ok)

case(ctrl_cnt)

// FTW1

8'd2 : data <= FTW1[47:40]; //0x04 FTW1_5

8'd3 : data <= FTW1[39:32]; //0x05 FTW1_4

8'd4 : data <= FTW1[31:24]; //0x06 FTW1_3

8'd5 : data <= FTW1[23:16]; //0x07 FTW1_2

8'd6 : data <= FTW1[15:8]; //0x08 FTW1_1

8'd7 : data <= FTW1[7:0]; //0x09 FTW1_0

// 输出幅度乘法器

8'd8 : data <= ask_out_range[15:8];//0x21

8'd9 : data <= ask_out_range[7:0]; //0x22

8'd10 : data <= 8'h0;//0x23

8'd11 : data <= 8'h0; //0x24

// 写控制寄存器 输出梯形的ASK调制模式

8'd14 : data <= 8'h10; //0x1D

8'd15 : data <= 8'h47; //0x1E 配置PLL时钟 280M

8'd16 : data <= 8'h00; //0x1F single tone 外部更新

8'd17 : data <= 8'h70; //0x20

// 输出边沿变化率控制器

//8'd19 : data <= 8'h03; //0x25

// OSK RAMP rate控制字来决定从0幅度到满幅度的转换时间,

// 控制子最小只能到0x03,再小就不能正常输出波形。

// 写控制寄存器 输出矩形的ASK调制模式

//8'd14 : data <= 8'h14; //0x1D

//8'd15 : data <= 8'h47; //0x1E 配置PLL时钟 280M

//8'd16 : data <= 8'h01; //0x1F single tone 外部更新

//8'd17 : data <= 8'h60; //0x20

default:data <= 8'h00;

endcase

else;

矩形输出不了,按程序配置后输出的是正弦波。(相同部分的程序就不贴了,矩形和梯形相比只是更改了0x20寄存器的配置)

always@(posedge CLK)

if(RST)

address <=6'b00_0000;

else if(mst_rst_ok)

case(ctrl_cnt)

// ************** 写寄存器 ***********************

// FTW1

8'd2 : address <= 6'b00_0100; //0x04 FTW1_5

8'd3 : address <= 6'b00_0101; //0x05 FTW1_4

8'd4 : address <= 6'b00_0110; //0x06 FTW1_3

8'd5 : address <= 6'b00_0111; //0x07 FTW1_2

8'd6 : address <= 6'b00_1000; //0x08 FTW1_1

8'd7 : address <= 6'b00_1001; //0x09 FTW1_0

// 输出幅度乘法器

8'd8 : address <= 6'b10_0001; //0x21

8'd9 : address <= 6'b10_0010; //0x22

8'd10 : address <= 6'b10_0011; //0x23

8'd11 : address <= 6'b10_0100; //0x24

// 写控制寄存器

8'd14 : address <= 6'b01_1101; //0x1D

8'd15 : address <= 6'b01_1110; //0x1E 配置PLL时钟

8'd16 : address <= 6'b01_1111; //0x1F

8'd17 : address <= 6'b10_0000; //0x20

default:address <= 6'b00_0000;

endcase

else;

always@(posedge CLK)

if(RST)

data <=8'b1111_1011;

else if(mst_rst_ok)

case(ctrl_cnt)

// FTW1

8'd2 : data <= FTW1[47:40]; //0x04 FTW1_5

8'd3 : data <= FTW1[39:32]; //0x05 FTW1_4

8'd4 : data <= FTW1[31:24]; //0x06 FTW1_3

8'd5 : data <= FTW1[23:16]; //0x07 FTW1_2

8'd6 : data <= FTW1[15:8]; //0x08 FTW1_1

8'd7 : data <= FTW1[7:0]; //0x09 FTW1_0

// 输出幅度乘法器

8'd8 : data <= ask_out_range[15:8];//0x21

8'd9 : data <= ask_out_range[7:0]; //0x22

8'd10 : data <= 8'h0;//0x23

8'd11 : data <= 8'h0; //0x24

// 写控制寄存器 输出矩形的ASK调制模式

8'd14 : data <= 8'h14; //0x1D

8'd15 : data <= 8'h47; //0x1E 配置PLL时钟 280M

8'd16 : data <= 8'h00; //0x1F single tone 外部更新

8'd17 : data <= 8'h60; //0x20

default:data <= 8'h00;

endcase

else;

给你发的程序UD_CLK都是外部更新的,内部更新的程序我也做了,效果和这个一样。

我们是用FPGA配置的,代码使用verilog实现。

麻烦看哈我是那个寄存器配置的有问题或者那不对,非常感谢。。。。谢谢。。

举报

举报