[tr]请教个问题,我配置EMIFA的CS0使用的SDRAM接口,参数是数据位宽16、突发长度为8。在DSP代码中直接用CPU读取CS0地址的short类型值,Byte地址每次累加2(short指针加1),连续读8个。EMIFA另一端为模拟SDRAM接口的

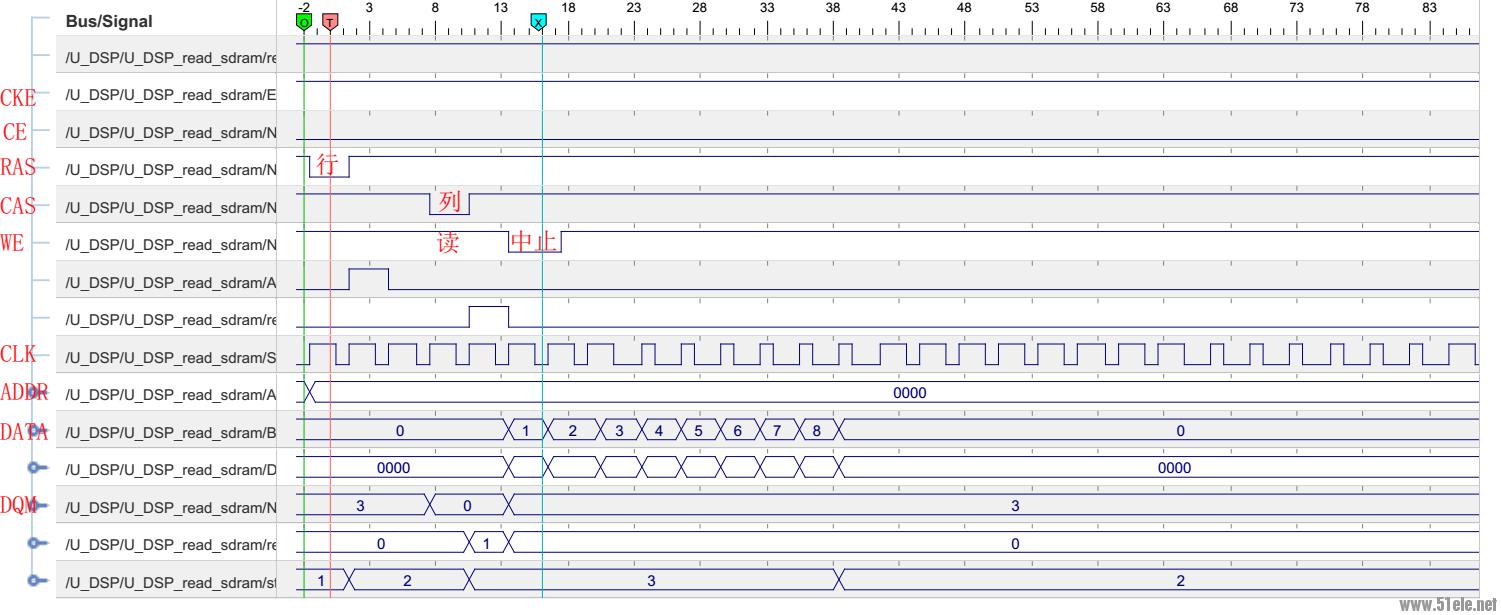

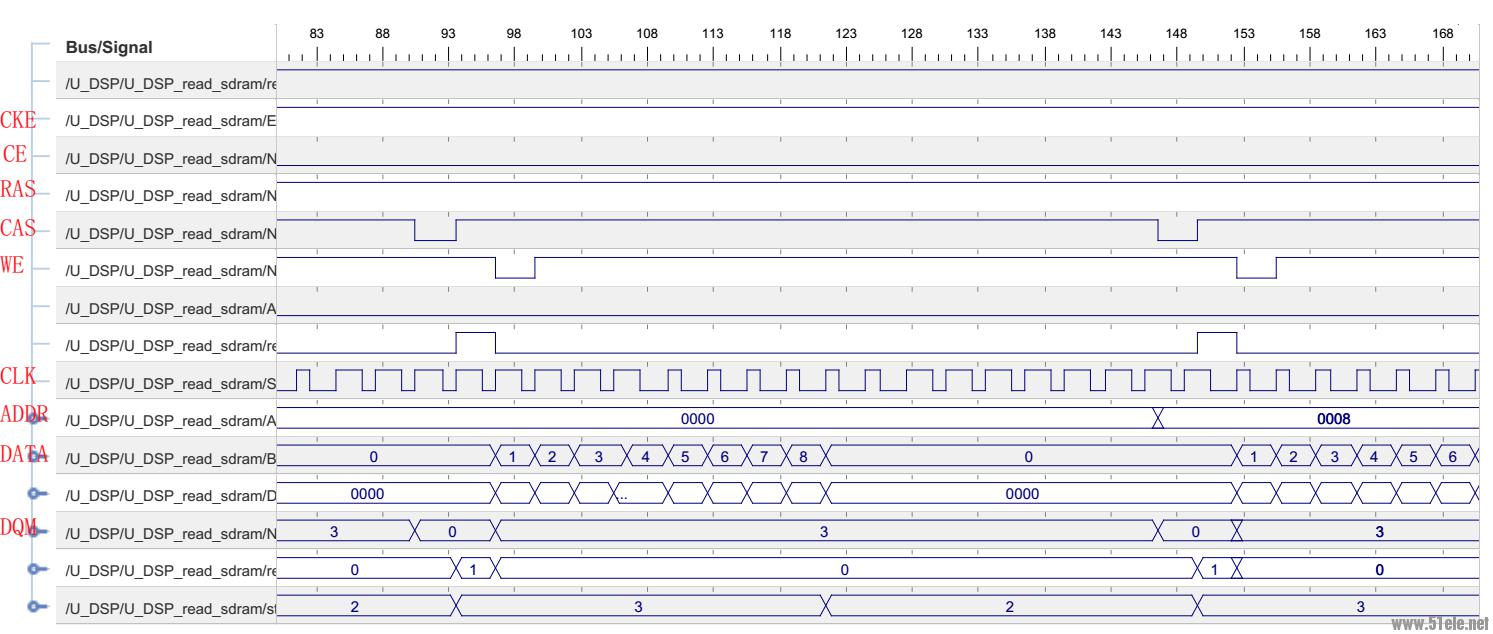

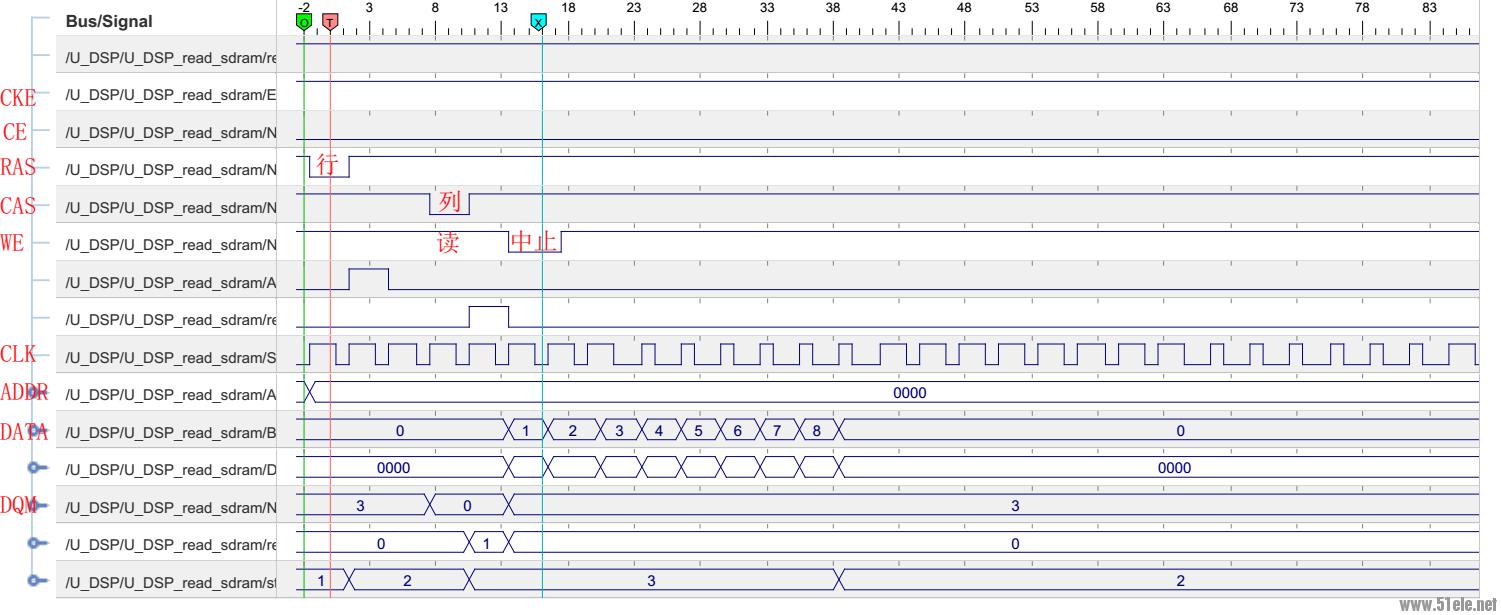

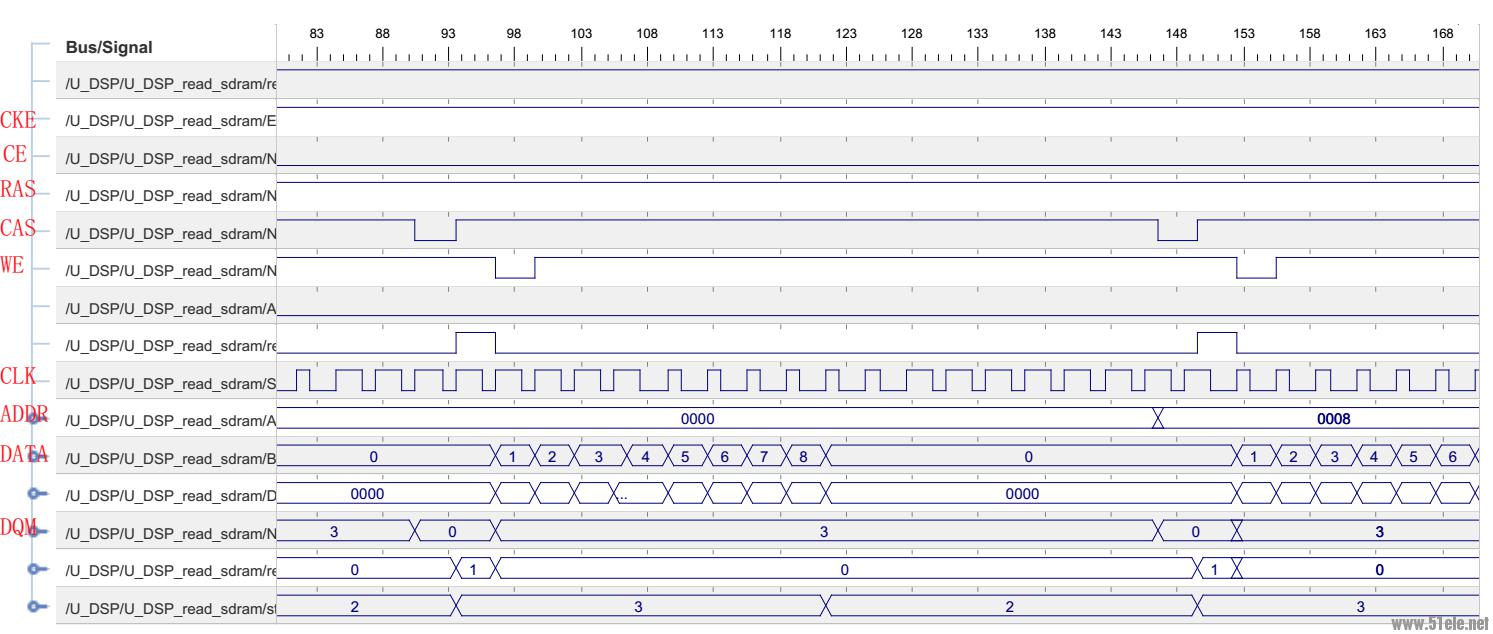

FPGA,FPGA数据总线输出是从1开始累加的数,一个突发读到的应该是从1到8的8个数据,但是DSP得到的结果是[1,2,1,2,1,2,1,2]。从FPGA抓到的waveform看抓到的数据是这样的:当每次突发读取开始后在读取第一个数据的时候就发出了突发中止命令,连续读了多个burst。附件附了抓取的前三个突发,其他突发现象一致;由于不是用的同步时钟抓取的,所以CLK看起来不是很均匀。当DSP用memcpy函数读取SDRAM时,能得到[1,2,3,4,1,2,3,4],突发在第三个数据时发出中止命令。现象大概就是这样的,请问出现这种情况的原因是什么,或者怎么正确使用配置EMIFA的SDRAM接口?demo里面有SDRAM相关例程吗,没有找到,只找到异步数据接口的。

下面是chipscope抓的图

[/tr]

举报

举报