[tr]

需求:

目前项目需要UPP发送时钟为24M,用PLL0分频只能得到28.5M,故选用PLL1作为UPP、UART2模块输入时钟。

结果:

现在已经实现了upp发送时钟24M,然而UART2接PC串口助手得倒乱码信息。

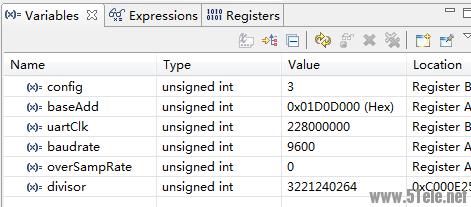

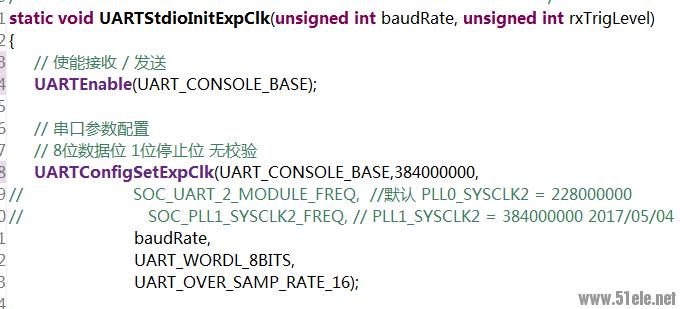

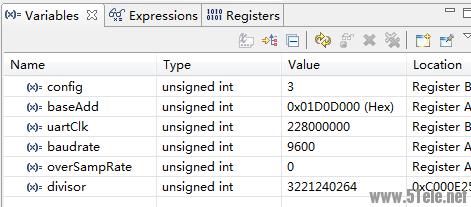

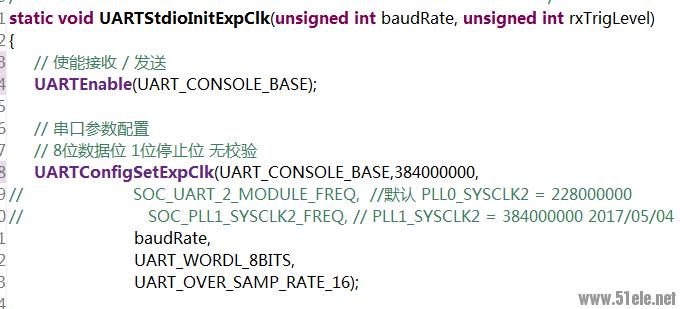

Variables窗口看到uart2模块输入时钟为228M(应该是我设定的PLL1_SYSCLK2=384M)没变化,如下图:

尝试解决:

尝试解决:

1、修改波特率

,发现还是115200;

2、后来发现UART2配置前就使能了,不知道是不是源码的BUG。

问题还是没解决,希望大神们抽时间看看。拜谢!

注: 在uPP_B_TO_A例程上修改

问题还是没解决,希望大神们抽时间看看。拜谢!

注: 在uPP_B_TO_A例程上修改

[/tr]

,发现还是115200;

,发现还是115200;

举报

举报

举报

举报

举报

举报