结论

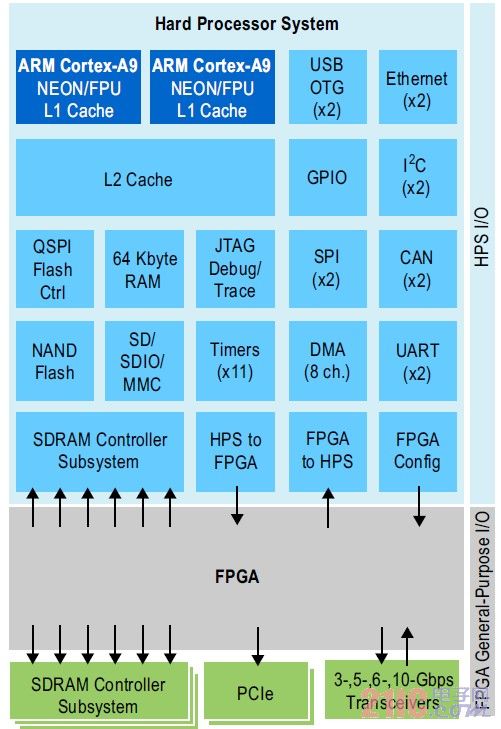

与以往相比,目前的嵌入式系统开发人员必须面对激烈的竞争,迅速应对多变的标准、协议和需求,以更少的资源满足越来越高的各种市场需求。含有硬核处理器内核的SoCFPGA 不但支持设计人员解决这些设计难题,而且还帮助他们获得了明显的产品及时面市、价格/ 性能、突出产品特点以及长寿命产品等优势。与传统方案相比,现在已经到达了一个关键点,基于FPGA 的SoC 成为可行而且是首选的方法,必将在市场上获得广泛应用。

结论

与以往相比,目前的嵌入式系统开发人员必须面对激烈的竞争,迅速应对多变的标准、协议和需求,以更少的资源满足越来越高的各种市场需求。含有硬核处理器内核的SoCFPGA 不但支持设计人员解决这些设计难题,而且还帮助他们获得了明显的产品及时面市、价格/ 性能、突出产品特点以及长寿命产品等优势。与传统方案相比,现在已经到达了一个关键点,基于FPGA 的SoC 成为可行而且是首选的方法,必将在市场上获得广泛应用。

举报

举报

举报

举报

举报

举报

举报

举报