在电子信息领域,函数发生器(信号源)是通用的设备。近年来电子信息技术的飞速发展,使得各领域对信号源的要求在不断提高。不但要求其频率稳定度和准确度高,要求频率改变的方便性,而且还要求可以产生任意波形,输出不同幅度的信号等。而实现频率合成方法有许多种,但基本上可以归纳为直接频率合成和间接频率合成两大类方法。采用传统的频率合成技术要实现上述要求,几乎是不可能的。

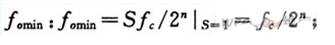

虽然根据奈奎斯特采样定理,一个周期采样两个点即可保证信号的频谱信息不丢失,但为了输出信号滤波后失真较小,一个周期至少采样8个点;故可知S的取值范围应该为1~2n-3;

虽然根据奈奎斯特采样定理,一个周期采样两个点即可保证信号的频谱信息不丢失,但为了输出信号滤波后失真较小,一个周期至少采样8个点;故可知S的取值范围应该为1~2n-3;

举报

举报

举报

举报

举报

举报

更多回帖