本次带来

FPGA系统性学习系列,今天开始正式更新,之前更新过类似的郝旭帅FPGA零基础学习系列,由于时间久远,之前的系列所用开发操作软件、硬件设备及所涉及知识维度都有待更新及完善。

本系列将带来FPGA的系统性学习,从最基本的数字

威廉希尔官方网站

基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让

电子、信息、

通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

Intel FPGA开发流程

作者:郝旭帅 校对:陆辉

本篇目录

1. 设计前准备

2. 建立工程

3. 输入设计

4. 综合和分析

5. RTL

仿真

6. 锁定管脚

7. 布局布线

8. 时序仿真

9. 生成配置文件并下载

正文

本篇将设计一个简单的二输入与门,来讲解整个设计流程。至于设计语言就不在单独列出一个章节去做特殊说明,语法、操作、实验将同时讲解,这样更具有带入性,便于读者阅读和学习。

1设计前准备

在设计之前我们需要在两个方面进行准备:硬件方面和软件方面。

开发FPGA设计,最终的产品是要落在使用FPGA芯片完成某种功能。所以我们首先需要一个带有Intel FPGA芯片的

开发板。

本文中设计将采用CYCLONE系列FPGA进行讲解,如果读者有其他系列(必须是Intel FPGA,否则无法在Quartus上开发),也可以进行学习,不同系列的开发流程基本相同。

我们需要综合工具-quartus 软件和仿真工具-modelsim软件。正确安装这两个软件是开发Intel FPGA的必要条件。

图1 :Quartus 软件图标

图1 :Quartus 软件图标

按照《quaruts prime 18.0标准版安装与破解-郝旭帅团队V1》的方式安装,Modelsim软件的图标将不会出现在桌面上。并不是没有安装上,而是此时Quartus软件认为Modelsim软件只是它的一个小程序包而已,所以就没有体现单独的软件图标。

当准备好软件后,笔者向大家推荐一个工程管理的方式,也是本文中做工程管理的方式,这样会比较清楚。

做设计的话,会编写很多设计文件、仿真文件以及综合器会给我输出很多的过程文件等等,那么这些文件最好都能有自己的一个“归宿”,不要乱放。

路径和命名中不允许出现非法字符(合法字符包括:数字、字母、下划线。特别说明:空格是非法的),笔者建议以字母开头。

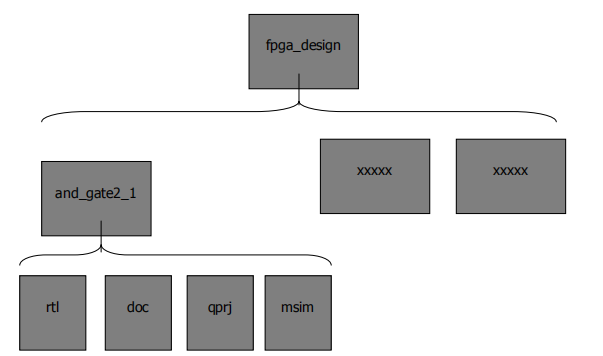

我们是做FPGA开发设计的,首先我们将建立一个文件夹,专门用来放FPGA开发设计。例如:E:/fpga_design。

在后续的开发设计中,我们会做各种各样的设计。每个设计都有自己的名字,在上述文件内,用实验的名字命名一个文件夹。名字的话一定要带有某种含义,不建议随便给个字母序列当做名字。例如:第一个要做的二输入与门的设计,命名为and_gate2_1。

在建立完某项设计的文件后,依次在其里面新建四个文件夹,分别为:rtl、qprj、msim、doc。

图 2 :工程管理文件脉络示意图

图 2 :工程管理文件脉络示意图

rtl文件夹用于存放设计的源文件。

doc文件夹用于存放设计的一些文档性的资料。

qprj文件夹用于存放quaruts 工程以及quartus生成的一些过程性文件。

msim文件夹用于存放仿真文件。

在 FPGA 设计时,主要是这四个文件的使用。某些时候我们也会新加一些文件,例如:FPGA板卡需要我们设计自己时,就会多一个文件夹

PCB,用于存放PCB相关的工程或者源文件等。

2建立工程

做好设计前准备后,就可以开始建立quartus 工程了。

在做设计时,都是以工程为主体的设计。在没有工程的情况下,利用quartus软件打开设计源文件等,也是不支持编译和综合的。

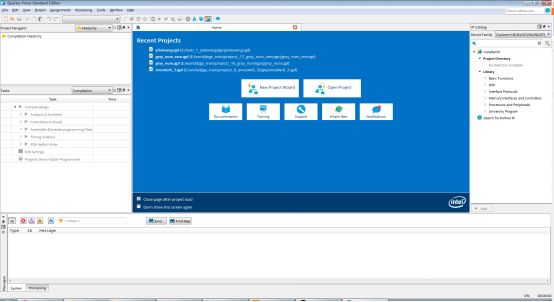

双击quartus 软件的图标(图4-1),打开quartus软件。在有的电脑上,软件启动的速度不是很快(在确保自己已经双击打开的前提下,可以等待1分钟),不要多次去双击图标,容易造成PC卡死或者启动了很多个quartus软件。

图3 :quartus 18.0界面

图3 :quartus 18.0界面

笔者这里不对每个界面进行单独介绍,后续用到那个功能或者界面时,会单独介绍说明。

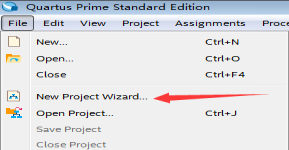

点击左上角File,选择New Project Wizard…。

图4 :打开新工程创建向导

图4 :打开新工程创建向导

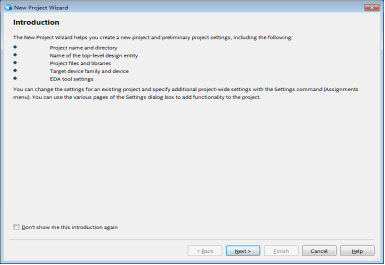

打开新工程向导,首先出现一个工程向导介绍说明。

图5 :工程向导的介绍界面

图5 :工程向导的介绍界面

在工程向导中,我们会指定工程名称和位置,顶层实体的名称,工程文件和库文件,目标器件,EDA工具。

在复杂设计时,会将威廉希尔官方网站

分成各个小模块去做设计,最终还需要一个大模块将这些小模块包括进来,对外呈现都是大模块的接口。此时,这个大模块就是顶层实体(TOP level en

tity)。如果设计中只有一个模块,那么这个模块就是顶层实体。

点击Next。

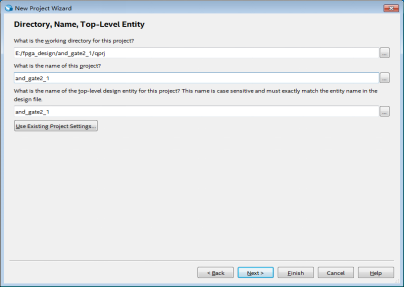

图6 :指定工程位置、工程名称和顶层实体的界面

图6 :指定工程位置、工程名称和顶层实体的界面

将工程的位置指定到之前我们准备好的文件夹(qprj)中。点击编辑框后面的三个小点,进行文件搜索指定。

工程的名称就是采用之前我们做的设计文件夹的名字,这个名字可以是任意的,笔者建议和文件夹保持一致,因为当初建立文件夹时,就是选择用工程的名字。直接输入工程名称and_gate2_1即可。

顶层实体的名字会自动出现,与工程的名字保持一致。我们也可以重新指定一个新名字,笔者建议与工程名字保持一致。

点击Next。

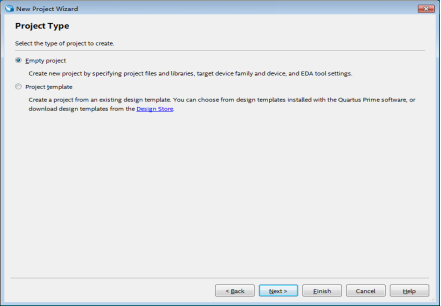

图7 :选择建立的工程的类型

图7 :选择建立的工程的类型

选择空白工程(默认空白工程),点击Next。

图8 :添加文件

图8 :添加文件

建立工程时,我们可以直接向工程中添加已有的文件。一般我们选择什么都不添加,后续设计中,如果有提前做好的文件,也是选择什么都不添加。建立完工程后,依然可以向工程添加文件。

点击Next。

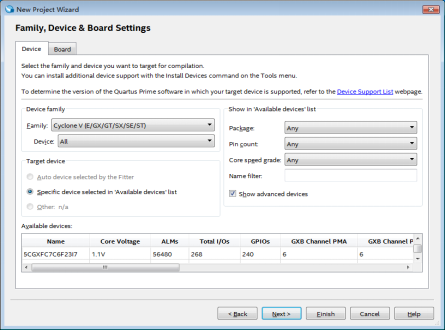

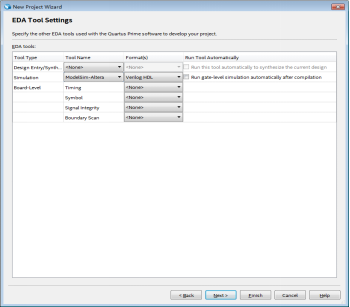

图9 :选择目标器件

图9 :选择目标器件

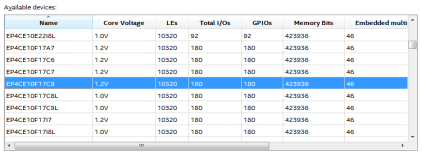

FPGA设计最终是要落实到芯片内部,在这里要选择对应的芯片(自己手里开发板的FPGA芯片)。芯片的型号在FPAG的芯片上有描述,如果芯片上看不清楚,或者芯片在被其他东西挡住,可以查看开发板的资料,一般都有介绍。笔者手中开发板的FPGA的型号为EP4CE10F17C8N。后续所有的选择将按照笔者手中的型号进行设计和选择,读者不相同的,请自行改动。如果暂时还没有开发板的读者,可以跟着笔者选择继续下面的步骤(没有开发板的话,后面有一些步骤是做不了的)。

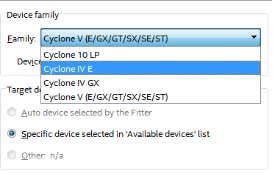

选择时,首先选择对应的系列。

图10 :选择芯片所对应的系列

图10 :选择芯片所对应的系列

选择对应的系列后,可以看到下面的器件列表(此列表的窗口是可以拉大的,可以直接扩大整个界面)中,就出现很多的器件。呈现的器件都是按照一定的规律进行排列的,可以很快的找到自己的芯片,然后单击选择芯片(先不考虑为什么没有EP4CE10F17C8N,而选择EP4CE10F17C8)。

图11 :器件列表

图11 :器件列表

如果每次新建工程都是这样去寻找芯片的话,是有一定的累人。好在这个软件给我们提供了筛选面板,我们可以把筛选条件输入进去。

图12 :器件筛选

图12 :器件筛选

设置好筛选条件后,器件列表中就只有四个器件了,很容易就可以找到我们这款芯片。

筛选条件中有封装类型、管脚数目和速度等级。那么我们怎么知道自己手中的芯片的这些信息呢?

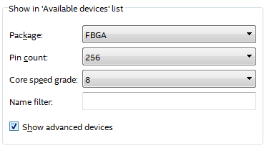

答案都隐藏在芯片的名字中。笔者手中的是CYCLONE IV系列的片子,下面就介绍一下这个系列的命名方式。

图13 :CYCLONE IV E系列命名规则

图13 :CYCLONE IV E系列命名规则

如果是其他系列,请自行参考所对应的芯片手册。

通过观察图4-13,EP4CE10F17C8N中末位N,只是表示无铅封装,和具体内部机构没有任何关系。故而选择不带N的,也是可以的。

注意无论是哪种方法,最后找到自己想要的芯片后,一定要点击它,选中它。

点击Next。

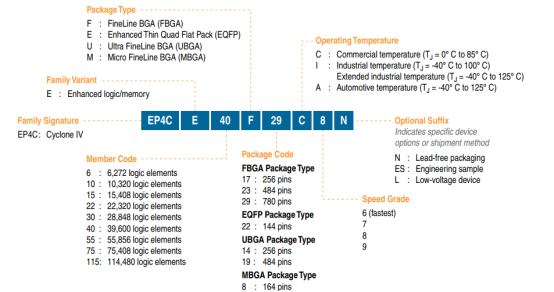

图14 :选择EDA工具

图14 :选择EDA工具

Quartus软件是一个综合工具,他可以关联一些其他的工具协助设计FPGA。在这里我们在simulation一栏,工具选择modelsim-altera,格式选择verilog HDL。其他保持默认。

点击Next。

图15 :工程向导配置总结

图15 :工程向导配置总结

这个总结显示出在新工程向导中,我们所做的所有的设置。大家可以检查一下,如果发现那一项和自己的要求不一致,就需要点击back,修改后,在回到此步骤。

点击Finsh,完成工程创建。

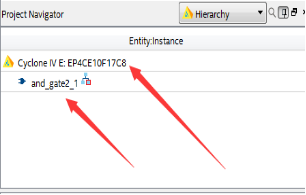

图16 :工程建立完成后,工程向导界面

图16 :工程建立完成后,工程向导界面

工程建立完成后,工程向导界面显示出选择的器件和指定的顶层实体。

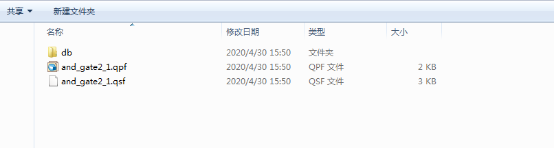

打开qprj文件夹。

图17 :建立完工程后的qprj文件夹

图17 :建立完工程后的qprj文件夹

db文件夹为基础数据文件夹。

.qpf为quartus project file,quartus 工程文件。如果此时将quatus关闭了,双击此文件就可以打开工程。

.qsf为quartus settings file,quartus 设置文件。在quaruts里面做的大部分操作都会记录到此文件中。

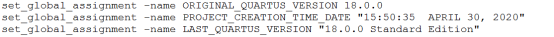

Quarus 的版本很多,如果用一个版本建立的工程,用另外一个版本打开可能会出一些bug,所以建议采用使用已建好工程的版本打开。可以使用记事本的方式打开.qsf。

图18 :qsf文件的一部分

图18 :qsf文件的一部分

通过查看.qsf文件,可以了解到工程的最初用什么版本建立,最后用什么版本打开(打开时,建议采用最后的版本打开)。

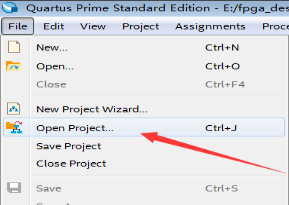

打开工程的方式,不建议采用双击.qpf文件。有时间一个PC上面,会有多个quaruts软件的情况,如果直接双击,就会采用某一个版本打开,这不一定是我们想要的。

建议打开工程的方式,首先查看应该选择的版本,启动对应的版本quartus软件,点击File,选择Open project(不要点击Open),找到工程,启动。

图19 :打开工程的途径

图19 :打开工程的途径

3输入设计

当建立完工程后,就可以输入设计。输入设计的方法有三种:原理图输入、HDL代码输入、原理图和HDL代码混入输入。

原理图输入就是以现有模块级联的方式实现功能。

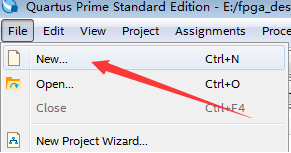

点击File,选择New。

图20 :新建模块

图20 :新建模块

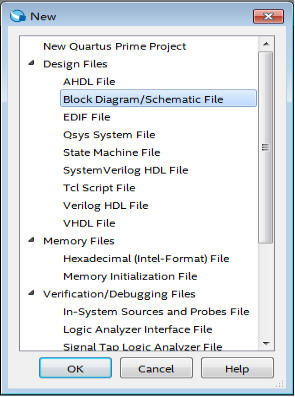

选择design file中的Block Diagram/Schematic File。点击ok。

图21 :新建文件列表

图21 :新建文件列表

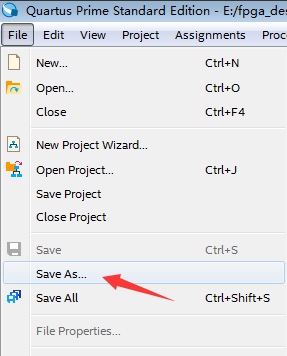

对于新建的bdf文件立刻进行另存为。

图22 :另存为

图22 :另存为

另存为到qprj文件夹。Bdf文件是只有quartus软件才能认可,不具有移植性,把它放到工程文件夹中。

图23 :保存路径和名称

图23 :保存路径和名称

点击保存。特别注意保存路径和保存名称。不要盲目直接点击保存,一定要再三确认。

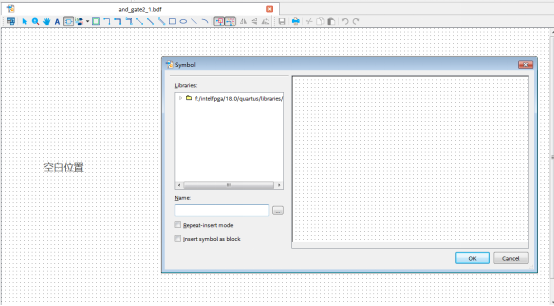

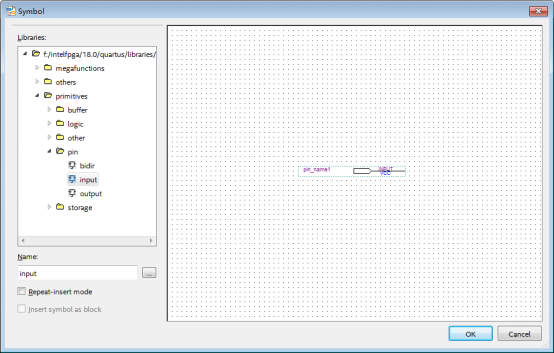

在BDF文件的空白位置,双击,打开添加原件的窗口。

图24 :打开添加原件的窗口

图24 :打开添加原件的窗口

在libraries中,选择and2,点击ok。

图25 :添加二输入与门

图25 :添加二输入与门

鼠标会拖动一个二输入与门的符号,此时点击鼠标左键,一个二输入的与门就放置在文件中了。

图26 :放置的二输入与门

图26 :放置的二输入与门

当添加完二输入与门后,也就意味着芯片内部的设计完成。现在需要将内部设计与外部相连接。芯片与外界相连接靠的是IO。

双击空白处,选择input(输入),点击ok。添加输入IO。

图27 :添加input管脚

图27 :添加input管脚

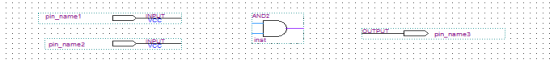

二输入与门,要有两个输入。同样的方法,再次添加一个。同时也要有一个输出,选择output(输出)(在input下面),添加一个输出。

图28 :添加两个输入和一个输出

图28 :添加两个输入和一个输出

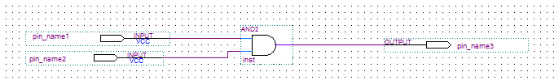

将管脚和二输入与门进行相连接。

把鼠标移至需要连接线的地方时,鼠标会自动变为十字状(不是十字状箭头),并且右下带有一个“7”形的导管。然后按住鼠标左键进行导线的引出。当连接到另外一个接口时,

就会出现一个小方框,证明已经连接上,此时释放鼠标左键即可。

图29 :连接完成图样

图29 :连接完成图样

此时默认两个输入的管脚的名字为pin_name1和pin_name2。在设计时,二输入与门我们将其输入命名为一个为A,一个为B,输出为Y。

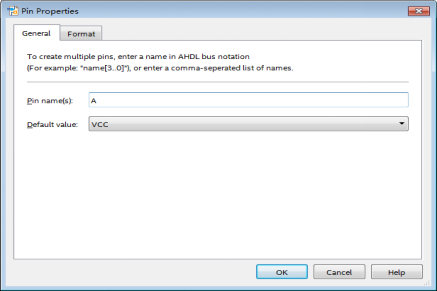

右击pin_name1,选择properties。

图30 :选择属性

图30 :选择属性

将pin name改为A。点击ok。

图31 :修改管脚名称

图31 :修改管脚名称

将其他两个管脚也做对应修改。

图32 :修改完管脚名称的图样

图32 :修改完管脚名称的图样

此时点击保存(ctrl + s),使用原理图的输入方式就完成了。

用计算机语言设计一个数字威廉希尔官方网站

系统,其实质就是用一种语言描述一个硬件模型,因此这样的语言又称为硬件描述语言(Hardware Description Language),或使用缩写HDL。虽然现在HDL已经有多种语言版本,而且还在发展中。但是在本书讨论的HDL仅包括现在最常使用的Verilog HDL和VHDL两种语言系统。

目前在国内做FPGA设计的公司中,使用Verilog HDL占据大多数,故而本书以Verilog HDL为主,在后续的章节中,专门设置一章来讲解VHDL。

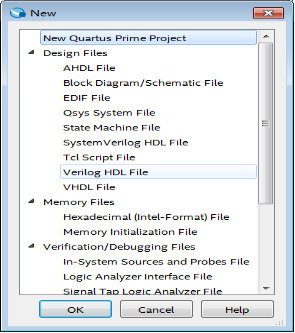

选择File,New,选择design file中的verilog HDL file。点击ok。

图33 :新建verilog HDL file

图33 :新建verilog HDL file

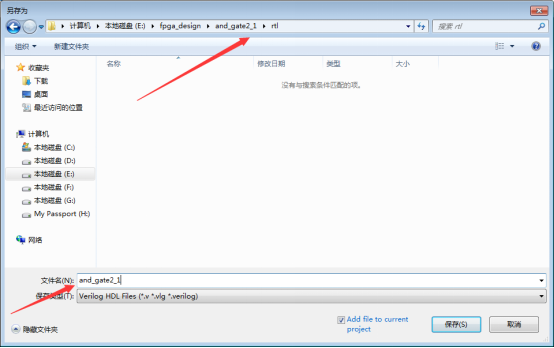

新建完成后,立刻另存为,保存到rtl中。hdl文件的移植性比较高,无论在哪个平台都是通用的。

图34 :保存verilog HDL文件

图34 :保存verilog HDL文件

保存时,注意名字和保存路径。Verilog文件的后缀为.v。

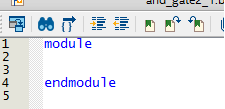

建立完,verilog HDL文件后,就需要输入二输入与门所对应的verilog代码了。

Verilog 语法和C很相似,学习起来比较容易。下面我们按照做威廉希尔官方网站

的方式讲解verilog语言。

做威廉希尔官方网站

的话,首先需要拿出一块打的面包板,剪出合适大小的一块。相当于圈了一个地方,做设计只能在这块区域内。

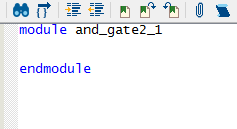

对于verilog语言来说,需要用module和endmodule圈出一个区域,设计代码只能在这块区域中。Verilog语言区分大小写,我们一律采用小写。module和endmodule是verilog的关键字,在综合器中会变蓝。如果endmodule没有变蓝,请多打一个回车或者空格。

图35 :verilog第一步

图35 :verilog第一步

当剪出合适大小的面包板后,需要其上面写一个名字。后面应用也好,说起来也好,好歹有个名字。

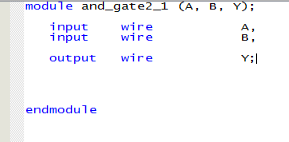

在verilog中,也需要有一个module name。

在verilog中命名的话,需要遵从一定的规则。由字母、数字、下划线构成;建议字母开头;不能够与verilog的关键字相同;命名是要有一定的意义。

对于module name来说,一般还有一个要求,与文件名称保持一致。那么此时我们要做二输入与门,文件名称是and_gate2_1。要求module name也写成and_gate2_1。

图36 :verilog第二步

图36 :verilog第二步

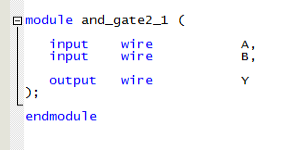

当对面包板命名后,需要给它添加输入和输出的端口(合理的布局接口)。

二输入与门有两个输入,一个为A,另外一个为B;一个输出为Y。在verilog中,布置接口的方式有两种。

图37 :布置接口的第一种方式

图37 :布置接口的第一种方式

图38 :布置接口的第二种方式

图38 :布置接口的第二种方式

在verilog中,module name(and_gate2_1)之后的那个括号中的内容成为端口列表。

Verilog布置接口的第一种方式为1995标准,第二种方式为2003标准。目前大多数平台都可以支持这两种方式。笔者建议用2003标准。

端口列表中,描述端口时,用逗号隔开,最后一个端口后面不加逗号。在端口列表的括号后面有一个分号。

对于描述端口来说,有最基本的四项:方向、类型、位宽、名称。

input表示输入,output表示输出,inout表示输入输出。

类型中比较常用的有两种:一种是wire,另外一种reg。wire类型时,wire可以省略不写。另外input必须是wire类型。笔者建议wire不省略,都写上。

在做威廉希尔官方网站

时,位宽表示有几根线。有时候为了方便,会将同一种类的线进行同时命名,此时就需要用到位宽。例如:5位的地址线。可以单独命名5次,但是比较麻烦。位宽用中括号括起来,例:[3:0],[3:1],[2:5]。如果位宽为1的话,省略不写。笔者建议位宽的右侧为0,左侧为位宽减一。

名称就是为这个输入命名了一个名字。命名时要遵从verilog命名规则。

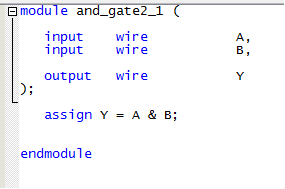

在做完端口后,需要在面包板上做出符合功能的设计,然后用连接线将设计和输入输出管脚相连接。

二输入与门的设计是需要在中间放一个组合逻辑威廉希尔官方网站

二输入与门。

Verilog中,描述组合逻辑的第一种方式是利用assign语句进行描述。

图39 :assign语句描述二输入与门

图39 :assign语句描述二输入与门

assign语句要求被赋值变量(Y)为wire类型,中间采用阻塞赋值(=)的方式,最后面是赋值表达式,在verilog中,算术与用&来表示(后续介绍算术运算和逻辑运算的区别)。

至此,二输入与门的HDL输入就完成了。

在复杂设计时,我们可以用HDL代码生成底层模块,用原理图的方式,将底层模块进行连接。此方式在后续的章节中介绍。

4综合和分析

当设计输入完成后,需要对设计进行综合分析,同时也检查一下其中是否存在错误。可以单击综合分析按钮,可以双击综合分析选项,也可以利用快捷键(Ctrl + K)。

图40 :综合分析按钮

图40 :综合分析按钮

图41 :综合分析选项

图41 :综合分析选项

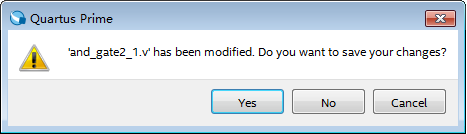

进行综合分析时,有时会提出一个提示:

图42 :某文件被改变,是否要保存

图42 :某文件被改变,是否要保存

出现上述提示,就证明我们在设计时,修改了某些文件后,没有点击保存。此时点击Yes即可。但是这是一个非常不好的习惯,建议大家修改完任何设计都要及时保存。

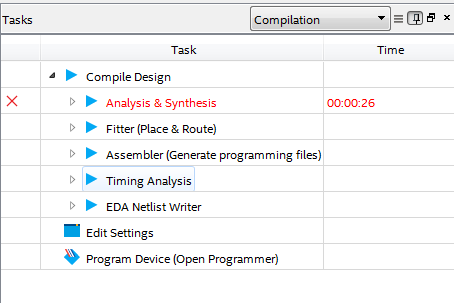

图43 :Task的综合分析前面的进度条和后面的已用时间

图43 :Task的综合分析前面的进度条和后面的已用时间

经过一段时间后,会出现错误。

图44 :出现错误

图44 :出现错误

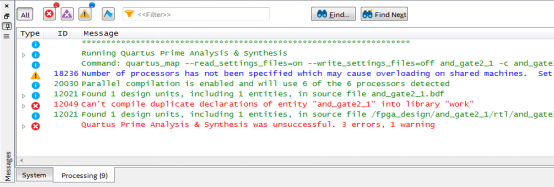

出现错误后,可以观察quartus 的下部massage窗口。

图45 :massages窗口报错信息

图45 :massages窗口报错信息

报错信息为:错误(12049):无法将实体“and_gate2_1”的重复声明编译到库“work”中。报错的原因是我们在本工程中声明了多个and_gate2_1,在威廉希尔官方网站

中是不允许出现多个威廉希尔官方网站

模块是同样的名字。

在设计时,为了演示原理图输入和HDL代码输入,工程中存在原理图输入的and_gate2_1和HDL代码输入的and_gate2_1。

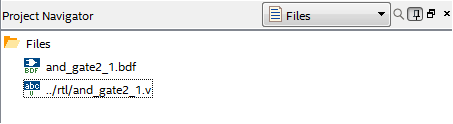

在工程向导界面,选择Hierarchy,选择Files。Hierarchy为结构,显示工程的威廉希尔官方网站

模块的结构;Files为文件,显示工程中存放的所有文件。可以利用此方式查看,工程中是否存在多个and_gate2_1。

图46 :选择Files界面

图46 :选择Files界面

在Files界面中,可以发现工程中确实存在两个and_gate2_1。

图47 :Files界面

图47 :Files界面

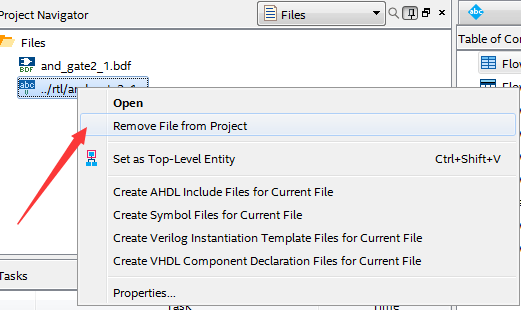

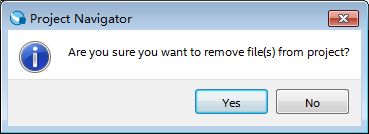

此时右键选择第and_gate2_1.v,选择Remove file from project。

图48 :选择移除

图48 :选择移除

随后在确定界面点击Yes。

图49 :确认移除

图49 :确认移除

将其移除工程后,就会只剩下一个原理图输入的and_gate2_1。然后进行综合分析,等待结果完成。

图50 :综合分析成功

图50 :综合分析成功

如果中间有错误的话,请参考输入设计中的原理图输入,查看自己的步骤是否正确。

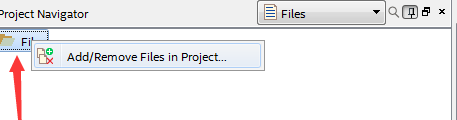

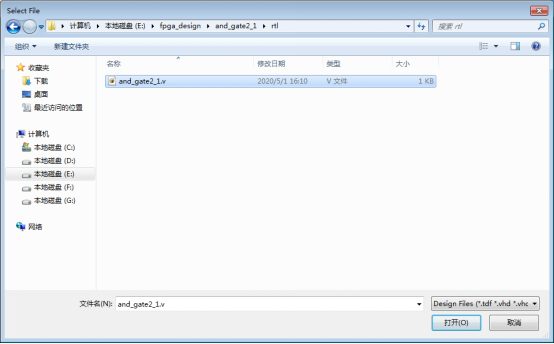

再一次选择到Files界面,将and_gate2_1.bdf移除。将HDL代码输入的and_gate2_1.v

重新添加回来。在Files上右键,选择Add/Remove Files in project(添加或移除文件)。

图51 :从工程中添加或移除文件

图51 :从工程中添加或移除文件

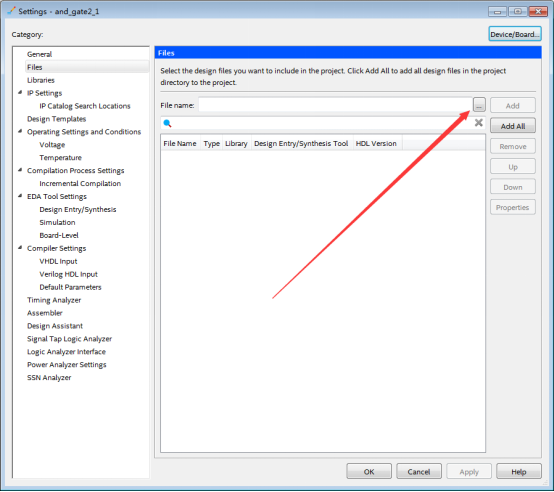

选择编辑框后面三个点。

图52 :寻找添加文件

图52 :寻找添加文件

找到and_gate2_1.v,选中,点击打开。

图53 :添加选中文件

图53 :添加选中文件

注意添加文件的路径,and_gate2_1.v是存放在rtl文件夹中。

然后点击apply,OK。就添加成功。

图54 :确认添加文件

图54 :确认添加文件

点击综合分析,确认综合分析成功。如果综合分析失败,请参考输入设计中的HDL输入,查找错误的地方。

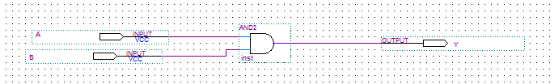

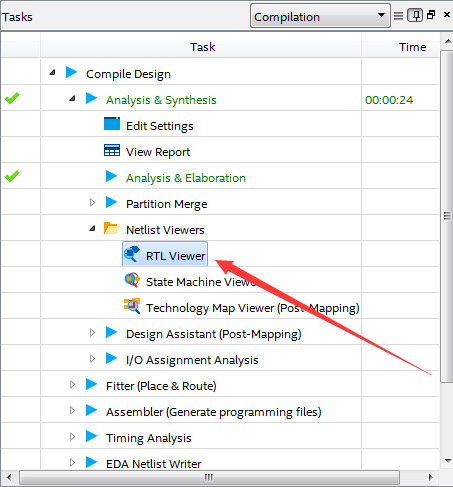

无论是哪一种输入方式,综合分析成功。双击RTL视图选项,打开RTL视图,查看quartus综合出的威廉希尔官方网站

模型。

图55 :RTL视图的选项

图55 :RTL视图的选项

在RTL视图中,综合出来的威廉希尔官方网站

图,只是威廉希尔官方网站

模型而已。在FPGA中是没有与门的,有的只是LUT等效的二输入与门威廉希尔官方网站

。

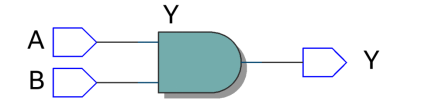

图56 :RTL视图的二输入与门

图56 :RTL视图的二输入与门

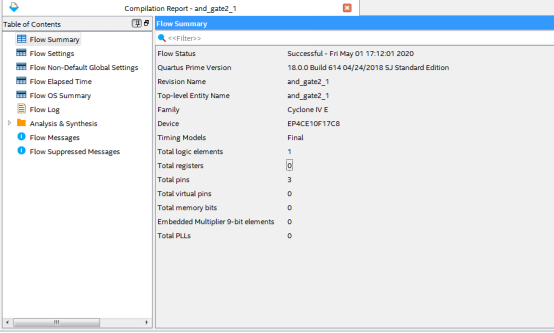

综合分析成功后,会产生一个报告。

图57 :综合分析报告

图57 :综合分析报告

在报告中,可以看出综合状态、软件信息、工程版本信息、顶层实体、器件系列、目标器件、时序模型、逻辑单元数量、寄存器数量、管脚数量、虚拟管脚数量、存储器大小、嵌入式乘法器的使用个数、锁相环使用个数。

只是设计了一个二输入的与门,所以使用一个逻辑单元,3个管脚,其他都没有涉及到。

下篇带来FPGA零基础学习:Intel FPGA 开发流程(下)

举报

举报