晶振有两个比较重要的参数,频偏和温偏,单位都是PPM,通俗说,晶振的标称频率不是一直稳定的,某些环境下晶振频率会有误差,误差越大,威廉希尔官方网站

稳定性越差,甚至威廉希尔官方网站

无法正常工作。

所以在PCB设计时,晶振的layout显得尤其的重要,有如下几点需要注意。

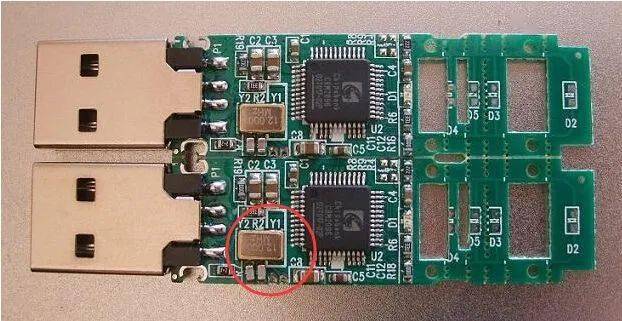

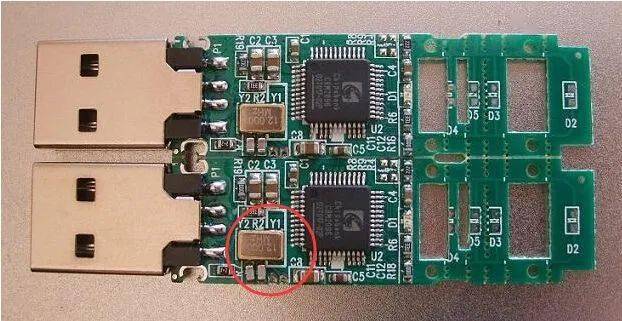

✔ 两个匹配电容尽量靠近晶振摆放。

✔ 晶振由石英晶体构成,容易受外力撞击或跌落的影响,所以在布局时,最好不要放在PCB边缘,尽量靠近芯片摆放。

✔ 晶振的走线需要用GND保护好,并且远离敏感信号如RF、CLK信号以及高速信号。

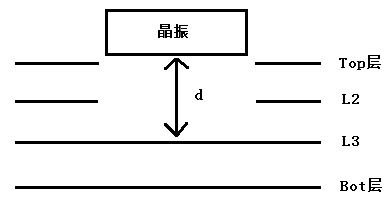

✔ 在一些晶振的PCB设计中,相邻层挖空(净空)或者同一层和相邻层均净空处理,第三层需要有完整的地平面,这么做的原因是维持负载电容的恒定。

晶振负载电容的计算公式是:

CL=C1*C2/(C1+C2)+Cic+Cp

Cic为集成威廉希尔官方网站

内部电容,Cp为PCB板的寄生电容,寄生电容过大,将会导致负载电容偏大,从而引起晶振频偏,这个时候减小匹配电容C1和C2可能会有所改善,但这也是治标不治本的措施。

晶振有两个比较重要的参数,频偏和温偏,单位都是PPM,通俗说,晶振的标称频率不是一直稳定的,某些环境下晶振频率会有误差,误差越大,威廉希尔官方网站

稳定性越差,甚至威廉希尔官方网站

无法正常工作。

所以在PCB设计时,晶振的layout显得尤其的重要,有如下几点需要注意。

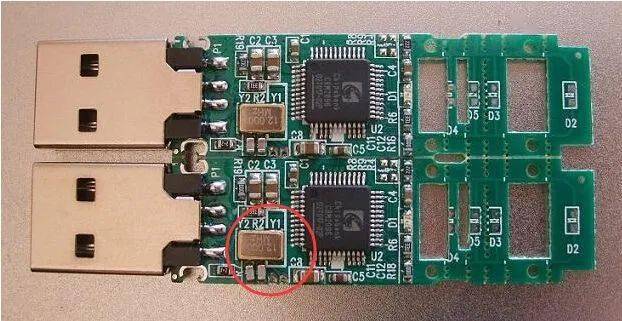

✔ 两个匹配电容尽量靠近晶振摆放。

✔ 晶振由石英晶体构成,容易受外力撞击或跌落的影响,所以在布局时,最好不要放在PCB边缘,尽量靠近芯片摆放。

✔ 晶振的走线需要用GND保护好,并且远离敏感信号如RF、CLK信号以及高速信号。

✔ 在一些晶振的PCB设计中,相邻层挖空(净空)或者同一层和相邻层均净空处理,第三层需要有完整的地平面,这么做的原因是维持负载电容的恒定。

晶振负载电容的计算公式是:

CL=C1*C2/(C1+C2)+Cic+Cp

Cic为集成威廉希尔官方网站

内部电容,Cp为PCB板的寄生电容,寄生电容过大,将会导致负载电容偏大,从而引起晶振频偏,这个时候减小匹配电容C1和C2可能会有所改善,但这也是治标不治本的措施。

举报

举报

举报

举报

举报

举报

举报

举报