1 E2PROM介绍及其应用现状

E2PROM(Electically Erasable Programmable Read-Only Memory),即电可擦除只读存储器。它是一种非易欠性存储器,掉电后数据依然存在(一般可保存长达100年),读写耗电极低,擦写时只需相应的电信号即可,控制方式简单,体积小巧。价格便宜,被广泛应用于对数据存储安全性及可靠性要求较高的场合,如各类IC卡、智能家电、工业仪器仪表等。

但E2PROM使用寿命有限,一般为可擦写100万次,即某一位由1写为0或由0写为1的次数为100万次。一般的系统往往只对若干同定单元进行频繁的读写,很容易造成这些单元的损坏。而常用的E2PROM存储系统,只要某一个存储单元损坏,即使其他绝大部分单元都是完好的,也只能将整个E2PROM芯片报废。这既是对资源的浪费,也是系统正常运行的潜在风险。

为了延长E2PROM芯片的寿命,提高存储系统的可靠性,本文提出一种较可靠的E2PROM控制器设计方法,并在FPGA中用VHDL进行了实现。

2 本文E2PROM控制器的工作原理

在很多领域的存储系统中,可靠性对系统安全至关重要。为了避免系统出错,并延长系统的寿命,本文在适当牺牲存储效率的前提下,着重考虑提高存储系统的可靠性。

E2PROM存储器存储单元的损坏主要是由频繁的写操作造成的。若要解决问题,首先耍避免对同一单元进行频繁的擦写,降低存储单元损坏的可能;其次当某些单元损坏时,读写控制器应该能够跳过这些损坏的单元,保证系统能继续正常工作。本文设计的E2PROM控制器具有这两个方面的功能。

本文的设计思想是,将整个EzpROM地址空间划分为地址分配表区、备用区和数据区,如图1所示。

图1 E2PROM地址空间划分

在地址分配表区中只存储所有数据区或备用区存储单元的地址,初始时与数据区的每个存储单元一一对应;当某个数据所在的单元损坏时(由于频繁读写的是数据所在的单元,所以首先考虑这种情况),则改用备用区某单元(通过改写对应的数据分配表单元存储的地址,使其指向改用的备用区某单元来实现),以后每次读写都指向新的存储单元,这样就跳过了损坏的单元;若要避免对相同单元频繁擦写,则每过一段合适的时间对整个数据分配表进行更新,或对整个E2PROM空间重新划分;判断某存储单元是否损坏的方法是,对该单元进行写操作之后立刻回读,若读写内容一致则该单元正常,否则已损坏;备用区的首地址存储该区域未使用部分的开始地址,以方便数据单元损坏时使用该单元,每当有数据单元损坏后使用了该单元,备用区首地址则指向下一单元。

这样,E2PROM中保存数据区域的损坏单元都能被跳过,只有保存地址的地址分配表和备用区首地址单元的损坏对系统的正常运行有致命的影响。而备用区首地址单元的写频率是最高的,保存数据的单元每出现一个损坏单元就要对其改写一次。因此,理论上当有100万个单元(1MB)因写操作损坏时,备用区首地址单元的寿命也即耗尽。但目前较常用的E2PROM芯片的容量最大也就若干MB,如果出现近100万个损坏单元,芯片早已应该报废。所以,理论上该方法已足够可靠。

3 系统总体设计

本文E2PROM存储芯片选用ATMEL公司的AT24C01,FPGA芯片采用Altera公司的CycIone II系列。

系统的总体框图如图1所示。系统主要分为FPGA部分和E2PROM部分。FPGA接受外界控制信号、数据及时钟等信号,并对E2PROM进行控制。E2PROM根据FPGA的控制信号进行相应的读写操作。

AT24C01内部数据单元组织方式为128x8位。将其分为三部分:前48x8位作为地址分配表区,地址范围0000000~0101111;中间32x8位作为备用区,地址范围为0110000~1001111;后48x8位为数据区。地址范围为1010000~1111111。地址空间划分说明如图2所示。

本文的E2PROM控制器在FPGA中用VHDL语言进行设计。用有限状态机技术实现。

图2系统总体结构

4 AT24C01 E2PROM读写控制原理

4.1 I2C总线工作原理

AT24C01采用简单的双向两线串行总线PC总线标准。I2c总线由数据线SDA和时钟线SCL构成,可发送和接收数据。其数据传输过程中共有四种基本类型信号:

(1)开始信号,当SCL为高电平时SDA由高电平向低电平跳变,表明传送数据开始;

(2)结束信号,当SCL为高电平时SDA由低电平向高电平跳变,表明传送数据结束;

(3)数据信号。即SDA线上传输的数据,当SCL为高电平时有效,不允许改变,当SCL为低电平无效。允许改变;

(4)应答信号,接收端正确接收到8位数据后,向发送端发出特定的低电平脉冲,表示已收到数据。

4.2两线E2PROM字节读写工作原理

两线E2PROM的写操作方式分为字节写和按页写。读操作方式分为字节读和顺序读。本文仅使用以最基本的读写方式——字节写和字节读方式为例说明设计过程,其它读写方式的设计过程与此相似。

(1)E2PROM的字节写操作。在控制器对E2PROM发送启动信号之后,紧接着发送一个8位的写控制字。控制字的组成包括4位12C特征码(E2PROM一般为“1010”)、3位芯片地址码(单片E2PROM为“000”)以及1位读写状态位(读操作为‘1’,写操作为‘0’)。 E2PROM正确接收到写控制字后,发送l位低电平的应答信号。控制器紧接着发送E2PROM存储单元地址和要写入的数据。E2PROM每次止确地接收到一个字节的数据都要发送一个应答信号返回给控制器。随后控制器发送停止信号,对E2PROM写一个字节的操作完成。

(2)E2PROM的字节读操作。E2PROM的读操作包括写地址和读数据两个阶段。控制器首先发送一个启动信号和8位的写控制字节(读些状态位R/W=‘0’),E2PROM正确接收到控制字后发送1位低电平的应答信号,之后控制器发送8位的E2PROM地址。通过写操作设置E2PROM存储单元地址。接着控制器再发送一个启动信号和读控制字节(此时R/W=‘1’),启动读操作,E2PROM收到信息后发送1位的低电平应答信号,然后将指定单元的数据发送到SDA线上,控制器正确收到数据后返回一个低电平的应答信号给E2PROM,随后发送停止信号,字节读操作结束。

5 可靠性E2PROM控制器设计

本文用VHDL语言,以有限状态机的方式在实现FPGA对E2PROM的控制。对于一般的读写过程,只需要7个基本状态便可实现,即:空闲,开始。写控制字,写地址,写数据,读数据,停止。

但由于本文的读写过程较为复杂,虽然基本的状态仍为这7个,但如果仅用这7种状态,会使得程序流程异常繁杂。考虑到每次读写中都首先要从地址分配表中读出数据地址,然后才在数据地址读写数据,这两个阶段虽然过程相近,但状态转换条件不同,将它们分离开来能使状态转换和程序流程更清晰。所以本系统对这两个阶段的状态分开实现,用14个状态实现整个读写过程,即:S0空闲,S1开始,S2控制字(写操作)。s3写地址,s4开始,S5控制字(读操作),S6读数据(从地址分配表中读取数据地址),S7结束(查表结束,此后为数据读写过程),S8开始,S9写控制字,S10写地址,Sll写数据,S12读数据,S13停止。其中Sl到S7为查地址分配表的过程.S8到S13为进行数据读写的过程。整个过程的状态转换过程如图3所示。

本文设计的E2PROM采用的方法需要首先对E2PROM芯片进行格式化,即对整个E2PROM存储空间进行划分,建立地址分配表。这个过程为基本写操作的循环,可以嵌入系统读写过程中。

因此,整个系统共有3个主要进程:时钟产生进程,状态转换进程和状态控制进程。

1、时钟产生进程,负责产生满足系统所需的各种时钟,主要是E2PROM的SCL,并且为了方便方便按照时钟要求读写数据,将SCL周期内划分为4个子周期。工作在1.8V、2.5V和2.7v时,E2PROM的工作频率为100KHz。本文采用100M的外

部晶振产生外部时钟clk,则需进行1000分频来产生E2PROM所需的SCL时钟信号。该进程如下:

CLK_GEN:PROCESS(clk)

BEGIN

IF clk’EVENT AND clk=’1’THEN

IF ncount=499 THEN

ncount《=0;sclsig《=NOT sclsig;

ELSE ncount《=ncount+l;

END IF:

END IF;

sel《=selsig;

END PROCESS;

2、状态转换进程,负责在适当的时机将状态机转入下一状态,代码如下:

STATE_TRANS:PROCESS(sclsig)

BEGIN

IF sclsig’EVENT AND sclsig=’0’THEN

curstate《=nextstate;

END IF;

END PROCESS

3、状态控制进程,负责在格式化及读写过程中各种信号的设置,这是整个系统最复杂也是最核心的部分,其本质就是系统状态转换图的VHDL代码实现。但其过程相当繁琐,在这里只能将这个进程代码的主要部分展示出来,然后对各状态的具体操作进行适当的说明。

本进程的主要代码如下:

STATE_CTR:PROCESS(clk)

BEGIN

IF clk’EVENT AND clk=’1’THEN

CASE curstate IS

WHEN S0=》

IF rwf

THEN nextstate《=S1;

END IF;

。。。。。。

WHEN S13=》

IF sclsig=O AND ncount=499

THEN sda《=’0’:

ELSIF sclsig=1 AND nclk=124

THEN sda《=’1’;nextstate《=sO;

END IF;

END CASE;

END IF;

END PROCESS;

图3系统状态转换图

对各状态的说明如下:

S0:空闲状态,检测rwf信号输入。如果为格式化命令(“ll”)则转入S8,如果为读操作或写操作命令(分别为“0l”和“10”)则转入S1。

S1:产生开始信号。完成后转入入S2。

S2:向SDA线输出写操作控制字。完成后转入S3。

S3:写地址(由外部输入)。即所需操作的数据单元对应在地址分配表中的地址。完成后转入S4。

S4:产生开始信号。完成后转入S5。

S5:向SDA线读操作控制字。完成后转入S6。

S6:读取数据,此处为所需数据所在的地址。完成后转入s7。

S7:产生结束信号。完成后转入S8。至此查表过程结束,此后为实际读写过程。

s8:产生开始信号。完成后转入S9。

S9:输出控制字。如果在读操作过程中且为第二次进入该状态,则向SDA线输出读操作控制字,完成后转入S12;否则输出写操作控制字,完成后转入S1O。

S1O:写地址(即S6状态中读取的数据)。完成后,如果为读操作则转入S11,否则转入S8。

S11:写数据,向SDA线写外部提供的数据。完成后转入S13。

S12:读数据,完成后转入S13。

S13:产生结束信号。如果处于读操作结束状态,则转入SO;如果处于写操作结束状态并且没有对数据回读以检查所写单元是否正常。则转入S6进行回读;如果处于写操作回读结束状态,无误则转入S0,有误则转入S1读备用区首地址;如果是对备用区写操作回读有误,则地址加l后进入S6写下一地址,直至能正确写入,之后将地址加1写入备用区首地址.然后转入S0;如果处于格式化过程中,则地址加1后转入S8,直到格式化结束转入S0。

6 仿真结果和结论

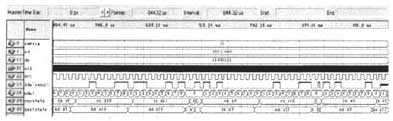

图4写操作功能仿真的部分波形

图5读操作功能仿真的部分波形

在Quartos II软件中对本文设计的E2PROM控制器进行了功能仿真。写操作和读操作功能仿真的部分波形如图4和图5所示。根据仿真波形可知,其结果与预期基本一致。在工程中的成功应用也证明了本设计的正确性。

本文创新点:对E2PROM存储空间进行适当的划分,以类似指针的方式进行读写操作,减少了系统对特定存储单元的依赖,提高了系统的可靠性。

1 E2PROM介绍及其应用现状

E2PROM(Electically Erasable Programmable Read-Only Memory),即电可擦除只读存储器。它是一种非易欠性存储器,掉电后数据依然存在(一般可保存长达100年),读写耗电极低,擦写时只需相应的电信号即可,控制方式简单,体积小巧。价格便宜,被广泛应用于对数据存储安全性及可靠性要求较高的场合,如各类IC卡、智能家电、工业仪器仪表等。

但E2PROM使用寿命有限,一般为可擦写100万次,即某一位由1写为0或由0写为1的次数为100万次。一般的系统往往只对若干同定单元进行频繁的读写,很容易造成这些单元的损坏。而常用的E2PROM存储系统,只要某一个存储单元损坏,即使其他绝大部分单元都是完好的,也只能将整个E2PROM芯片报废。这既是对资源的浪费,也是系统正常运行的潜在风险。

为了延长E2PROM芯片的寿命,提高存储系统的可靠性,本文提出一种较可靠的E2PROM控制器设计方法,并在FPGA中用VHDL进行了实现。

2 本文E2PROM控制器的工作原理

在很多领域的存储系统中,可靠性对系统安全至关重要。为了避免系统出错,并延长系统的寿命,本文在适当牺牲存储效率的前提下,着重考虑提高存储系统的可靠性。

E2PROM存储器存储单元的损坏主要是由频繁的写操作造成的。若要解决问题,首先耍避免对同一单元进行频繁的擦写,降低存储单元损坏的可能;其次当某些单元损坏时,读写控制器应该能够跳过这些损坏的单元,保证系统能继续正常工作。本文设计的E2PROM控制器具有这两个方面的功能。

本文的设计思想是,将整个EzpROM地址空间划分为地址分配表区、备用区和数据区,如图1所示。

图1 E2PROM地址空间划分

在地址分配表区中只存储所有数据区或备用区存储单元的地址,初始时与数据区的每个存储单元一一对应;当某个数据所在的单元损坏时(由于频繁读写的是数据所在的单元,所以首先考虑这种情况),则改用备用区某单元(通过改写对应的数据分配表单元存储的地址,使其指向改用的备用区某单元来实现),以后每次读写都指向新的存储单元,这样就跳过了损坏的单元;若要避免对相同单元频繁擦写,则每过一段合适的时间对整个数据分配表进行更新,或对整个E2PROM空间重新划分;判断某存储单元是否损坏的方法是,对该单元进行写操作之后立刻回读,若读写内容一致则该单元正常,否则已损坏;备用区的首地址存储该区域未使用部分的开始地址,以方便数据单元损坏时使用该单元,每当有数据单元损坏后使用了该单元,备用区首地址则指向下一单元。

这样,E2PROM中保存数据区域的损坏单元都能被跳过,只有保存地址的地址分配表和备用区首地址单元的损坏对系统的正常运行有致命的影响。而备用区首地址单元的写频率是最高的,保存数据的单元每出现一个损坏单元就要对其改写一次。因此,理论上当有100万个单元(1MB)因写操作损坏时,备用区首地址单元的寿命也即耗尽。但目前较常用的E2PROM芯片的容量最大也就若干MB,如果出现近100万个损坏单元,芯片早已应该报废。所以,理论上该方法已足够可靠。

3 系统总体设计

本文E2PROM存储芯片选用ATMEL公司的AT24C01,FPGA芯片采用Altera公司的CycIone II系列。

系统的总体框图如图1所示。系统主要分为FPGA部分和E2PROM部分。FPGA接受外界控制信号、数据及时钟等信号,并对E2PROM进行控制。E2PROM根据FPGA的控制信号进行相应的读写操作。

AT24C01内部数据单元组织方式为128x8位。将其分为三部分:前48x8位作为地址分配表区,地址范围0000000~0101111;中间32x8位作为备用区,地址范围为0110000~1001111;后48x8位为数据区。地址范围为1010000~1111111。地址空间划分说明如图2所示。

本文的E2PROM控制器在FPGA中用VHDL语言进行设计。用有限状态机技术实现。

图2系统总体结构

4 AT24C01 E2PROM读写控制原理

4.1 I2C总线工作原理

AT24C01采用简单的双向两线串行总线PC总线标准。I2c总线由数据线SDA和时钟线SCL构成,可发送和接收数据。其数据传输过程中共有四种基本类型信号:

(1)开始信号,当SCL为高电平时SDA由高电平向低电平跳变,表明传送数据开始;

(2)结束信号,当SCL为高电平时SDA由低电平向高电平跳变,表明传送数据结束;

(3)数据信号。即SDA线上传输的数据,当SCL为高电平时有效,不允许改变,当SCL为低电平无效。允许改变;

(4)应答信号,接收端正确接收到8位数据后,向发送端发出特定的低电平脉冲,表示已收到数据。

4.2两线E2PROM字节读写工作原理

两线E2PROM的写操作方式分为字节写和按页写。读操作方式分为字节读和顺序读。本文仅使用以最基本的读写方式——字节写和字节读方式为例说明设计过程,其它读写方式的设计过程与此相似。

(1)E2PROM的字节写操作。在控制器对E2PROM发送启动信号之后,紧接着发送一个8位的写控制字。控制字的组成包括4位12C特征码(E2PROM一般为“1010”)、3位芯片地址码(单片E2PROM为“000”)以及1位读写状态位(读操作为‘1’,写操作为‘0’)。 E2PROM正确接收到写控制字后,发送l位低电平的应答信号。控制器紧接着发送E2PROM存储单元地址和要写入的数据。E2PROM每次止确地接收到一个字节的数据都要发送一个应答信号返回给控制器。随后控制器发送停止信号,对E2PROM写一个字节的操作完成。

(2)E2PROM的字节读操作。E2PROM的读操作包括写地址和读数据两个阶段。控制器首先发送一个启动信号和8位的写控制字节(读些状态位R/W=‘0’),E2PROM正确接收到控制字后发送1位低电平的应答信号,之后控制器发送8位的E2PROM地址。通过写操作设置E2PROM存储单元地址。接着控制器再发送一个启动信号和读控制字节(此时R/W=‘1’),启动读操作,E2PROM收到信息后发送1位的低电平应答信号,然后将指定单元的数据发送到SDA线上,控制器正确收到数据后返回一个低电平的应答信号给E2PROM,随后发送停止信号,字节读操作结束。

5 可靠性E2PROM控制器设计

本文用VHDL语言,以有限状态机的方式在实现FPGA对E2PROM的控制。对于一般的读写过程,只需要7个基本状态便可实现,即:空闲,开始。写控制字,写地址,写数据,读数据,停止。

但由于本文的读写过程较为复杂,虽然基本的状态仍为这7个,但如果仅用这7种状态,会使得程序流程异常繁杂。考虑到每次读写中都首先要从地址分配表中读出数据地址,然后才在数据地址读写数据,这两个阶段虽然过程相近,但状态转换条件不同,将它们分离开来能使状态转换和程序流程更清晰。所以本系统对这两个阶段的状态分开实现,用14个状态实现整个读写过程,即:S0空闲,S1开始,S2控制字(写操作)。s3写地址,s4开始,S5控制字(读操作),S6读数据(从地址分配表中读取数据地址),S7结束(查表结束,此后为数据读写过程),S8开始,S9写控制字,S10写地址,Sll写数据,S12读数据,S13停止。其中Sl到S7为查地址分配表的过程.S8到S13为进行数据读写的过程。整个过程的状态转换过程如图3所示。

本文设计的E2PROM采用的方法需要首先对E2PROM芯片进行格式化,即对整个E2PROM存储空间进行划分,建立地址分配表。这个过程为基本写操作的循环,可以嵌入系统读写过程中。

因此,整个系统共有3个主要进程:时钟产生进程,状态转换进程和状态控制进程。

1、时钟产生进程,负责产生满足系统所需的各种时钟,主要是E2PROM的SCL,并且为了方便方便按照时钟要求读写数据,将SCL周期内划分为4个子周期。工作在1.8V、2.5V和2.7v时,E2PROM的工作频率为100KHz。本文采用100M的外

部晶振产生外部时钟clk,则需进行1000分频来产生E2PROM所需的SCL时钟信号。该进程如下:

CLK_GEN:PROCESS(clk)

BEGIN

IF clk’EVENT AND clk=’1’THEN

IF ncount=499 THEN

ncount《=0;sclsig《=NOT sclsig;

ELSE ncount《=ncount+l;

END IF:

END IF;

sel《=selsig;

END PROCESS;

2、状态转换进程,负责在适当的时机将状态机转入下一状态,代码如下:

STATE_TRANS:PROCESS(sclsig)

BEGIN

IF sclsig’EVENT AND sclsig=’0’THEN

curstate《=nextstate;

END IF;

END PROCESS

3、状态控制进程,负责在格式化及读写过程中各种信号的设置,这是整个系统最复杂也是最核心的部分,其本质就是系统状态转换图的VHDL代码实现。但其过程相当繁琐,在这里只能将这个进程代码的主要部分展示出来,然后对各状态的具体操作进行适当的说明。

本进程的主要代码如下:

STATE_CTR:PROCESS(clk)

BEGIN

IF clk’EVENT AND clk=’1’THEN

CASE curstate IS

WHEN S0=》

IF rwf

THEN nextstate《=S1;

END IF;

。。。。。。

WHEN S13=》

IF sclsig=O AND ncount=499

THEN sda《=’0’:

ELSIF sclsig=1 AND nclk=124

THEN sda《=’1’;nextstate《=sO;

END IF;

END CASE;

END IF;

END PROCESS;

图3系统状态转换图

对各状态的说明如下:

S0:空闲状态,检测rwf信号输入。如果为格式化命令(“ll”)则转入S8,如果为读操作或写操作命令(分别为“0l”和“10”)则转入S1。

S1:产生开始信号。完成后转入入S2。

S2:向SDA线输出写操作控制字。完成后转入S3。

S3:写地址(由外部输入)。即所需操作的数据单元对应在地址分配表中的地址。完成后转入S4。

S4:产生开始信号。完成后转入S5。

S5:向SDA线读操作控制字。完成后转入S6。

S6:读取数据,此处为所需数据所在的地址。完成后转入s7。

S7:产生结束信号。完成后转入S8。至此查表过程结束,此后为实际读写过程。

s8:产生开始信号。完成后转入S9。

S9:输出控制字。如果在读操作过程中且为第二次进入该状态,则向SDA线输出读操作控制字,完成后转入S12;否则输出写操作控制字,完成后转入S1O。

S1O:写地址(即S6状态中读取的数据)。完成后,如果为读操作则转入S11,否则转入S8。

S11:写数据,向SDA线写外部提供的数据。完成后转入S13。

S12:读数据,完成后转入S13。

S13:产生结束信号。如果处于读操作结束状态,则转入SO;如果处于写操作结束状态并且没有对数据回读以检查所写单元是否正常。则转入S6进行回读;如果处于写操作回读结束状态,无误则转入S0,有误则转入S1读备用区首地址;如果是对备用区写操作回读有误,则地址加l后进入S6写下一地址,直至能正确写入,之后将地址加1写入备用区首地址.然后转入S0;如果处于格式化过程中,则地址加1后转入S8,直到格式化结束转入S0。

6 仿真结果和结论

图4写操作功能仿真的部分波形

图5读操作功能仿真的部分波形

在Quartos II软件中对本文设计的E2PROM控制器进行了功能仿真。写操作和读操作功能仿真的部分波形如图4和图5所示。根据仿真波形可知,其结果与预期基本一致。在工程中的成功应用也证明了本设计的正确性。

本文创新点:对E2PROM存储空间进行适当的划分,以类似指针的方式进行读写操作,减少了系统对特定存储单元的依赖,提高了系统的可靠性。

举报

举报

举报

举报