现代通讯电子设备的抗干扰测试已经成为必须的测试项目,主要的干扰类型为噪声干扰。在通信信道测试和电子对抗领域里,噪声始终是最基本、最常用的干扰源之一。如何产生稳定和精确的噪声信号已经成为一个重要的研究领域。其中,带限白噪声信号时间相关性小,目前应用最广泛。现有的硬件高斯白噪声发生器通常分为物理噪声发生器和数字噪声发生器两类,数字噪声发生器虽然没有物理噪声发生器的精度高,但是实现威廉希尔官方网站

较为简单,易于应用。

FPGA技术的发展,提高了硬件噪声发生器的速度和性能,相比基于软件实现的噪声发生器,展现出更大的优势。本文设计的高斯白噪声发生器采用FPGA的方式实现,输出的基带白噪声带宽可调,范围为1~66 MHz,步进3 MHz,幅度8位可调,同时可产生正弦波、三角波、锯齿波、方波等函数波,通过更改现场可编程器件的配置波形数据也可产生其他复杂函数波形。

1 高斯白噪声发生器原理

本文所述的高斯白噪声发生器如图1所示。

首先,在现场可编程门阵列(Field Programmable Gate Array,FPGA)平台上以一个统一的时钟速度(以后称之为噪声发生速度,即f0)生成高速m序列伪随机码流,对该序列进行有限冲击响应(Finite Impulse Response,FIR)数字滤波处理,得到带限白噪声数字序列,同时在FPGA中实现直接数字综合(Direct Digital Synthesizer,DDS)算法,产生正弦数字序列,并与噪声序列合成;其次,将以上得到的数字序列通过高速数/模转换器(Digital Analog Converter,DAC)转换为模拟噪声信号;再次,通过LC低通滤波器以及放大器转换为模拟带限白噪声和正弦信号,该信号即为基带白噪声信号。下面对涉及的基本算法进行分析和仿真。

高斯白噪声发生方法中涉及伪随机码发生算法、数字滤波算法和正弦波发生算法。本文详细论述这几种算法,及其在FPGA上的实现方法,分析了各种算法在频域上的频谱特性。

2 高斯白噪声发生器算法分析

2.1 伪随机码发生算法

伪随机码(Pseudo-random Sequence,PS)的性能指标直接影响产生白噪声的随机性,是系统设汁的关键。通常产生伪随机码的威廉希尔官方网站

为一反馈移存器,分为线性和非线性两类。前者产生周期最长的二进制数字序列为最大长度线性反馈移存器序列,简称m序列。本文采用的就是m序列伪随机码。

产生m序列的反馈移存器的递推方程可以写为:

它给出了移位输入an与移位前各级状态的关系。

特征多项式写为:

它决定了移位寄存器的反馈连接和序列的结构。

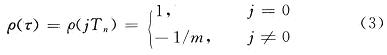

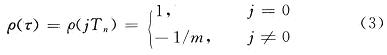

m序列的自相关函数可表示为:

式(3)为一个周期(m=2n-1)内的函数,其中Tn为伪随机噪声码元的宽度。整个时域的自相关函数的周期为m=2n-1。信号的自相关函数与功率谱密度构成一对傅里叶变换,因此m序列的自相关函数经过傅里叶变换,其功率谱密度为:

假定零频处的功率为1,那么功率下降为0.5处的频率为:

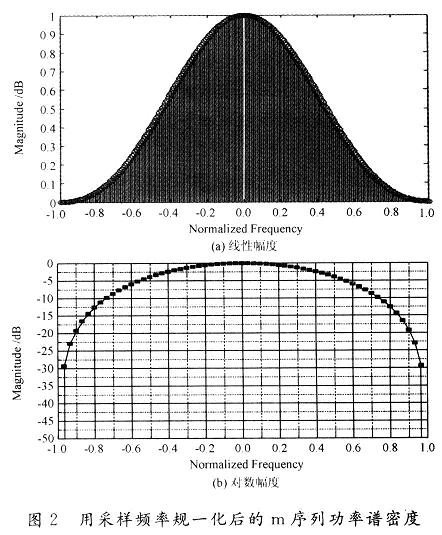

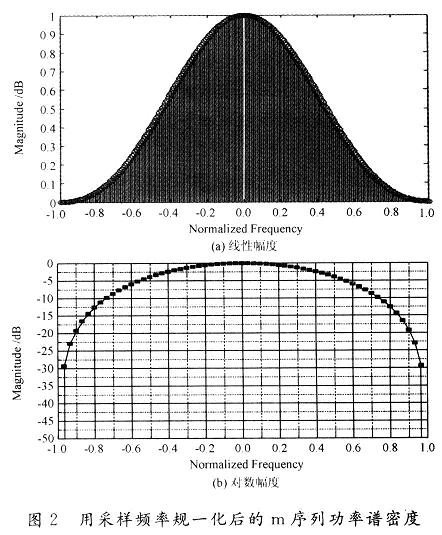

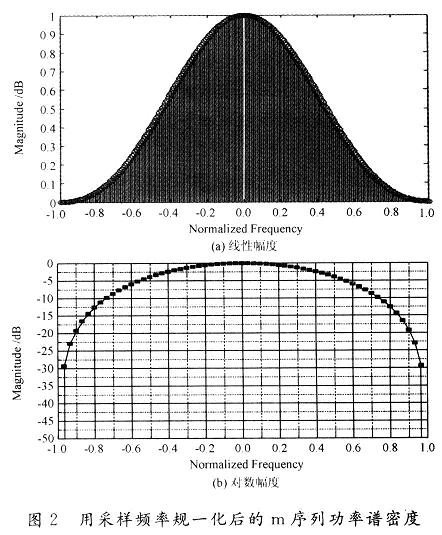

其典型的功率谱密度如图2所示。

由图2可以看出,m序列的功率谱密度的包络是[(sin x)/x]2形的,它约在伪随机序列基本时钟频率的45%带宽内具有均匀功率谱密度,所以用滤波器滤除该频带内的信号就可以近似看作带限白噪声。m序列的均衡性、游程分布、自相关特性和功率谱与随机序列的基本性质很相似,所以m序列属于伪噪声的序列或伪随机序列。

2.2 FIR数字滤波算法

m序列的功率谱是固定的,要生成带宽可调的数字噪声序列需要对m序列进行低通数字滤波,本文采用的是FIR数字滤波器。

由Lindeberg定理可知,设有独立随机变量序列

该定理证明了由大量微小且独立的随机因素引起,并积累而成的变量,必是一个正态随机变量。FIR滤波器的单位冲激响应为h(n),0≤n≤N一1,输入函数为x(i),则输出函数y(i)可以写为:

该算法需要N次相乘,N-1次累加。为了产生带宽小于5 MHz高质量的数字噪声序列,需要构建窄通带、通带阻带转换迅速的低通滤波器,对此仅仅增加单级FIR滤波的冲激相应长度n是不够的,对此本文采用了多级FIR数字滤波的方法。为了使得多路多级FIR滤波器能够在常用FPGA平台上实现,对FIR数字滤波模型进行算法优化,以节约所需逻辑单元资源是很有必要的。

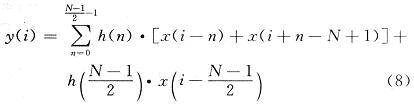

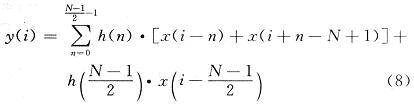

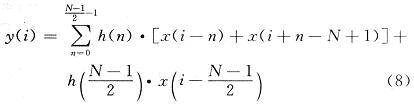

采用单位冲激相应h(n)为偶函数的FIR滤波器,并取阶数N为奇数,则式(6)可以化简为:

采用该方法可以将FIR算法中乘的次数减半,总计算量减为(N+1)/2次相乘,N-2次累加,极大地节省了FPGA的逻辑单元资源。FIR的滤波过程实质上就是一个延迟后加权相加的过程,即滤波输出y(i)是输入x(i)以及它的前N一1个状态的加权叠加。

2.3 DDS算法

随着数字集成威廉希尔官方网站

和微电子技术的发展,直接数字频率合成器(Direct Digital Synthesizer,DDS)逐渐体现出其具有相对带宽宽,频率转换时间短,频率分辨率高,输出相位连续,可编程及全数字化结构等优点。

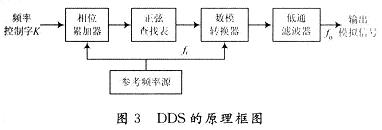

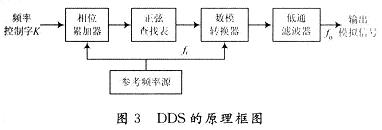

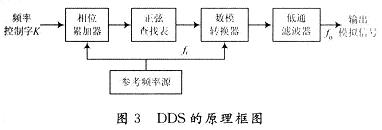

DDS的基本工作原理是根据正弦函数的产生,从相位出发,用不同的相位给出不同的电压幅度,最后滤波平滑出所需要的频率。图3是DDS的原理方框图。

参考频率源又称参考时钟源,它是一个稳定的晶体振荡器,用来同步DDS的各组成部分。相位累加器类似于一个计数器,它由多个级联的加法器和寄存器组成,在每一个参考时钟脉冲输入时,它的输出就增加一个步长的相位增量值,这样相位累加器把频率控制字K的数字变换成相位抽样来确定输出合成频率的大小。相位增量的大小随外指令频率控制字K的不同而不同,一旦给定了相位增量,输出频率也就确定了。当用这样的数据寻址时,正弦查表就把存储在相位累加器中的抽样数字值转换成近似正弦波幅度的数字量函数。以上的算法都可在FPGA内部实现。

3 实验结果

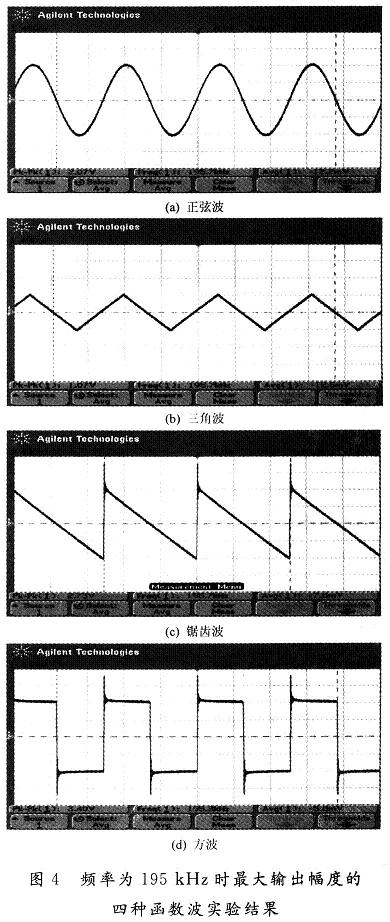

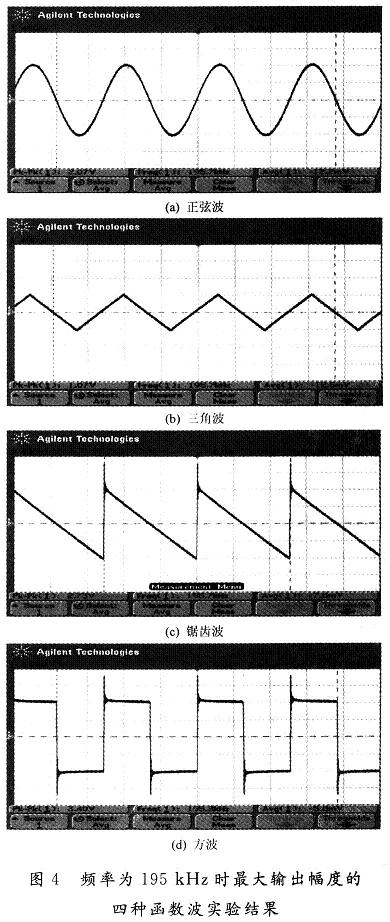

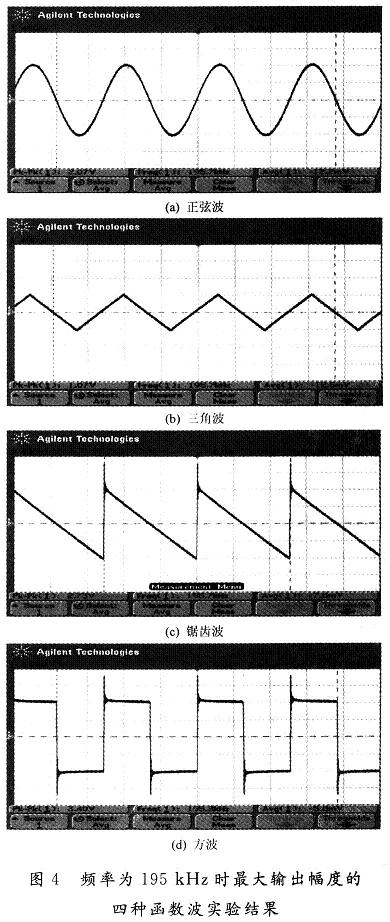

本文的FPGA平台选用Altera公司的EP2C8现场可编程逻辑器件,完成所有m序列、FIR数字滤波和DDS算法,需要FPGA 86%的逻辑单元资源和1%的RAM资源;时钟采用50MHz、稳定度为50 ppm的有源晶振,通过EP2C8内部PLL(Phase Locked Loop,锁相环)3倍频到150 MHz作为系统全局时钟;采用ADI公司的AD9731进行D/A转换,采样速度150 MSPS,10位;对AD9731输出的电流信号进行7阶LC低通滤波,然后进行放大,使得噪声信号的满幅输出都达到峰峰值3V。图4是频率为195 kHz最大输出幅度的四种函数波测试结果。

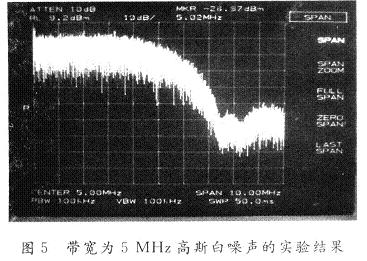

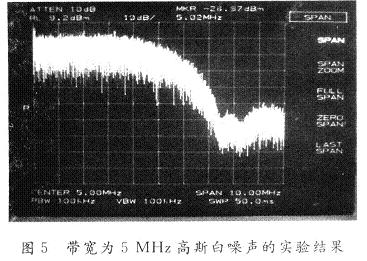

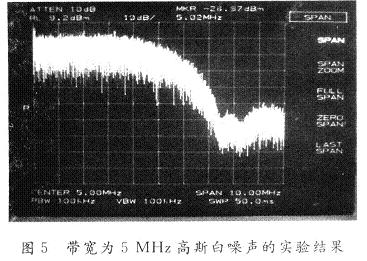

从图4可以看出,采用DDS模块,得到了正弦波、三角波、锯齿波和方波的波形。图5为该噪声和函数波发生器产生的5 MHz噪声的实验结果,图6是输出带宽为5 MHz的高斯白噪声统计直方图。

从图5和图6可以看出,基于FPGA的m序列发生算法,FIR滤波算法和DDS算法,通过数/模转换和低通放大后,本文设计的噪声发生器产生的5 MHz噪声的3 dB,带宽为4.8 MHz,带内平坦度为±1.5 dB,输出噪声的统计特性服从高斯分布,满足了设计需要。

4 结 语

设计了一种基于FPGA高斯白噪声发生器,分析了该种噪声发生器所用的m序列发生算法,FIR数字滤波算法和DDS算法,可产生带宽为3~66 MHz,步进3 MHz,幅度8位可调的高斯白噪声;采用现场可编程门阵列(FPGA)实现噪声发生器的设计,在Altera公司的QuartusⅡ软件环境下,实现了基于FPGA的m序列产生模块、FIR数字滤波器模块、DDS模块和合成模块,通过数/模转换器和低通放大,得到了可用于雷达系统和通信信道测试的高斯白噪声信号。实验结果验证了本文设计的有效性。

现代通讯电子设备的抗干扰测试已经成为必须的测试项目,主要的干扰类型为噪声干扰。在通信信道测试和电子对抗领域里,噪声始终是最基本、最常用的干扰源之一。如何产生稳定和精确的噪声信号已经成为一个重要的研究领域。其中,带限白噪声信号时间相关性小,目前应用最广泛。现有的硬件高斯白噪声发生器通常分为物理噪声发生器和数字噪声发生器两类,数字噪声发生器虽然没有物理噪声发生器的精度高,但是实现威廉希尔官方网站

较为简单,易于应用。

FPGA技术的发展,提高了硬件噪声发生器的速度和性能,相比基于软件实现的噪声发生器,展现出更大的优势。本文设计的高斯白噪声发生器采用FPGA的方式实现,输出的基带白噪声带宽可调,范围为1~66 MHz,步进3 MHz,幅度8位可调,同时可产生正弦波、三角波、锯齿波、方波等函数波,通过更改现场可编程器件的配置波形数据也可产生其他复杂函数波形。

1 高斯白噪声发生器原理

本文所述的高斯白噪声发生器如图1所示。

首先,在现场可编程门阵列(Field Programmable Gate Array,FPGA)平台上以一个统一的时钟速度(以后称之为噪声发生速度,即f0)生成高速m序列伪随机码流,对该序列进行有限冲击响应(Finite Impulse Response,FIR)数字滤波处理,得到带限白噪声数字序列,同时在FPGA中实现直接数字综合(Direct Digital Synthesizer,DDS)算法,产生正弦数字序列,并与噪声序列合成;其次,将以上得到的数字序列通过高速数/模转换器(Digital Analog Converter,DAC)转换为模拟噪声信号;再次,通过LC低通滤波器以及放大器转换为模拟带限白噪声和正弦信号,该信号即为基带白噪声信号。下面对涉及的基本算法进行分析和仿真。

高斯白噪声发生方法中涉及伪随机码发生算法、数字滤波算法和正弦波发生算法。本文详细论述这几种算法,及其在FPGA上的实现方法,分析了各种算法在频域上的频谱特性。

2 高斯白噪声发生器算法分析

2.1 伪随机码发生算法

伪随机码(Pseudo-random Sequence,PS)的性能指标直接影响产生白噪声的随机性,是系统设汁的关键。通常产生伪随机码的威廉希尔官方网站

为一反馈移存器,分为线性和非线性两类。前者产生周期最长的二进制数字序列为最大长度线性反馈移存器序列,简称m序列。本文采用的就是m序列伪随机码。

产生m序列的反馈移存器的递推方程可以写为:

它给出了移位输入an与移位前各级状态的关系。

特征多项式写为:

它决定了移位寄存器的反馈连接和序列的结构。

m序列的自相关函数可表示为:

式(3)为一个周期(m=2n-1)内的函数,其中Tn为伪随机噪声码元的宽度。整个时域的自相关函数的周期为m=2n-1。信号的自相关函数与功率谱密度构成一对傅里叶变换,因此m序列的自相关函数经过傅里叶变换,其功率谱密度为:

假定零频处的功率为1,那么功率下降为0.5处的频率为:

其典型的功率谱密度如图2所示。

由图2可以看出,m序列的功率谱密度的包络是[(sin x)/x]2形的,它约在伪随机序列基本时钟频率的45%带宽内具有均匀功率谱密度,所以用滤波器滤除该频带内的信号就可以近似看作带限白噪声。m序列的均衡性、游程分布、自相关特性和功率谱与随机序列的基本性质很相似,所以m序列属于伪噪声的序列或伪随机序列。

2.2 FIR数字滤波算法

m序列的功率谱是固定的,要生成带宽可调的数字噪声序列需要对m序列进行低通数字滤波,本文采用的是FIR数字滤波器。

由Lindeberg定理可知,设有独立随机变量序列

该定理证明了由大量微小且独立的随机因素引起,并积累而成的变量,必是一个正态随机变量。FIR滤波器的单位冲激响应为h(n),0≤n≤N一1,输入函数为x(i),则输出函数y(i)可以写为:

该算法需要N次相乘,N-1次累加。为了产生带宽小于5 MHz高质量的数字噪声序列,需要构建窄通带、通带阻带转换迅速的低通滤波器,对此仅仅增加单级FIR滤波的冲激相应长度n是不够的,对此本文采用了多级FIR数字滤波的方法。为了使得多路多级FIR滤波器能够在常用FPGA平台上实现,对FIR数字滤波模型进行算法优化,以节约所需逻辑单元资源是很有必要的。

采用单位冲激相应h(n)为偶函数的FIR滤波器,并取阶数N为奇数,则式(6)可以化简为:

采用该方法可以将FIR算法中乘的次数减半,总计算量减为(N+1)/2次相乘,N-2次累加,极大地节省了FPGA的逻辑单元资源。FIR的滤波过程实质上就是一个延迟后加权相加的过程,即滤波输出y(i)是输入x(i)以及它的前N一1个状态的加权叠加。

2.3 DDS算法

随着数字集成威廉希尔官方网站

和微电子技术的发展,直接数字频率合成器(Direct Digital Synthesizer,DDS)逐渐体现出其具有相对带宽宽,频率转换时间短,频率分辨率高,输出相位连续,可编程及全数字化结构等优点。

DDS的基本工作原理是根据正弦函数的产生,从相位出发,用不同的相位给出不同的电压幅度,最后滤波平滑出所需要的频率。图3是DDS的原理方框图。

参考频率源又称参考时钟源,它是一个稳定的晶体振荡器,用来同步DDS的各组成部分。相位累加器类似于一个计数器,它由多个级联的加法器和寄存器组成,在每一个参考时钟脉冲输入时,它的输出就增加一个步长的相位增量值,这样相位累加器把频率控制字K的数字变换成相位抽样来确定输出合成频率的大小。相位增量的大小随外指令频率控制字K的不同而不同,一旦给定了相位增量,输出频率也就确定了。当用这样的数据寻址时,正弦查表就把存储在相位累加器中的抽样数字值转换成近似正弦波幅度的数字量函数。以上的算法都可在FPGA内部实现。

3 实验结果

本文的FPGA平台选用Altera公司的EP2C8现场可编程逻辑器件,完成所有m序列、FIR数字滤波和DDS算法,需要FPGA 86%的逻辑单元资源和1%的RAM资源;时钟采用50MHz、稳定度为50 ppm的有源晶振,通过EP2C8内部PLL(Phase Locked Loop,锁相环)3倍频到150 MHz作为系统全局时钟;采用ADI公司的AD9731进行D/A转换,采样速度150 MSPS,10位;对AD9731输出的电流信号进行7阶LC低通滤波,然后进行放大,使得噪声信号的满幅输出都达到峰峰值3V。图4是频率为195 kHz最大输出幅度的四种函数波测试结果。

从图4可以看出,采用DDS模块,得到了正弦波、三角波、锯齿波和方波的波形。图5为该噪声和函数波发生器产生的5 MHz噪声的实验结果,图6是输出带宽为5 MHz的高斯白噪声统计直方图。

从图5和图6可以看出,基于FPGA的m序列发生算法,FIR滤波算法和DDS算法,通过数/模转换和低通放大后,本文设计的噪声发生器产生的5 MHz噪声的3 dB,带宽为4.8 MHz,带内平坦度为±1.5 dB,输出噪声的统计特性服从高斯分布,满足了设计需要。

4 结 语

设计了一种基于FPGA高斯白噪声发生器,分析了该种噪声发生器所用的m序列发生算法,FIR数字滤波算法和DDS算法,可产生带宽为3~66 MHz,步进3 MHz,幅度8位可调的高斯白噪声;采用现场可编程门阵列(FPGA)实现噪声发生器的设计,在Altera公司的QuartusⅡ软件环境下,实现了基于FPGA的m序列产生模块、FIR数字滤波器模块、DDS模块和合成模块,通过数/模转换器和低通放大,得到了可用于雷达系统和通信信道测试的高斯白噪声信号。实验结果验证了本文设计的有效性。

举报

举报

举报

举报