1. DMA简介

直接存储器存取(DMA,Direct Memory Access)用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。无须CPU干预,数据可以通过DMA快速地移动,节省CPU资源。DMA传输本质上是一种CPU进行权力下放的方式,将一些本来需要CPU处理的繁琐事务经过交代(配置DMA)之后全权交给DMA控制器处理。DMA 传输对于高效能嵌入式系统算法和网络是很重要的。

在实现DMA传输时,是由DMA控制器直接接管总线,因此,存在着一个总线控制权转移问题。即DMA传输前,CPU要把总线控制权交给DMA控制器,而在结束DMA传输后,DMA控制器应立即把总线控制权再交回给CPU。一个完整的DMA传输过程必须经过DMA请求、DMA响应、DMA传输、DMA结束4个步骤。

2. STM32的DMA架构

STM32有两个DMA控制器,共有12个通道(DMA1有7个通道,DMA2有5个通道),每个通道专门用来管理来自于一个或多个外设对存储器访问的请求。还有一个仲裁器来协调各个DMA请求的优先权。

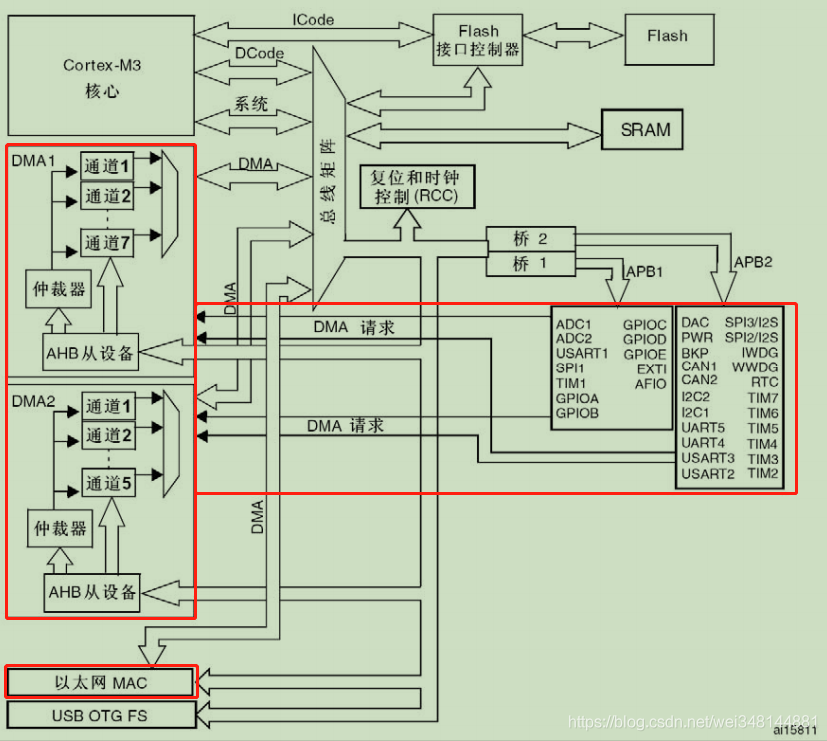

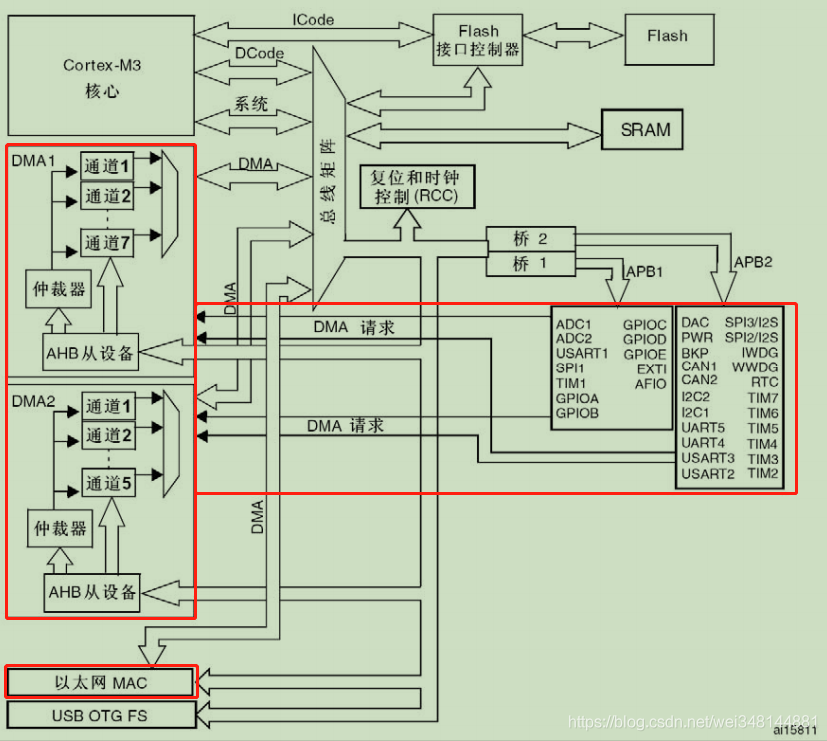

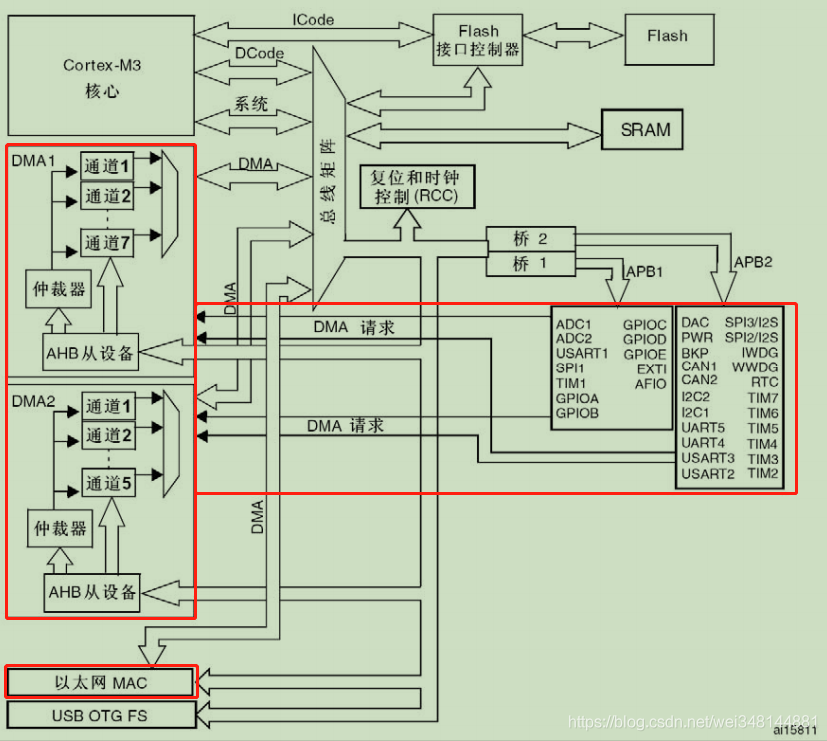

2.1 DMA框图

由框图可以看到,DMA1和DMA2、以太网MAC、USB OTG FS均为AHB下的外设(时钟源是AHB),DMA1、DMA2、以太网MAC可以以DMA方式控制总线。其中主要的DMA1和DMA2控制器的DMA请求源均为APB1和APB2下的外设。一旦DMA接管总线,就可以对总线上外设进行数据读取,闪存、SRAM、外设的SRAM、APB1、APB2和AHB外设均可作为访问的源和目标。

2.2 DMA主要特性

12个独立的可配置的通道(请求):DMA1有7个通道,DMA2有5个通道每个通道都直接连接专用的硬件DMA请求,每个通道都同样支持软件触发。这些功能通过软件来配置。

在同一个DMA模块上,多个请求间的优先权可以通过软件编程设置(共有四级:很高、高、中等和低),优先权设置相等时由硬件决定(请求0优先于请求1,依此类推) 。

独立数据源和目标数据区的传输宽度(字节、半字、全字),模拟打包和拆包的过程。源和目标地址必须按数据传输宽度对齐。

支持循环的缓冲器管理

每个通道都有3个事件标志(DMA半传输、DMA传输完成和DMA传输出错),这3个事件标志逻辑或成为一个单独的中断请求。

存储器和存储器间的传输

外设和存储器、存储器和外设之间的传输

闪存、SRAM、外设的SRAM、APB1、APB2和AHB外设均可作为访问的源和目标。

可编程的数据传输数目:最大为65535

3. DMA详解

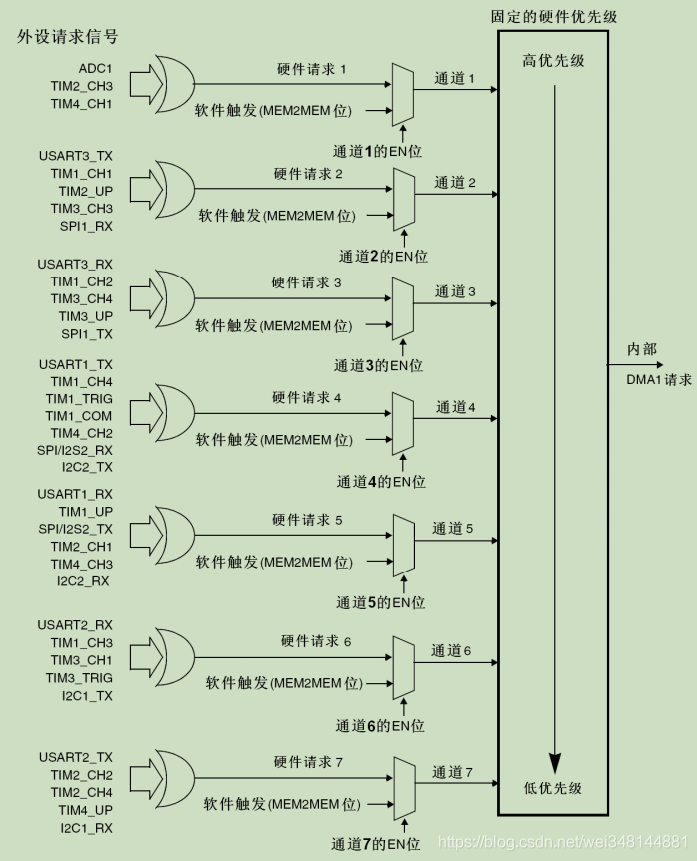

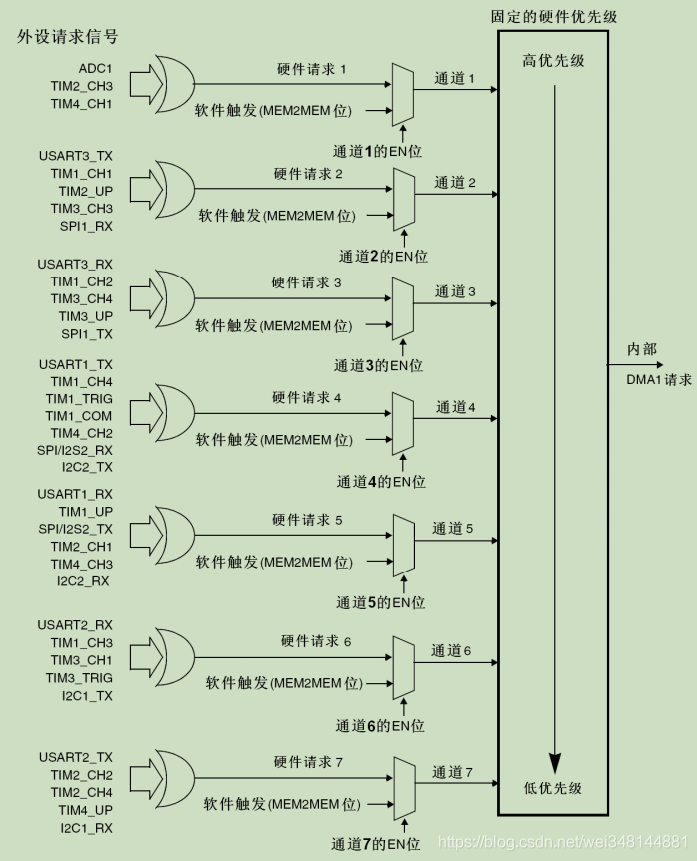

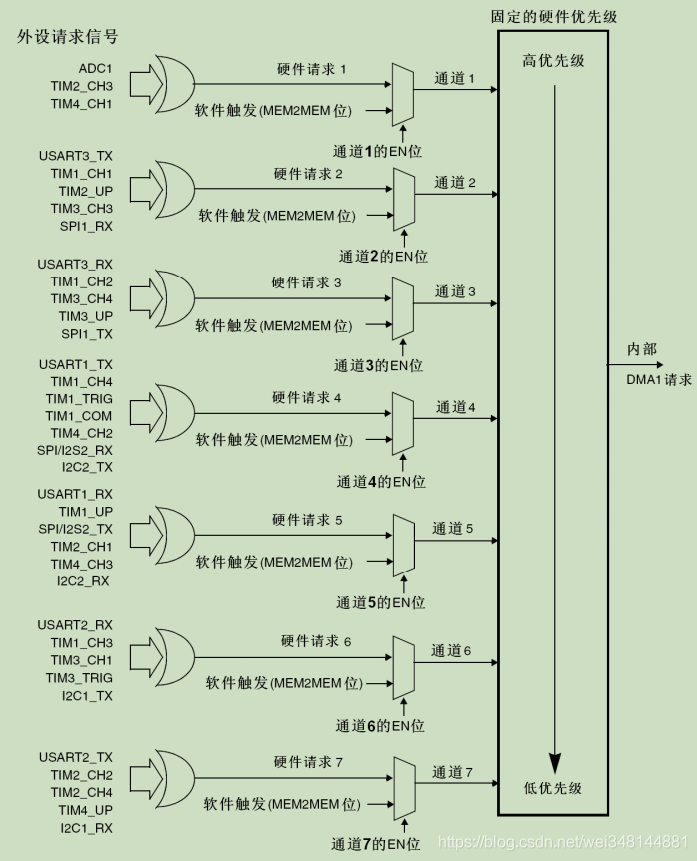

3.1 DMA请求

如框图所示,APB1和APB2下的外设向DMA控制器发送请求信号。

在发生一个事件后,外设向DMA控制器发送一个请求信号。DMA控制器通过仲裁器根据通道的优先权处理请求。当DMA控制器开始访问发出请求的外设时,立即向请求源发送一个应答信号,请求源得到应答后立即释放它的请求。

3.2 DMA通道

DMA共有12个独立可编程的通道,DMA1有7个、DMA2有5个。每个通道对应着多个不同的外设的请求,他们通过逻辑或连接到一个通道,一个通道同一时间只能接收一个外设请求。每个通道都可以在有固定地址的外设寄存器和存储器地址之间执行DMA传输。DMA传输的数据量是可编程的,最大达到65535。

DMA1通道:

DMA2通道:

3.3 DMA仲裁器

这么多通道,肯定要有优先级来进行管理,仲裁器根据通道请求的优先级来启动外设/存储器的访问。每个通道的优先权可以在DMA_CCRx寄存器中设置,有4个等级:

最高优先级

高优先级

中等优先级

低优先级

优先响应高优先级的通道,如果2个请求通道有相同的软件优先级,则较低编号的通道比较高编号的通道有较高的优先权。

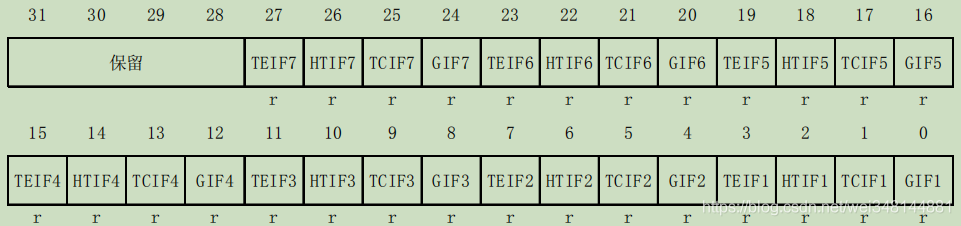

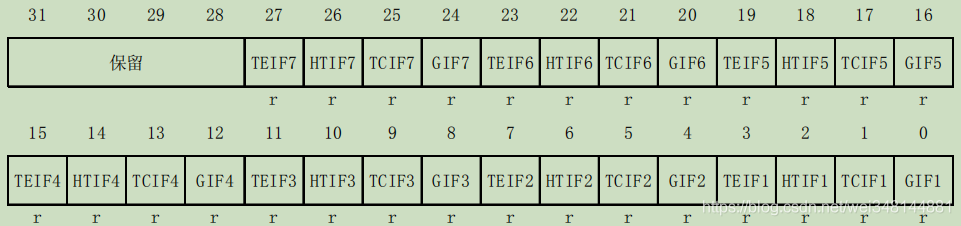

3.4 DMA中断

每个DMA通道都可以在DMA传输过半、传输完成和传输错误时产生中断。为应用的灵活性考虑,通过设置寄存器的不同位来打开这些中断。

DMA中断请求:

3.5 传输方向

DMA有三个传输方向,外设到存储器、存储器到外设、存储器到存储器。

3.6 DMA循环模式

传送一次之后,又恢复第一次的配置,继续进行传输。

循环模式用于处理循环缓冲区和连续的数据传输(如ADC的扫描模式)。在DMA_CCRx寄存器中的CIRC位用于开启这一功能。当启动了循环模式,数据传输的数目变为0时,将会自动地被恢复成配置通道时设置的初值,DMA操作将会继续进行。当通道配置为非循环模式时,传输结束后(即传输计数变为0)将不再产生DMA操作。要开始新的DMA传输,需要在关闭DMA通道的情况下,在DMA_CNDTRx寄存器中重新写入传输数目。

3.7 地址增量模式

当传输的数据不止一个时,需要根据起始地址、数据宽度对后来的数据的读写地址进行指定,这就有了地址增量模式。通过设置DMA_CCRx寄存器中的PINC和MINC标志位,外设和存储器的指针在每次传输后可以有选择地完成自动增量。当设置为增量模式时,下一个要传输的地址将是前一个地址加上增量值,增量值取决与所选的数据宽度为1、2或4。第一个传输的地址是存放在DMA_CPARx /DMA_CMARx寄存器中地址。在传输过程中,这些寄存器保持它们初始的数值,软件不能改变和读出当前正在传输的地址。

4. DMA寄存器

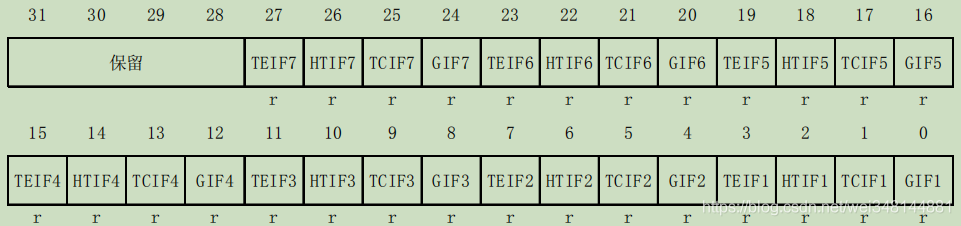

4.1 DMA中断状态寄存器(DMA_ISR)

GIFx:通道x的全局中断标志(x = 1 … 7) (Channel x global interrupt flag)

如果通道x发生了下方三个中断(TCIFx、HTIFx、TEIFx)任意一个,该位就被置位。

TCIFx:通道x的传输完成标志(x = 1 … 7) (Channel x transfer complete flag),完成置1。

HTIFx:通道x的半传输标志(x = 1 … 7) (Channel x half transfer flag),完成置1。

TEIFx:通道x的传输错误标志(x = 1 … 7) (Channel x transfer error flag),出错置1。

在DMA_IFCR寄存器的相应位写入’1’可以清除DMA_ISR对应的标志位。

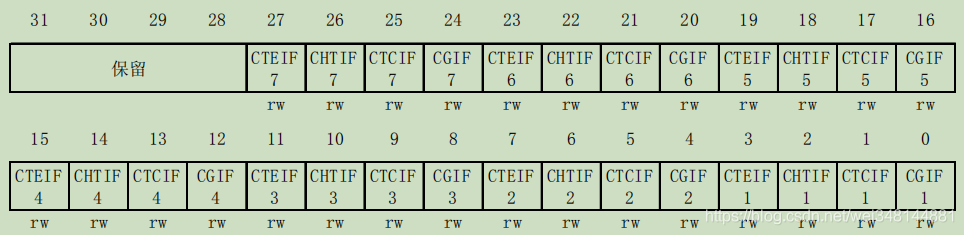

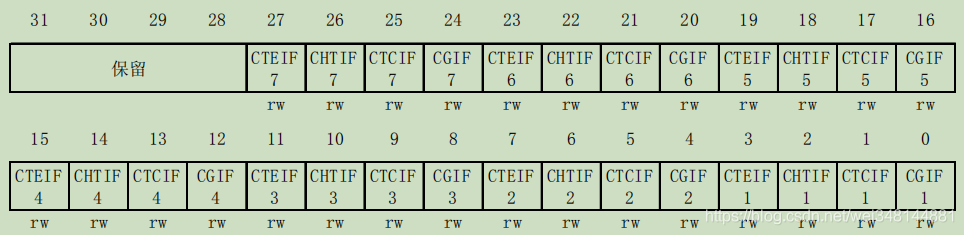

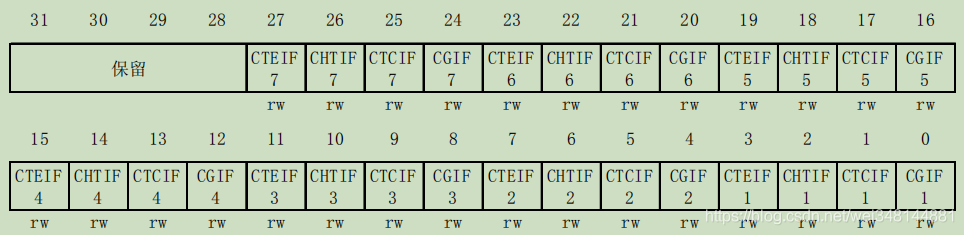

4.2 DMA中断标志清除寄存器(DMA_IFCR)

该寄存器对上述中断状态寄存器DMA_ISR清除相应的标志位。写1清除,写0无效。

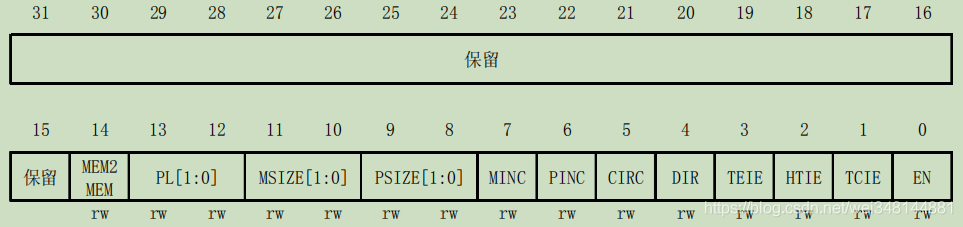

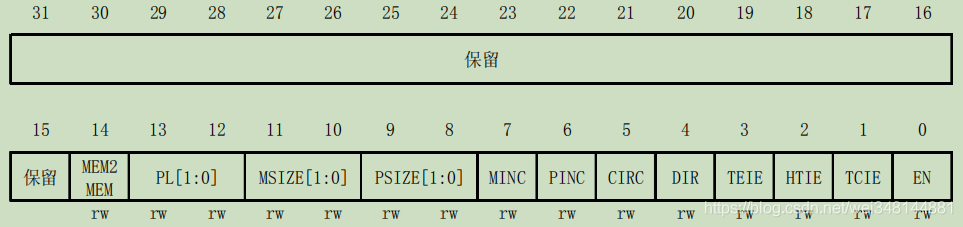

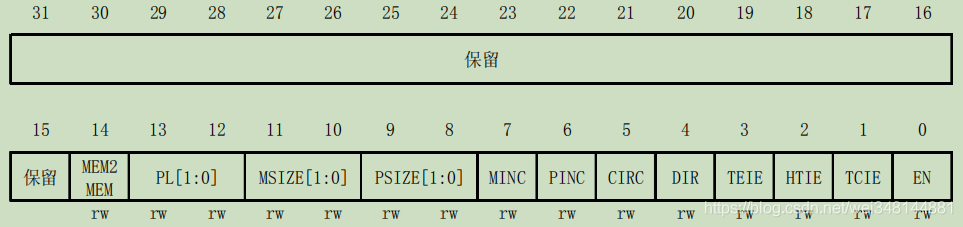

4.3 DMA通道x配置寄存器(DMA_CCRx)(x = 1…7)

EN:通道开启 (Channel enable)

0:通道不工作

1:通道开启

TEIE/HTIE/TCIE:允许传输错误/半传输/传输完成中断 (Transfer error interrupt enable)

0:禁止TE/HT/TC中断

0:允许TE/HT/TC中断

DIR:数据传输方向 (Data transfer direction)

0:从外设读

1:从存储器读

CIRC:循环模式 (Circular mode)

0:不执行循环操作

1:执行循环操作

PINC:外设地址增量模式 (Peripheral increment mode)

0:不执行外设地址增量操作

1:执行外设地址增量操作

MINC:存储器地址增量模式 (Memory increment mode)

0:不执行存储器地址增量操作

1:执行存储器地址增量操作

PSIZE[1:0]:外设数据宽度 (Peripheral size)

00:8位 01:16位 10:32位 11:保留

MSIZE[1:0]:存储器数据宽度 (Memory size)

00:8位 01:16位 10:32位 11:保留

PL[1:0]:通道优先级 (Channel priority level)

00:低 01:中 10:高 11:最高

MEM2MEM:存储器到存储器模式 (Memory to memory mode)

0:非存储器到存储器模式;

1:启动存储器到存储器模式。

4.4 DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7)

NDT[15:0]:数据传输数量 (Number of data to transfer)

数据传输数量为0至65535。这个寄存器只能在通道不工作(DMA_CCRx的EN=0)时写入。通道开启后该寄存器变为只读,指示剩余的待传输字节数目。寄存器内容在每次DMA传输后递减。

数据传输结束后,寄存器的内容或者变为0;或者当该通道配置为自动重加载模式(循环模式)时,寄存器的内容将被自动重新加载为之前配置时的数值。

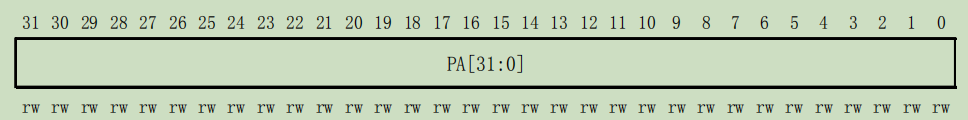

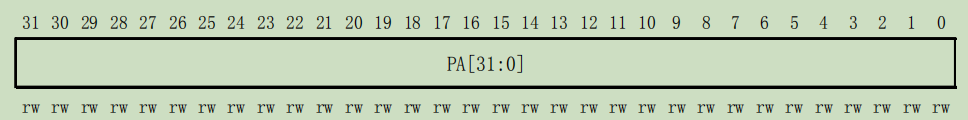

4.5 DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7)

PA[31:0]:外设地址 (Peripheral address),这里存放的是外设数据寄存器的基地址,作为数据传输的源或目标。

当PSIZE=’01’(16位),不使用PA[0]位。操作自动地与半字地址对齐。

当PSIZE=’10’(32位),不使用PA[1:0]位。操作自动地与字地址对齐。

4.6 DMA通道x存储器地址寄存器(DMA_CMARx)(x = 1…7)

与外设地址寄存器类似。

1. DMA简介

直接存储器存取(DMA,Direct Memory Access)用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。无须CPU干预,数据可以通过DMA快速地移动,节省CPU资源。DMA传输本质上是一种CPU进行权力下放的方式,将一些本来需要CPU处理的繁琐事务经过交代(配置DMA)之后全权交给DMA控制器处理。DMA 传输对于高效能嵌入式系统算法和网络是很重要的。

在实现DMA传输时,是由DMA控制器直接接管总线,因此,存在着一个总线控制权转移问题。即DMA传输前,CPU要把总线控制权交给DMA控制器,而在结束DMA传输后,DMA控制器应立即把总线控制权再交回给CPU。一个完整的DMA传输过程必须经过DMA请求、DMA响应、DMA传输、DMA结束4个步骤。

2. STM32的DMA架构

STM32有两个DMA控制器,共有12个通道(DMA1有7个通道,DMA2有5个通道),每个通道专门用来管理来自于一个或多个外设对存储器访问的请求。还有一个仲裁器来协调各个DMA请求的优先权。

2.1 DMA框图

由框图可以看到,DMA1和DMA2、以太网MAC、USB OTG FS均为AHB下的外设(时钟源是AHB),DMA1、DMA2、以太网MAC可以以DMA方式控制总线。其中主要的DMA1和DMA2控制器的DMA请求源均为APB1和APB2下的外设。一旦DMA接管总线,就可以对总线上外设进行数据读取,闪存、SRAM、外设的SRAM、APB1、APB2和AHB外设均可作为访问的源和目标。

2.2 DMA主要特性

12个独立的可配置的通道(请求):DMA1有7个通道,DMA2有5个通道每个通道都直接连接专用的硬件DMA请求,每个通道都同样支持软件触发。这些功能通过软件来配置。

在同一个DMA模块上,多个请求间的优先权可以通过软件编程设置(共有四级:很高、高、中等和低),优先权设置相等时由硬件决定(请求0优先于请求1,依此类推) 。

独立数据源和目标数据区的传输宽度(字节、半字、全字),模拟打包和拆包的过程。源和目标地址必须按数据传输宽度对齐。

支持循环的缓冲器管理

每个通道都有3个事件标志(DMA半传输、DMA传输完成和DMA传输出错),这3个事件标志逻辑或成为一个单独的中断请求。

存储器和存储器间的传输

外设和存储器、存储器和外设之间的传输

闪存、SRAM、外设的SRAM、APB1、APB2和AHB外设均可作为访问的源和目标。

可编程的数据传输数目:最大为65535

3. DMA详解

3.1 DMA请求

如框图所示,APB1和APB2下的外设向DMA控制器发送请求信号。

在发生一个事件后,外设向DMA控制器发送一个请求信号。DMA控制器通过仲裁器根据通道的优先权处理请求。当DMA控制器开始访问发出请求的外设时,立即向请求源发送一个应答信号,请求源得到应答后立即释放它的请求。

3.2 DMA通道

DMA共有12个独立可编程的通道,DMA1有7个、DMA2有5个。每个通道对应着多个不同的外设的请求,他们通过逻辑或连接到一个通道,一个通道同一时间只能接收一个外设请求。每个通道都可以在有固定地址的外设寄存器和存储器地址之间执行DMA传输。DMA传输的数据量是可编程的,最大达到65535。

DMA1通道:

DMA2通道:

3.3 DMA仲裁器

这么多通道,肯定要有优先级来进行管理,仲裁器根据通道请求的优先级来启动外设/存储器的访问。每个通道的优先权可以在DMA_CCRx寄存器中设置,有4个等级:

最高优先级

高优先级

中等优先级

低优先级

优先响应高优先级的通道,如果2个请求通道有相同的软件优先级,则较低编号的通道比较高编号的通道有较高的优先权。

3.4 DMA中断

每个DMA通道都可以在DMA传输过半、传输完成和传输错误时产生中断。为应用的灵活性考虑,通过设置寄存器的不同位来打开这些中断。

DMA中断请求:

3.5 传输方向

DMA有三个传输方向,外设到存储器、存储器到外设、存储器到存储器。

3.6 DMA循环模式

传送一次之后,又恢复第一次的配置,继续进行传输。

循环模式用于处理循环缓冲区和连续的数据传输(如ADC的扫描模式)。在DMA_CCRx寄存器中的CIRC位用于开启这一功能。当启动了循环模式,数据传输的数目变为0时,将会自动地被恢复成配置通道时设置的初值,DMA操作将会继续进行。当通道配置为非循环模式时,传输结束后(即传输计数变为0)将不再产生DMA操作。要开始新的DMA传输,需要在关闭DMA通道的情况下,在DMA_CNDTRx寄存器中重新写入传输数目。

3.7 地址增量模式

当传输的数据不止一个时,需要根据起始地址、数据宽度对后来的数据的读写地址进行指定,这就有了地址增量模式。通过设置DMA_CCRx寄存器中的PINC和MINC标志位,外设和存储器的指针在每次传输后可以有选择地完成自动增量。当设置为增量模式时,下一个要传输的地址将是前一个地址加上增量值,增量值取决与所选的数据宽度为1、2或4。第一个传输的地址是存放在DMA_CPARx /DMA_CMARx寄存器中地址。在传输过程中,这些寄存器保持它们初始的数值,软件不能改变和读出当前正在传输的地址。

4. DMA寄存器

4.1 DMA中断状态寄存器(DMA_ISR)

GIFx:通道x的全局中断标志(x = 1 … 7) (Channel x global interrupt flag)

如果通道x发生了下方三个中断(TCIFx、HTIFx、TEIFx)任意一个,该位就被置位。

TCIFx:通道x的传输完成标志(x = 1 … 7) (Channel x transfer complete flag),完成置1。

HTIFx:通道x的半传输标志(x = 1 … 7) (Channel x half transfer flag),完成置1。

TEIFx:通道x的传输错误标志(x = 1 … 7) (Channel x transfer error flag),出错置1。

在DMA_IFCR寄存器的相应位写入’1’可以清除DMA_ISR对应的标志位。

4.2 DMA中断标志清除寄存器(DMA_IFCR)

该寄存器对上述中断状态寄存器DMA_ISR清除相应的标志位。写1清除,写0无效。

4.3 DMA通道x配置寄存器(DMA_CCRx)(x = 1…7)

EN:通道开启 (Channel enable)

0:通道不工作

1:通道开启

TEIE/HTIE/TCIE:允许传输错误/半传输/传输完成中断 (Transfer error interrupt enable)

0:禁止TE/HT/TC中断

0:允许TE/HT/TC中断

DIR:数据传输方向 (Data transfer direction)

0:从外设读

1:从存储器读

CIRC:循环模式 (Circular mode)

0:不执行循环操作

1:执行循环操作

PINC:外设地址增量模式 (Peripheral increment mode)

0:不执行外设地址增量操作

1:执行外设地址增量操作

MINC:存储器地址增量模式 (Memory increment mode)

0:不执行存储器地址增量操作

1:执行存储器地址增量操作

PSIZE[1:0]:外设数据宽度 (Peripheral size)

00:8位 01:16位 10:32位 11:保留

MSIZE[1:0]:存储器数据宽度 (Memory size)

00:8位 01:16位 10:32位 11:保留

PL[1:0]:通道优先级 (Channel priority level)

00:低 01:中 10:高 11:最高

MEM2MEM:存储器到存储器模式 (Memory to memory mode)

0:非存储器到存储器模式;

1:启动存储器到存储器模式。

4.4 DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7)

NDT[15:0]:数据传输数量 (Number of data to transfer)

数据传输数量为0至65535。这个寄存器只能在通道不工作(DMA_CCRx的EN=0)时写入。通道开启后该寄存器变为只读,指示剩余的待传输字节数目。寄存器内容在每次DMA传输后递减。

数据传输结束后,寄存器的内容或者变为0;或者当该通道配置为自动重加载模式(循环模式)时,寄存器的内容将被自动重新加载为之前配置时的数值。

4.5 DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7)

PA[31:0]:外设地址 (Peripheral address),这里存放的是外设数据寄存器的基地址,作为数据传输的源或目标。

当PSIZE=’01’(16位),不使用PA[0]位。操作自动地与半字地址对齐。

当PSIZE=’10’(32位),不使用PA[1:0]位。操作自动地与字地址对齐。

4.6 DMA通道x存储器地址寄存器(DMA_CMARx)(x = 1…7)

与外设地址寄存器类似。

举报

举报

举报

举报