上海雷卯电子工程师在负责电力行业的智能采集终端项目升级时,即根据客户的新需求和国网、南网新标准对原设计进行改进。在做原产品的静电(ESD)抗扰度4级试验,即接触放电±8kV时,发现以太网会中断,直到ESD干扰消除后才能恢复正常,如图1所示,这种现象不满足国网、南网标准中“实验过程中,以太网偶尔中断,但能自行恢复”的规定,CLASS B的要求。

图1:以太网中断不能重连

有ESD设计经验的人一般都知道静电干扰途径主要为地传导、信号线+电源线+I/O线传输和空间辐射三种。针对以上三种干扰改进ESD设计的方法如下:

1)软件复位设计。增加软件看门狗,主循环坏死就reset;加状态检测判断寄存器/IO口状态是否正确,不对就reset。

2)增加保护目标ESD免疫力,即增强IC本身ESD防护能力,比如内置集成ESD。

3)降低减弱ESD放电对保护目标的冲击强度,比如在IC外围增加TVS管和防静电管等ESD防护器件,割地处理,对地并电容,及缩短走线距离等。

首先以太网芯片属于公司大批量使用的通用芯片,不应替代;其次软件看门狗/reset都已经做了处理,所以方法1和2都不可选,只能选择方法3。查看老版原理图发现原设计并未对以太网模块做所需的防ESD处理,只是在数字电源VCC和模拟电源AVCC上加了TVS管,而关键的差分信号TX+/TX-和RX+/RX-并没有设计ESD防护,所以需在差分信号端增加4个TVS管。

TVS管选型需要考虑以下因素:

1)大批量供货需考虑成本,一般而言,TVS管阵列比增加4个TVS管便宜;

2)封装小,节省Layout空间,方便布局,TVS管阵列会比4个TVS管的体积小很多;

3)ESD防护能力,必须大于国网、南网静电抗扰度4级,即接触放电±8kV,空气放电±15kV;

4)负载电容越低越好,能快速吸收ESD干扰。

经过查询资料选用

1)封装极小,1.6mm*1.2mm,封装和内部结构示意图如图2所示;

2)超低负载电容,0.85pF,可将快速信号衰减程度降至水平;

3)ESD防护能力高,接触放电±15kV,空气放电±15kV,远高于国网、南网标准;

4)极低的动态电阻,提供超低箝位电压;超低漏电流,3.3V时1nA电流;

5)以太网电源AVCC设计上能节省一个TVS管;

6)价格便宜。

图2:LEIDITECH ULC0504T6封装和内部结构示意图

以太网防静电部分设计原理图如图3所示,L2、C59、C60组成π型滤波网络,C61为去耦电容,R74-R77为以太网传输信号的上拉电阻,V10为TVS管,D9为TVS管阵列。

图3:以太网防静电部分威廉希尔官方网站

增加TVS管阵列ULC0504T6后,以太网模块在Layout设计时需注意以下几点:

1)ULC0504T6、滤波电容等ESD防护器件尽量和以太网芯片放在同一层,且尽量在同一层将它们的地pin与以太网芯片的地pin,这样能减少环路面积,让所包含的场流量减小,其感应电流减小。

2)ULC0504T6、滤波电容等ESD防护器件要靠近以太网芯片放置,差分信号和电源的走线先经过ESD器件pin再到以太网芯片pin;

3)要尽量保证地平面连续,该打过孔的地方要打过孔,以增加回流路径;

4)以太网模块不要靠近整个板件的边沿,尽量往中间放,这样能增强水平和垂直耦合静电抗扰度能力。

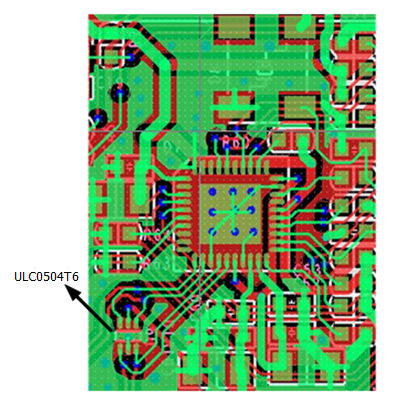

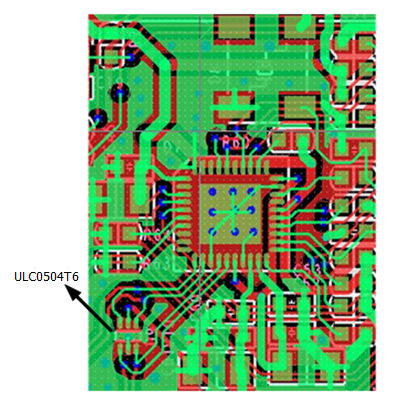

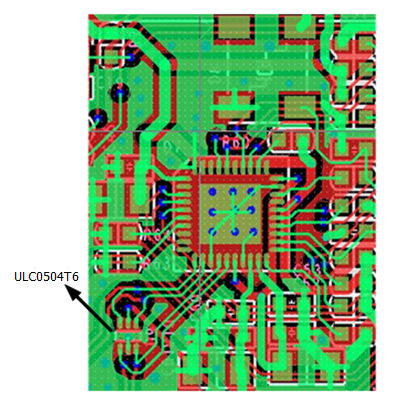

具体PCB布局如图4所示,由于以太网差分信号从下面上来,所以ULC0504T6放在左下角,这样保证了信号线先经过TVS管阵列再到以太网芯片pin上。

图4:以太网layout设计

改进后的设计,静电实验结果如图5所示。实验过程中偶尔断,但能立刻恢复,满足了国网、南网静电抗扰度4级实验要求。

图5:改进设计后的静电实验结构

上海雷卯电子工程师在负责电力行业的智能采集终端项目升级时,即根据客户的新需求和国网、南网新标准对原设计进行改进。在做原产品的静电(ESD)抗扰度4级试验,即接触放电±8kV时,发现以太网会中断,直到ESD干扰消除后才能恢复正常,如图1所示,这种现象不满足国网、南网标准中“实验过程中,以太网偶尔中断,但能自行恢复”的规定,CLASS B的要求。

图1:以太网中断不能重连

有ESD设计经验的人一般都知道静电干扰途径主要为地传导、信号线+电源线+I/O线传输和空间辐射三种。针对以上三种干扰改进ESD设计的方法如下:

1)软件复位设计。增加软件看门狗,主循环坏死就reset;加状态检测判断寄存器/IO口状态是否正确,不对就reset。

2)增加保护目标ESD免疫力,即增强IC本身ESD防护能力,比如内置集成ESD。

3)降低减弱ESD放电对保护目标的冲击强度,比如在IC外围增加TVS管和防静电管等ESD防护器件,割地处理,对地并电容,及缩短走线距离等。

首先以太网芯片属于公司大批量使用的通用芯片,不应替代;其次软件看门狗/reset都已经做了处理,所以方法1和2都不可选,只能选择方法3。查看老版原理图发现原设计并未对以太网模块做所需的防ESD处理,只是在数字电源VCC和模拟电源AVCC上加了TVS管,而关键的差分信号TX+/TX-和RX+/RX-并没有设计ESD防护,所以需在差分信号端增加4个TVS管。

TVS管选型需要考虑以下因素:

1)大批量供货需考虑成本,一般而言,TVS管阵列比增加4个TVS管便宜;

2)封装小,节省Layout空间,方便布局,TVS管阵列会比4个TVS管的体积小很多;

3)ESD防护能力,必须大于国网、南网静电抗扰度4级,即接触放电±8kV,空气放电±15kV;

4)负载电容越低越好,能快速吸收ESD干扰。

经过查询资料选用

1)封装极小,1.6mm*1.2mm,封装和内部结构示意图如图2所示;

2)超低负载电容,0.85pF,可将快速信号衰减程度降至水平;

3)ESD防护能力高,接触放电±15kV,空气放电±15kV,远高于国网、南网标准;

4)极低的动态电阻,提供超低箝位电压;超低漏电流,3.3V时1nA电流;

5)以太网电源AVCC设计上能节省一个TVS管;

6)价格便宜。

图2:LEIDITECH ULC0504T6封装和内部结构示意图

以太网防静电部分设计原理图如图3所示,L2、C59、C60组成π型滤波网络,C61为去耦电容,R74-R77为以太网传输信号的上拉电阻,V10为TVS管,D9为TVS管阵列。

图3:以太网防静电部分威廉希尔官方网站

增加TVS管阵列ULC0504T6后,以太网模块在Layout设计时需注意以下几点:

1)ULC0504T6、滤波电容等ESD防护器件尽量和以太网芯片放在同一层,且尽量在同一层将它们的地pin与以太网芯片的地pin,这样能减少环路面积,让所包含的场流量减小,其感应电流减小。

2)ULC0504T6、滤波电容等ESD防护器件要靠近以太网芯片放置,差分信号和电源的走线先经过ESD器件pin再到以太网芯片pin;

3)要尽量保证地平面连续,该打过孔的地方要打过孔,以增加回流路径;

4)以太网模块不要靠近整个板件的边沿,尽量往中间放,这样能增强水平和垂直耦合静电抗扰度能力。

具体PCB布局如图4所示,由于以太网差分信号从下面上来,所以ULC0504T6放在左下角,这样保证了信号线先经过TVS管阵列再到以太网芯片pin上。

图4:以太网layout设计

改进后的设计,静电实验结果如图5所示。实验过程中偶尔断,但能立刻恢复,满足了国网、南网静电抗扰度4级实验要求。

图5:改进设计后的静电实验结构

举报

举报

举报

举报