近年来,由于对

电子设备的需求不断增长,低功耗芯片的设计发挥了重要作用,这些电子设备越来越小化,并且功耗越来越低,以支持电池

电源。人工智能(AI)的使用 —— 越来越多地出现在可穿戴设备、物联网设备,以及更普遍的嵌入式系统中——正在给致力于开发具有更密集、更具创新性的架构和制造工艺的低功耗芯片的设计人员带来严峻的挑战。

需要适当的功率分析技术和工具来帮助工程师设计先进的AI芯片,以满足其特定要求,例如整体功能,可制造性,成本和可靠性。

低功耗设计低功耗设计的目的是降低

集成威廉希尔官方网站

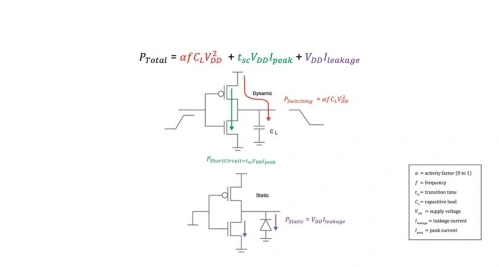

芯片的整体动态和静态功耗,这是实现下一代应用的关键方面。此过程涉及降低动态和静态功率。动态功率包括开关和短路功率分析,而静态功率主要包括漏电流分析。功率方程包括上述三个贡献,如图1所示。

图 1:功率分量和公式

在IC制造工艺基于90nm至16nm技术的那几年,设计人员的注意力集中在降低漏电功率上,因为它的重量(85%至95%)大于动态功率(10%至15%)。随着随后从16nm到14nm的过渡,功率方程发生了变化;泄漏功率得到了很好的控制,而动态功率则成为一个更重要的问题。首先,这是由于从平面到FinFET晶体管架构的过渡,这是一种建立在基板上的多门器件,其中栅极放置在通道的两侧,三侧或四侧或缠绕在通道周围,形成双栅极甚至多栅极3D结构。

在接下来的几年中,电子制造领域的不断进步将导致7,5甚至3nm的制造工艺,再次将泄漏功率的重要性推向前台。

人工智能的新挑战人工智能在电子应用中的日益广泛使用带来了新型的电力挑战。性能、功耗和面积 (PPA) 范例仍然是设计人员要实现的目标。不同之处在于,随着AI芯片的引入,在不牺牲功率的情况下最大化功率变得更加困难。如今,性能实际上受到功耗的限制,并且很难在不担心散热和热管理的情况下将功率可靠地输送到芯片的每个部分。

矢量的质量(定义为SoC在真实系统中工作时看到的实际活动)对于动态功耗分析和优化至关重要。

"最大的问题是估计工作负载,特别是当SoC在现场运行时,在真实系统上,"低功耗架构师兼Synopsys设计集团研究员Godwin Mabe说。"我们需要了解测量和优化动态功率的工作量。在人工智能方面,没有预定义的基准。我们需要识别这些工作负载,确保它们被捕获,并且更早地调试电源。

低功耗设计意味着了解功耗在软件开发、硬件设计和制造中的影响。它不是一个单步活动,应该在整个芯片设计过程中运行,目的是降低整体动态和静态功耗。

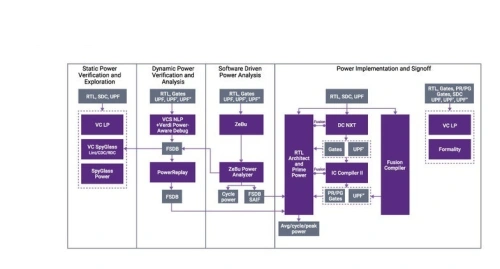

如图2所示,设计和验证方法分为五个主要阶段:

静态功率验证和探索

动态功率验证和分析

软件驱动的功耗分析

电源实现

签核

图 2:设计和验证阶段

仿真的作用提供SoC功耗估算值是一项艰巨的任务,这要求设计人员设置能够尽可能忠实地再现真实工作条件的测试台。能够满足这些要求的最佳系统是仿真。

为AI芯片运行功耗分析需要能够获取和处理数百千兆字节的合适工具,这些千兆字节由数万亿或数十亿个时钟周期组成。仿真系统中的电源分析有助于解决此问题,因为它只能识别电源分析的感兴趣窗口。

"有了AI芯片,两个新概念出现了,"Maben说。"第一个是验证调试具有挑战性,因为它需要很长时间。第二个问题是如何开发可以在芯片启动时准备就绪的应用软件。这就是仿真和原型设计概念出现的地方。

凭借其独特的快速仿真架构、最先进的商用

FPGA 以及基于FPGA的仿真软件创新,Synopsys的ZeBu Server是业界最快的仿真系统,可提供2×传统仿真解决方案的性能。ZeBu软件为用户提供了快速编译器、高级调试(包括与Verdi的本机集成)、仿真加速、混合仿真和功耗分析等宝贵工具。

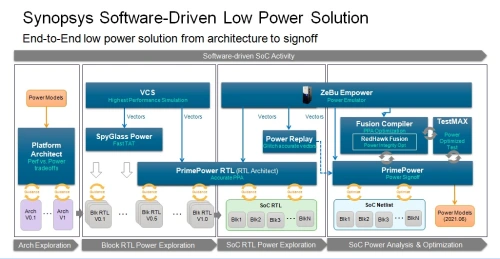

当应用程序在模拟器上运行时,它最终会转换为SoC的向量。然后,这些矢量可用于运行仿真,从而验证仿真器中芯片的功能。仿真是获取工作负载的正确平台,因为它会生成针对功率分析优化的向量。如图3所示,PrimePower RTL使用ZeBu EmPower矢量为设计人员提供有用的信息。

图 3:概要软件驱动的 SoC 活动

AI芯片使用大量的数学函数,主要是乘法和矩阵操作,由专用和优化的组合逻辑执行。

"当我们进入这些计算密集型应用的那一刻,设计人员担心的新概念是较低几何形状的故障功率。"毛刺功率占总功率的25%以上,我们知道毛刺功率意味着浪费功率。

故障的数量与SoC执行的操作数量成正比,这使得故障成为AI加速器需要解决的重要问题。有两种类型的毛刺:惯性毛刺和运输毛刺。惯性毛刺可以通过架构来解决,而运输毛刺是由于通过逻辑单元的延迟造成的,导致逻辑门输入处的到达时间不同。故障正在成为一个非常大的话题,因为它们很难优化,也很难衡量。

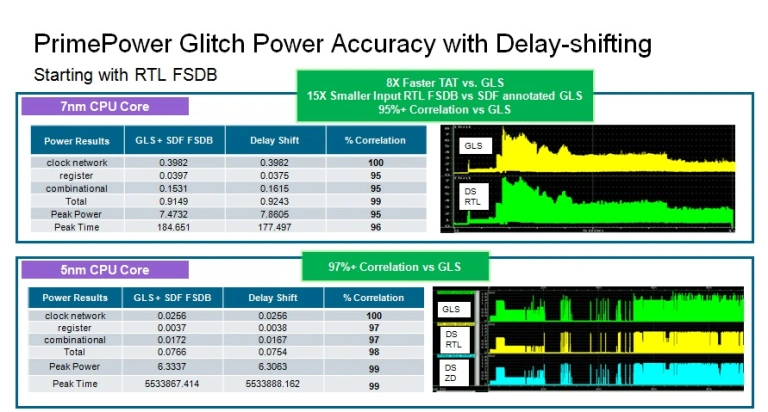

Synopsys提供端到端RTL到栅极的毛刺功率分析和优化解决方案。在RTL中,PrimePower RTL(见图 4)可以计算和报告每个层次结构的毛刺,还可以指向生成最高级别毛刺的RTL源代码行。PrimePower解决方案还提供使用RTL仿真的延迟/毛刺感知矢量生成,并可以使用零延迟栅极级仿真或与SPICE功率数密切相关的时序感知仿真来执行毛刺功率分析。

"故障正在变得占主导地位,特别是在AI芯片和较低的几何形状中,"有像PrimePower RTL这样的工具,它可以告诉设计人员哪些块更麻烦,并对其进行排名。然后,架构师可以更改架构,使其不那么容易出现故障。

图 4:PrimePower RTL 毛刺功耗分析