[tr]概述[tr]本实验室介绍了设置使用

[tr]Eval-AD 7091SDZ[tr]评估委员会和

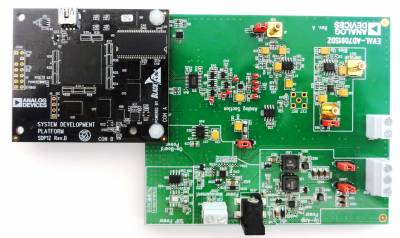

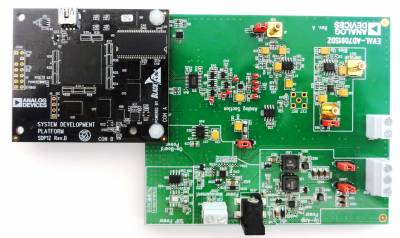

[tr]BemicroSDK [tr]USB[tr]和Nios II嵌入式开发套件(EDS)。下面是EVAL-AD091SDZ评估委员会与BeMicroSDK平台的图片。

[tr]为了组件评估和性能目的,而不是快速原型,用户被指示使用部件评估设置。这包括:

- [tr]1.像SDP-B这样的控制器板(EVAL-SDP-CS1Z)

- [tr]2.与SDP兼容的产品评估委员会

- [tr]3.相应的个人电脑软件(随产品评估委员会发运)

[tr]SDP-B控制器板是模拟设备系统演示平台(SDP)的一部分.它提供了一个高速[tr]USB[tr]从PC到组件评估板的2.0连接。PC机运行评估软件。每个评估板都是与SDP兼容的子板,包括性能测试所需的安装文件。

[tr]注:[tr]预计这两个平台的模拟性能可能有所不同。

[tr]2012年9月28日09:00 · [tr]阿德里安C

[tr]下面是一张

[tr]SDP-B[tr]控制器板

[tr]Eval-AD 7091SDZ[tr]评价委员会。

[tr]这个

[tr]Eval-AD 7091SDZ[tr]评估委员会是越来越多的委员会的成员之一。

[tr]SDP[tr]。它们的设计目的是帮助客户评估性能或快速将新产品原型化。

[tr]AD 7091[tr]

威廉希尔官方网站

设计,缩短设计时间。

[tr]这个[tr]AD 7091[tr]是一种12位逐次逼近寄存器模拟数字转换器,它提供超低功耗(通常为367μA在3下)。V[tr]和1[tr]MSPS[tr])同时实现快速吞吐量(1[tr]MSPS[tr]带着50[tr]兆赫 [tr]SCLK[tr])。AD 7091只运行于一个2.09V[tr]至5.25V[tr]电力供应。AD 7091还具有片上转换时钟和高速串行接口.

[tr]更多信息- [tr]AD 7091产品信息[tr]-定价、样品、数据表

- [tr]AD7091SDZ评估板用户指南

- [tr]BemicroSDK

- [tr]NIOS II嵌入式开发套件(EDS)

[tr]开始[tr]第一个目标是确保您拥有所需的所有项目,并安装软件工具,以便您可以创建和运行评估项目。

[tr]硬件项目[tr]以下是所需硬件项目的清单:

- [tr]箭电子[tr]BemicroSDK[tr]基于FPGA的单片机评测板

- [tr]BemicroSDK/SDP Interposer[tr]适配器板

- [tr]Eval-AD 7091SDZ[tr]评估委员会

- [tr]Intel Pentium III或兼容Windows PC,运行在866 MHz或更高,至少有512 MB的系统内存

[tr]软件工具[tr]以下是所需的软件工具清单:

- [tr]QUARTUS II网络版[tr]设计软件v12.1 SP1

- [tr]NIOS II EDS[tr]V12.1 SP1

[tr]这个

[tr]QUARTUS II[tr]设计软件和

[tr]NIOS II EDS[tr]可通过AlteraCompleDesignSuite DVD或从网络下载。

[tr]下载

[tr]提取实验室文件[tr]创建一个名为“

[tr]ADIEvalBoardLab[tr]“在您的电脑上并解压

[tr]Ad7091R_valboardlab.zip[tr]存档到这个文件夹。确保有

[tr]无空间[tr]在目录路径中。解压缩存档后,应将下列文件夹显示在

[tr]ADIEvalBoardLab[tr]文件夹:

[tr]FPGA,

[tr]高密度脂蛋白 [tr]软件,

[tr]DataCapture,

[tr]NiosCpu.

文件夹描述

FPGA包含所有必要的文件来编程BeMicroFPGA板,以运行评估项目。通过执行脚本

程序fpga.batFPGA将与评估项目一起编程。可以使用此文件夹中的文件创建新的NIOS II应用程序。

这个

IP子文件夹包含AD7091RNIOS II外围设备的源代码。

高密度脂蛋白包含AD 7091 HDL驱动程序的源文件:

--

博士子文件夹包含驱动程序的简要文档。

--

SRC子文件夹包含HDL源文件。

--

结核病文件夹包含驱动程序测试工作台的源。

NiosCpu包含Quartus评估项目源文件。这个

IP子文件夹包含AD 7091 Nios 2外围源代码。

软件包含Nios 2 SBT评估项目的源文件。

DataCapture包含用于数据采集的脚本文件。

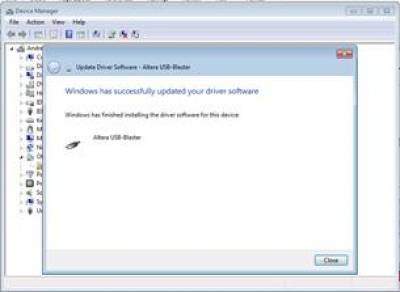

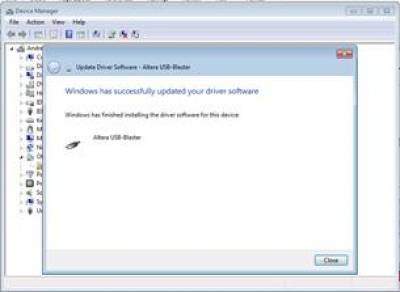

[tr]安装u***-blaster设备驱动程序。[tr]在.之后

[tr]QUARTUS II[tr]和

[tr]NIOS II[tr]安装了软件包,您可以将BeMicroSDK板插入到您的[tr]USB[tr]港口。您的WindowsPC将找到新的硬件,并尝试安装驱动程序。

[tr]由于Windows无法找到设备的驱动程序,自动安装将失败,驱动程序必须手动安装。在

[tr]设备管理器[tr]右键单击

[tr]USB[tr]-Blaster[tr]设备和选择

[tr]更新驱动软件.

[tr]在下一个对话框中选择该选项

[tr]浏览我的电脑寻找驱动软件[tr]。一个新的对话框将在可能指向驱动程序位置的地方打开。将位置设置为

[tr]阿尔特拉[tr]QUARTUS驱动程序USB-爆炸器[tr]和新闻

[tr]下一个.

[tr]如果Windows向您显示驱动程序尚未通过WindowsLogo测试的消息,请单击“

[tr]无论如何,请安装此驱动程序软件。[tr]“安装完成后,将显示一条消息,通知安装已完成。

[tr]2011年9月15日15:23

[tr]AD 7091评估项目概述[tr]评估项目包含构建系统所需的所有源文件,该系统可用于配置AD 7091并从中捕获数据。该系统由一个NiosⅡ软核处理器和一个PC应用程序组成,该处理器是在BeMicroboard上的FPGA上实现的。软核控制与待测设备(DUT)的

通信和数据捕获过程。将捕获的数据保存到BeMicroboard的片上RAM中,然后由PC应用程序读取,并保存到一个逗号分隔值(.csv)文件中,可用于进一步的数据分析。

[tr]在FPGA设计中实现了以下组件:

名字

地址

伊尔克

cpu

0x00000800

-

主锁相环

0x00000080

-

JTAG UART

0x00000090

0

UC探针UART

0x000000A0

1

EPC闪存控制器

0x00001800

2

片内RAM

0x00010000

-

雷德GPIO

0x00000100

-

GPIO

0x00002080

-

克特GPIO

0x000020A0

-

Sys ID

0x00000040

-

定时器

0x00000060

3

阿瓦隆大师

-

-

AD 7091R外围设备

0x00000120

-

表1系统组件

[tr]Nios II处理器包含实现与DUT通信协议的外围设备。外设分为三个逻辑模块:与Avalon总线接口和与片上RAM通信的模块,实现Avalon主接口直接写入片内RAM的模块和DUT的实际驱动程序模块。在不包含软核的FPGA设计中,该驱动程序也可以作为独立的驱动程序。给出了硬件描述语言驱动程序的框图,并对驱动程序的接口信号进行了描述。

[tr]表2描述了AD 7091 HDL驱动程序的端口。

港方向宽度描述

时钟和复位端口

FPGA CLK_I

在……里面

1

主时钟输入。

复位N_i

在……里面

1

主动低复位信号。

ADC_CLK_I

在……里面

1

在转换过程中发送给ADC的时钟。

IP控制和数据端口

数据O

走出16输出从ADC读取的数据。

数据RD_就绪_O

走出

1

主动高信号指示从AD 7091读取操作的状态。IP连续读取来自ADC的转换结果,并将它们输出到Data_O总线上。当信号较高时,可以从Data_O总线读取数据。

AD 7091控制和数据端口

ADC_SDATA_I

在……里面

1ADC串行数据输出。转换结果在这个引脚上输出。它被同步到SCLK

ADCSCLKO

走出

1

ADC串行数据时钟输入。当选择部件时,转换结果由该时钟移出。

ADC_CS_N_O

走出

1

ADC芯片选择当CS保持较低时启用串行总线,并使用CS在SPI.

ADC_CNVST_O

走出

1

ADC转换输入。此输入具有多个功能。在其前沿,它启动转换并选择部件、链或CS模式的接口模式。在CS模式下,它在低时启用SDO引脚。在链式模式下,当CNV较高时,应读取数据。

表2 AD 7091驱动程序端口描述

[tr]折叠图显示了从AD 7091驱动器读取操作的时序图。

[tr]表3描述了Avalon外围设备的端口:

港方向宽度描述

时钟和复位端口

CLK_i

在……里面

1

主时钟输入

复位I

在……里面

1

系统复位

ADC_CLK_I

在……里面

1

ADC时钟

Avalon从接口

阿瓦隆WRITEDATA_I

在……里面

32从写数据总线

阿瓦隆写I

在……里面

1

从写入数据请求

阿瓦隆读

在……里面

1

从读数据请求

阿瓦隆地址

在……里面

2

从地址总线

Avalon_READDATA_O

走出32从读数据总线

Avalon主接口

阿瓦隆大师

在……里面

1

主等待请求信号

阿瓦隆主地址

走出32主地址总线

阿瓦隆大师走出

4

主字节启用信号

Avalon_master_WRITEDATA_O走出32主写数据总线

外部连接器

ADC_SDATA_I

在……里面

1ADC串行数据输出。转换结果在这个引脚上输出。它被同步到SCLK

ADCSCLKO

走出

1

ADC串行数据时钟输入。当选择部件时,转换结果由该时钟移出。

ADC_CS_N_O

走出

1

ADC芯片选择当CS保持较低时启用串行总线,并使用CS在SPI.

ADC_CNVST_O

走出

1

ADC转换输入。此输入具有多个功能。在其前沿,它启动转换并选择部件、链或CS模式的接口模式。在CS模式下,它在低时启用SDO引脚。在链式模式下,当CNV较高时,应读取数据。

表3 Avalon外围端口描述

[tr]表4描述了Avalon外围设备的寄存器:

名字偏移量宽度存取描述

控制寄存器

0

32

RW位0用于启动数据采集。

位1用于启动内核的软件重置。

位2用于配置Avalon写主核以将数据写入相同的位置。

BIT 3用于向AD 7091评估板写入数据。

Acq计数寄存器

1

32

RW用于配置在开始获取时要获取的样本数的寄存器。

基寄存器

2

32

RW寄存器用于配置要写入所获取数据的内存位置的基地址。

状态寄存器

3

32

R

位0是用来表示采集完成的信号。

位1用来表示内存缓冲区已经溢出。

位2用于表示用户已对不可用寄存器进行读取。

表4 Avalon外围寄存器描述

[tr]快速评估[tr]本实验室的下一部分介绍了创建一个功能齐全的项目所需的所有步骤,这些步骤可用于评估[tr]阿迪[tr]站台。可以跳过这些步骤,将一个功能齐全的系统加载到FPGA中。快速评估过程的第一步是用实验室文件中提供的图像对FPGA进行编程。在加载图像之前,

[tr]QUARTUS II网络版[tr]工具或[tr]QUARTUSⅡ程序员[tr]必须安装在计算机上。若要加载fpga图像,请运行

[tr]程序fpga.bat[tr]批处理文件位于

[tr]ADIEvalBoardLab/FPGA[tr]文件夹。加载图像后,必须重置系统。现在,fpga包含了一个功能齐全的系统,可以直接跳到

[tr]演示项目用户界面[tr]这个实验室的一部分。

[tr]2012年9月3日17:42 · [tr]阿德里安C

[tr]NIOSⅡ软件设计[tr]本节介绍了开发将在

[tr]BeMicroSDK[tr]系统,并将用于控制和监视[tr]阿迪[tr]评估委员会。

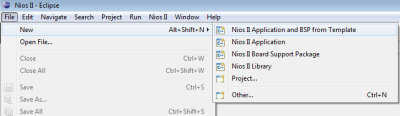

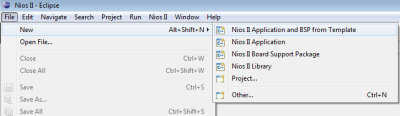

[tr]使用用于Eclipse的NIOS II软件构建工具创建一个新项目[tr]发射

[tr]NIOS II SBT[tr]从

[tr]启动→所有程序→Altera12.0sp2→Nios II EDS 12.0sp2→Nios II 12.0sp2面向Eclipse的软件构建工具.

[tr]注意:windows 7用户需要右击并选择

[tr]以管理员身份运行[tr]。另一种方法是右击并选择

[tr]特性[tr]并单击

[tr]兼容性[tr]选项卡并选择

[tr]以管理员身份运行此程序[tr]复选框,这将使这是一个永久的改变。

[tr]1.初始化Eclipse工作区- [tr]当Eclipse第一次启动时,会出现一个对话框,询问它应该使用哪个目录作为工作区。将单独的Eclipse工作区与SOPCBuilder中创建的每个硬件项目关联起来是非常有用的。浏览到[tr]ADIEvalBoardLab[tr]目录并单击[tr]创建新文件夹[tr]若要为软件项目创建文件夹,请执行以下操作。命名新文件夹“[tr]月食工作区[tr]“选择工作区目录后,单击[tr]好的[tr]而Eclipse将启动,工作台将出现在[tr]NIOS II[tr]透视。

[tr]2.在SBT中创建一个新的软件项目

[tr]2.在SBT中创建一个新的软件项目- [tr]选择[tr]文件→新→NiosⅡ应用程序和模板BSP.

- [tr]单击[tr]浏览[tr]按钮中的[tr]SOPC信息文件名[tr]对话框。

- [tr]选择[tr]UC.sopcinfo[tr]文件位于[tr]ADIEvalBoardLab/FPGA[tr]目录。

- [tr]将应用程序项目的名称设置为“[tr]ADIEvalboard”.

- [tr]选择[tr]空白工程[tr]模板下[tr]项目模板.

- [tr]单击[tr]完成[tr]纽扣。

[tr]该工具将创建两个新的软件项目目录。每个Nios II应用程序在Eclipse工作区中都有两个项目目录。

- [tr]应用软件项目本身--这是应用程序居住的地方。

- [tr]第二个是[tr]董事会支援计划(BSP)[tr]与主应用软件项目相关联的项目。该项目将为特定的SOPC系统构建系统库驱动程序。此项目继承主软件项目的名称并附加“[tr]_BSP[tr]“”为了那个。

[tr]由于选择了空白项目模板,此时应用程序项目目录中没有源文件。BSP包含一个软件驱动程序目录以及一个system.h头文件、系统初始化源代码和其他软件基础结构。

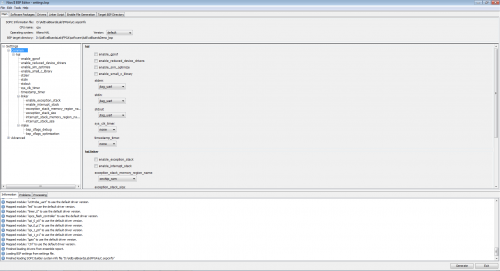

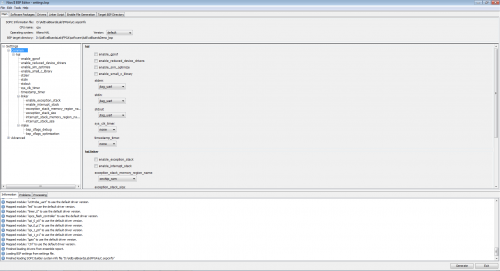

[tr]配置董事会支持包- [tr]配置板支持包以指定此软件系统的属性,方法是使用[tr]BSP编辑器[tr]工具。这些属性包括应该用于什么接口。[tr]斯迪奥[tr]和[tr]斯泰尔[tr]消息、应在其中分配堆栈和堆的内存以及是否应将操作系统或网络堆栈包括在此BSP中。

- [tr]右键单击[tr]ADIEvalboard_BSP[tr]项目和选择[tr]→ⅡBSP编辑器…[tr]从右击菜单.

[tr]本实验室提供的软件项目不使用操作系统。全

[tr]标准输出,

[tr]史丁[tr]和

[tr]斯泰尔[tr]消息将被定向到

[tr]JTAG_UART.

- [tr]选择[tr]共同[tr]设置视图。在[tr]共同[tr]设置视图,请更改下列设置:

- [tr]选择[tr]JTAG_UART[tr]为[tr]史丁, [tr]标准输出[tr]和[tr]斯泰尔[tr]留言。请注意,您有一个以上的选择。

- [tr]选择[tr]无[tr]为[tr]SYS_CLK定时器[tr]和[tr]时间戳定时器.

- [tr]选择[tr]文件→保存[tr]若要将板支持包配置保存到[tr]Settings.bsp[tr]档案。

- [tr]单击[tr]生成[tr]按钮来更新BSP。

- [tr]生成完成后,选择[tr]文件→退出[tr]若要关闭BSP编辑器,请执行以下操作。

[tr]配置BSP项目构建属性[tr]除了使用

[tr]BSP编辑器[tr],还有其他由Eclipse环境管理的编译设置,如编译器标志和优化级别。

- [tr]右键单击[tr]ADIEvalboard_BSP[tr]软件项目和选择[tr]特性[tr]从右击菜单.

- [tr]在左侧菜单上,选择[tr]NIOS II BSP属性.

- [tr]在编译期间,代码可能具有不同级别的优化,这是代码大小和性能之间的权衡。更改[tr]优化水平[tr]设置为[tr]2级

- [tr]由于我们的软件不使用C++,所以取消检查[tr]支持C++.

- [tr]检查[tr]减少设备驱动程序[tr]期权

- [tr]检查[tr]小型C库[tr]期权

- [tr]压榨[tr]应用[tr]和[tr]好的[tr]若要重新生成BSP并关闭[tr]特性[tr]窗户。

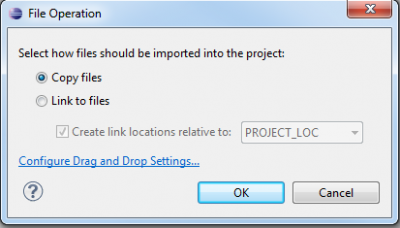

[tr]向项目添加源代码

[tr]向项目添加源代码[tr]在WindowsExplorer中,找到项目目录,其中包含一个名为

[tr]软件[tr]。在WindowsExplorer中,从

[tr]软件[tr]文件夹并将它们拖放到Eclipse软件项目中。

[tr]ADIEvalboard.

- [tr]选择所有文件和文件夹,并将它们拖到[tr]ADIEvalboard[tr]项目在SBT窗口中,并将文件拖放到项目文件夹中。

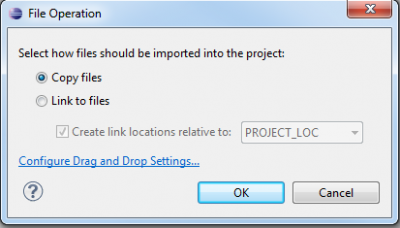

- [tr]将出现一个对话框来选择所需的操作。选择选项[tr]复制文件和文件夹[tr]和新闻[tr]好的.

- [tr]这将导致源文件被物理地复制到软件项目目录的文件系统位置,并在Eclipse工作区中注册这些源文件,以便它们出现在ProjectExplorer文件列表中。

[tr]配置应用程序项目构建属性

[tr]配置应用程序项目构建属性[tr]正如您为bsp项目配置了优化级别一样,您应该为应用软件项目设置优化级别。

[tr]ADIEvalboard[tr]也是。

- [tr]右键单击[tr]ADIEvalboard[tr]软件项目和选择[tr]特性[tr]从右击菜单.

- [tr]在左侧菜单上,选择[tr]NIOS II应用程序属性[tr]附签

- [tr]更改[tr]优化水平[tr]设置为[tr]2级.

- [tr]压榨[tr]应用[tr]和[tr]好的[tr]以保存更改。

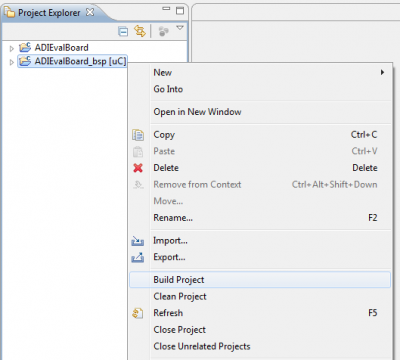

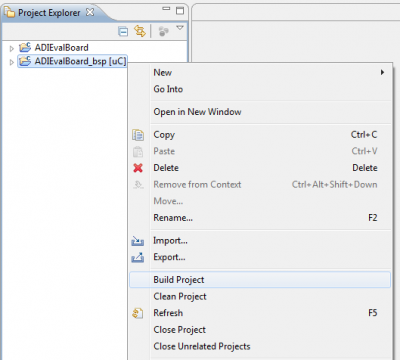

[tr]编译、下载和运行软件项目[tr]1.建立应用程序和BSP项目

[tr]编译、下载和运行软件项目[tr]1.建立应用程序和BSP项目- [tr]右键单击[tr]ADIEvalboard_BSP[tr]软件项目与选择[tr]建设项目[tr]建立董事会支援计划。

- [tr]生成完成后,右键单击[tr]ADIEvalboard[tr]应用软件项目及选择[tr]建设项目[tr]来构建Nios II应用程序。

[tr]这两个步骤将编译和构建相关的板支持包,然后实际应用软件项目本身。编译过程的结果将是

[tr]可执行和链接格式(.Elf)[tr]应用程序的文件,

[tr]ADIEvalBoard.elf[tr]档案。

[tr]2.核实委员会的连接

[tr]2.核实委员会的连接[tr]这个

[tr]BeMicroSDK[tr]硬件是用一个

[tr]系统ID[tr]外围。根据最后一次在SOPCBuilder工具中修改硬件设计的时间,为该外围设备分配了一个独特的值。SOPC Builder还将此信息放置在

[tr].socinfo[tr]硬件描述文件BSP是基于

[tr].socinfo[tr]档案。

- [tr]选择[tr]ADIEvalboard[tr]应用软件项目。

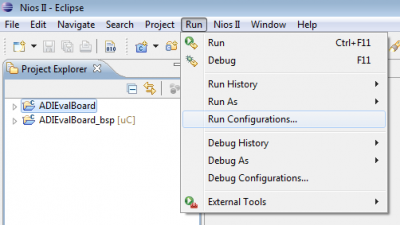

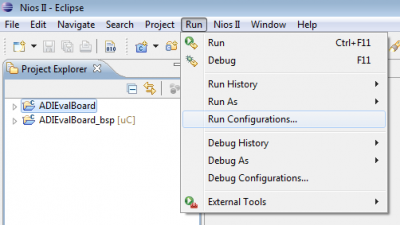

- [tr]选择[tr]运行→运行配置…

- [tr]选择[tr]NIOS II硬件[tr]配置类型

- [tr]按[tr]新的[tr]按钮创建新配置。

- [tr]将配置名称更改为[tr]BeMicroSDK[tr]然后点击[tr]应用.

- [tr]在[tr]目标连接[tr]选项卡,按[tr]刷新连接[tr]纽扣。您可能需要展开窗口或向右滚动以查看此按钮。

- [tr]选择[tr]JTAG_UART[tr]就像[tr]字节流设备[tr]为[tr]斯迪奥.

- [tr]检查[tr]忽略不匹配的系统ID选项.

- [tr]检查[tr]忽略不匹配的系统时间戳选项.

[tr]3.按目标运行软件项目

[tr]3.按目标运行软件项目[tr]要在Nios II处理器上运行软件项目:

- [tr]按[tr]跑[tr]按钮中的[tr]运行配置[tr]窗户。

[tr]这将重新构建软件项目,以创建最新的可执行文件,然后将代码下载到

[tr]BeMicroSDK[tr]硬件。调试器重置Nios II处理器,并执行下载的代码。请注意,代码在执行之前在内存中进行了验证。

[tr]代码大小和开始地址可能与上述屏幕截图中显示的不同。

[tr]2012年9月4日09:08 · [tr]阿德里安C

[tr]演示项目用户界面[tr]为了从ADC捕获数据,必须执行以下步骤:

- [tr]执行[tr]数据捕获[tr]剧本。此时,将从ADC中获取16 KB的数据,并将其保存到BeMicroSDK内存中。存储在BeMicroSDK内存中的数据被传输到PC上。在将数据传输到pc后,将其转换为16位值。

- [tr]从adc中捕获的数据保存到一个逗号分隔值(.csv)文件中,名为[tr]Acquisition.csv[tr],位于与[tr]数据捕获[tr]档案。

- [tr]数据捕获状态也显示在打开的命令窗口中,如下图所示。

- [tr]可以通过执行[tr]数据捕获[tr]剧本。

[tr]注:[tr]如果执行了几个连续的数据获取,则捕获的数据将追加到

[tr]Acquisition.csv[tr]档案。