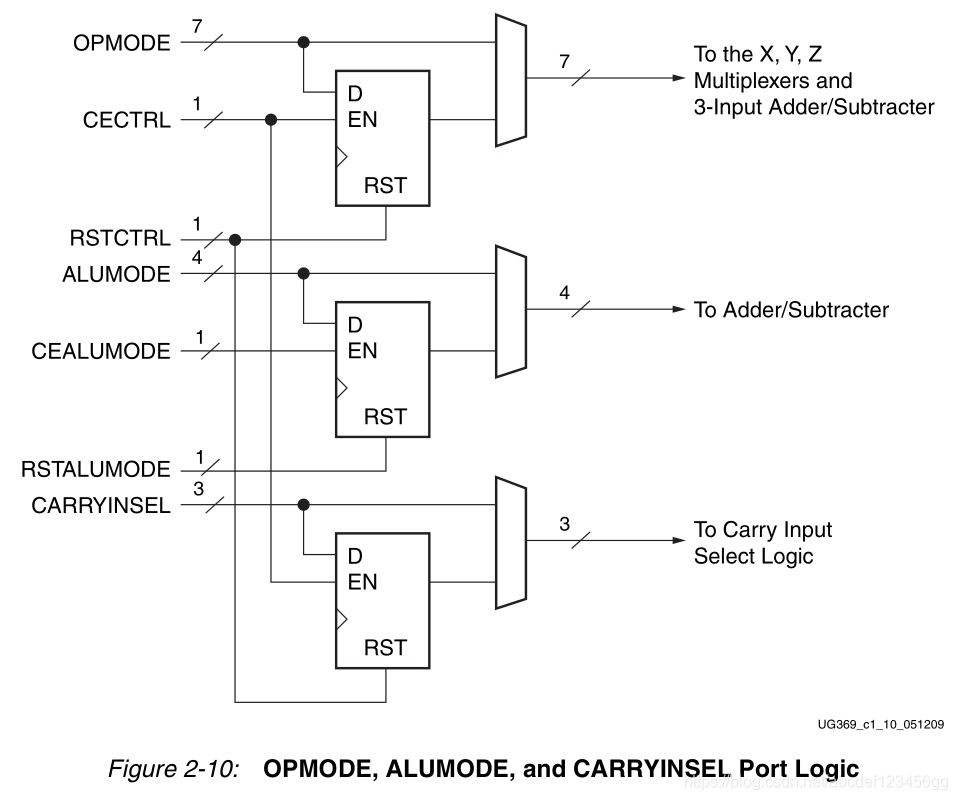

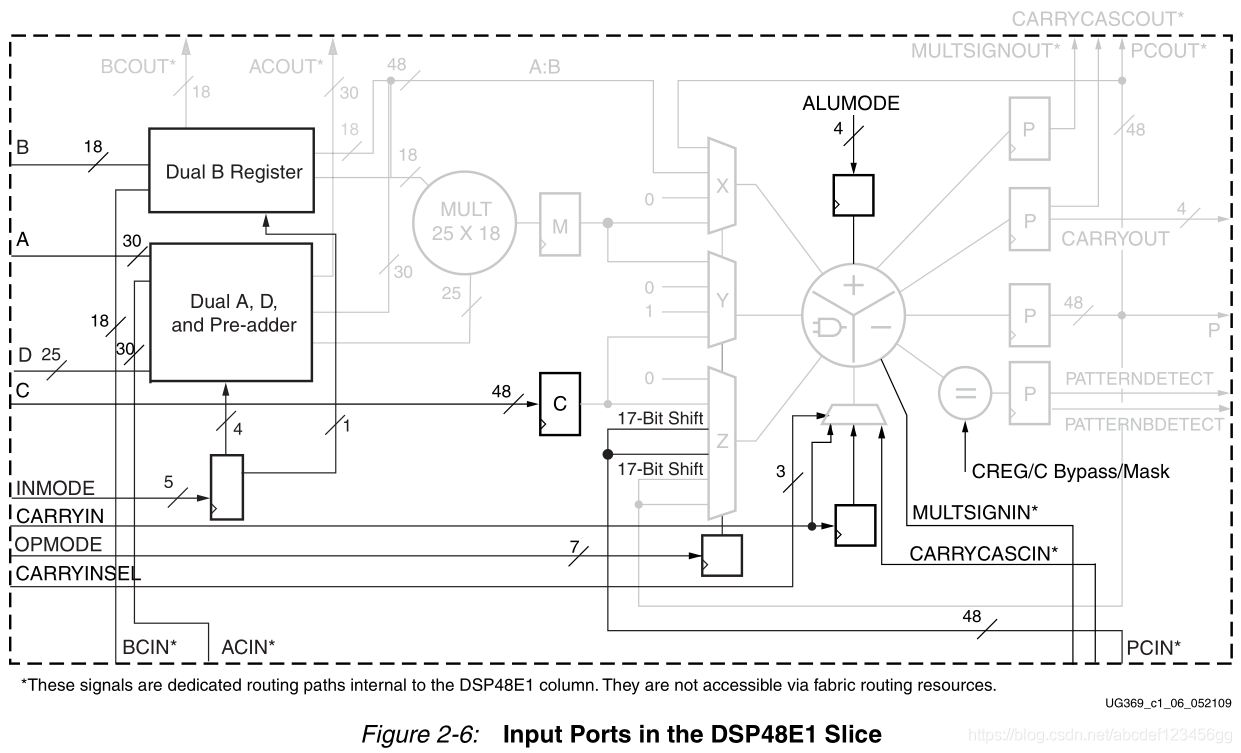

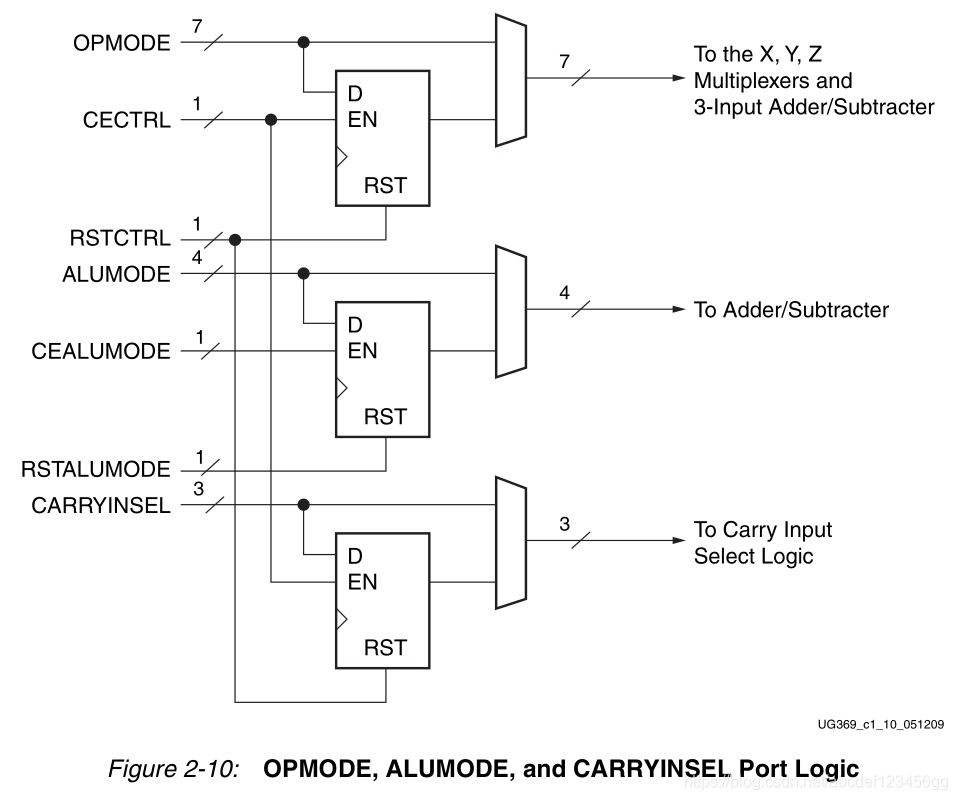

OPMODE、ALUMODE和CARRYINSEL端口逻辑支持flow through or registered输入控制信号。由配置位控制的多路复用器选择通过寄存器或可选寄存器的数据流。控制端口寄存器允许用户对增加的寄存器进行权衡,使其具有独立的时钟启用和复位功能。OPMODE和CARRYINSEL寄存器通过RSTCTRL复位。ALUMODE被RSTALUMODE重置。时钟启用,OPMODE、ALUMODE和CARRYINSEL端口逻辑如图2-10所示。

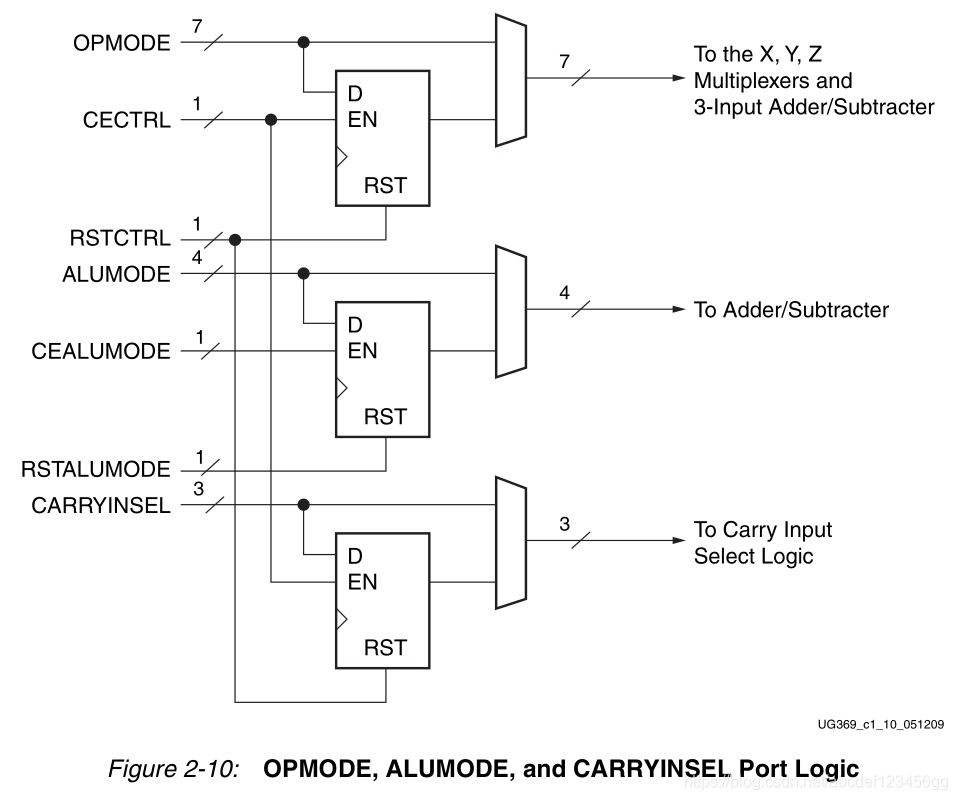

X, Y, and Z Multiplexers

OPMODE(操作模式)控制输入包含X、Y和Z多路选择的字段。

OPMODE输入提供了一种从时钟周期到时钟周期动态更改DSP48E1功能的方法(例如,相对于给定的计算序列更改DSP48E1片的内部数据路径配置)。

OPMODE位可以使用OPMODEREG属性注册(如表2-3所示)。

ALUMODE

4位ALUMODE控制第二阶段加/减/逻辑单元的行为。

ALUMODE = 0000 选择表单Z + (X + Y + CIN)的添加操作。

ALUMODE = 0011 选择Z - (X + Y + CIN)形式的减运算。

ALUMODE = 0001 可以实现- z + (X + Y + CIN) - 1 = not (Z) + X + Y + CIN。

ALUMODE = 0010 可以实现 - (Z + X + Y + CIN) - 1 = not (Z + X + Y + CIN)。

2的补数的负数是通过按位反转和加1得到的,例如-k = not (k) + 1。

其他的减运算和逻辑运算也可以通过增强型的加/减/逻辑单元来实现。见表2 - 10。

输出端口

除ACOUT和BCOUT外的所有输出端口都由RSTP重置,并由CEP启用(参见图2-13)。ACOUT和BCOUT分别通过RSTA和RSTB复位(如图2-7和图2-8所示)。

P端口

每个DSP48E1片都有一个48位的输出端口p。这个输出可以通过PCOUT路径内部连接(级联连接)到相邻的DSP48E1片。PCOUT连接到相邻的DSP48E1片中的Z多路复用器(PCIN)的输入。此路径提供相邻DSP48E1片之间的输出级联流。

CARRYCASCOUT and CARRYOUT 端口

每个DSP48E1片的执行可以使用CARRYOUT端口发送到FPGA逻辑。这个端口是4位宽。CARRYOUT[3]是双输入48位加法器/减法器或单输入累加器的有效进位输出。在本例中,USE_SIMD = ONE48是默认设置,代表非simd配置。当两个输入加法器、减法器或使用一个输入累加器在SIMD模式中,这样的信号是无效的,如果三个输入加法器、减法器(例如,a: B + C + PCIN)或两个输入累加器(例如,a: B + C + P)配置使用或者使用乘数。

OPMODE、ALUMODE和CARRYINSEL端口逻辑支持flow through or registered输入控制信号。由配置位控制的多路复用器选择通过寄存器或可选寄存器的数据流。控制端口寄存器允许用户对增加的寄存器进行权衡,使其具有独立的时钟启用和复位功能。OPMODE和CARRYINSEL寄存器通过RSTCTRL复位。ALUMODE被RSTALUMODE重置。时钟启用,OPMODE、ALUMODE和CARRYINSEL端口逻辑如图2-10所示。

X, Y, and Z Multiplexers

OPMODE(操作模式)控制输入包含X、Y和Z多路选择的字段。

OPMODE输入提供了一种从时钟周期到时钟周期动态更改DSP48E1功能的方法(例如,相对于给定的计算序列更改DSP48E1片的内部数据路径配置)。

OPMODE位可以使用OPMODEREG属性注册(如表2-3所示)。

ALUMODE

4位ALUMODE控制第二阶段加/减/逻辑单元的行为。

ALUMODE = 0000 选择表单Z + (X + Y + CIN)的添加操作。

ALUMODE = 0011 选择Z - (X + Y + CIN)形式的减运算。

ALUMODE = 0001 可以实现- z + (X + Y + CIN) - 1 = not (Z) + X + Y + CIN。

ALUMODE = 0010 可以实现 - (Z + X + Y + CIN) - 1 = not (Z + X + Y + CIN)。

2的补数的负数是通过按位反转和加1得到的,例如-k = not (k) + 1。

其他的减运算和逻辑运算也可以通过增强型的加/减/逻辑单元来实现。见表2 - 10。

输出端口

除ACOUT和BCOUT外的所有输出端口都由RSTP重置,并由CEP启用(参见图2-13)。ACOUT和BCOUT分别通过RSTA和RSTB复位(如图2-7和图2-8所示)。

P端口

每个DSP48E1片都有一个48位的输出端口p。这个输出可以通过PCOUT路径内部连接(级联连接)到相邻的DSP48E1片。PCOUT连接到相邻的DSP48E1片中的Z多路复用器(PCIN)的输入。此路径提供相邻DSP48E1片之间的输出级联流。

CARRYCASCOUT and CARRYOUT 端口

每个DSP48E1片的执行可以使用CARRYOUT端口发送到FPGA逻辑。这个端口是4位宽。CARRYOUT[3]是双输入48位加法器/减法器或单输入累加器的有效进位输出。在本例中,USE_SIMD = ONE48是默认设置,代表非simd配置。当两个输入加法器、减法器或使用一个输入累加器在SIMD模式中,这样的信号是无效的,如果三个输入加法器、减法器(例如,a: B + C + PCIN)或两个输入累加器(例如,a: B + C + P)配置使用或者使用乘数。

举报

举报

举报

举报

举报

举报