TMS320C6678 ZYNQ的开发手册详细资料将围绕8大板块,分别有cameralink_loopback、sdi_capture_display、fmc_tw2867_display、dual_camera_display、hdmi_edge_display和cameralink_display、等视频案例,本期推文主要讲述的是首次新增的camera_edge_display视频案例讲解步骤,其中以创龙科技基于

ti TMS320C6678 + Xilinx Zynq-7045的高速多路高清视频采集处理平台,其采用DSP+

FPGA+ARM架构,可完美满足目标追踪关键指标,故此成为本期讲解实例。接下来,让我们一起往下看。

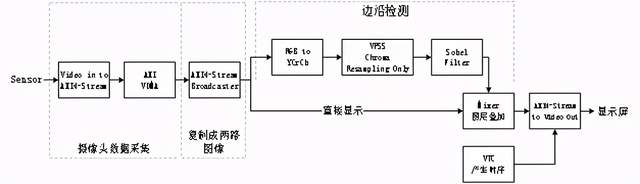

1 案例功能

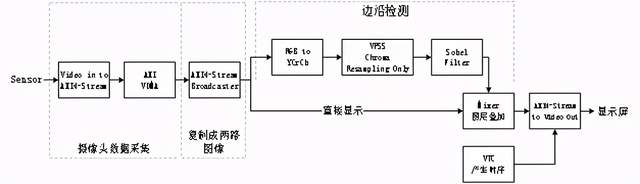

案例功能:PL端通过Video In to AXI4-Stream IP核采集摄像头视频,摄像头默认输出的视频分辨率为752x480@60,并通过AXI VDMA IP核将视频缓存到PS端DDR中,再通过AXI4-Stream Broadcaster IP核将视频复制成两路,一路用于Sobel(边缘检测)算法处理,另一路不作处理,然后通过Video Mixer IP核将两路视频进行叠加显示。

程序功能框图

2 操作说明

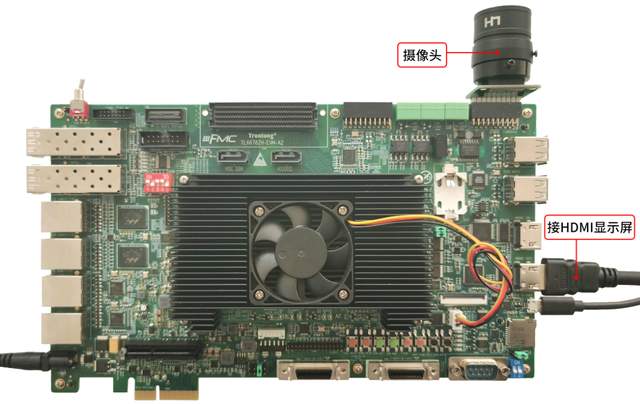

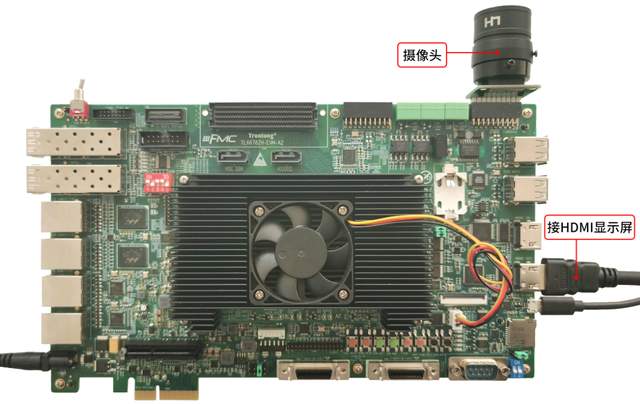

将MT9V034摄像头接到评估板CAMERA1接口,将HDMI显示屏通过HDMI数据线连接至评估板HDMI OUT接口。

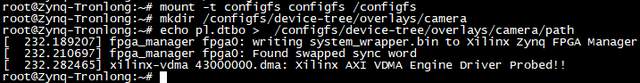

将本案例的动态设备树镜像文件pl.dtbo和PL端.bin格式可执行文件复制到"/lib/firmware/"目录下,并将PL端可执行文件重命名为system_wrapper.bin,然后执行如下命令加载设备树文件和PL端可执行文件。

Target# mount -t configfs configfs /configfs

Target# mkdir /configfs/device-tree/overlays/camera

Target# echo pl.dtbo > /configfs/device-tree/overlays/camera/path

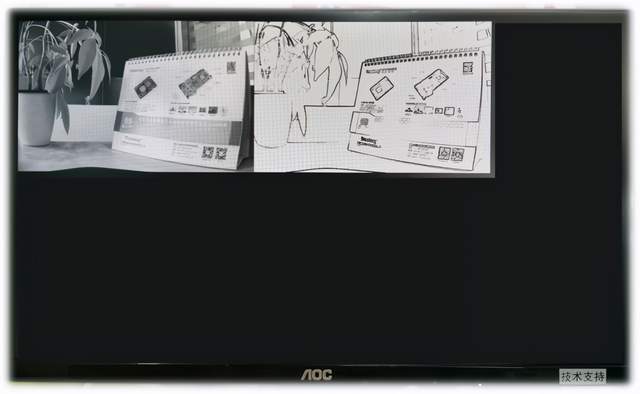

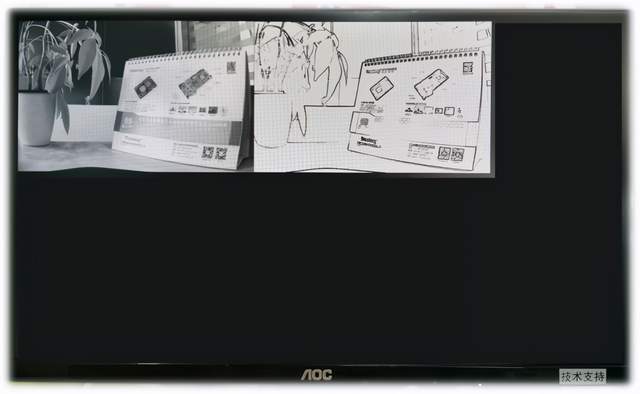

将案例"swlinux_systemimage"目录下所有脚本文件拷贝至评估板文件系统,并执行如下命令,即可看到HDMI显示屏输出两路图像。

Target# ./mt9v034_init.sh

Target# ./axi_vdma_init.sh

Target# ./sobel_filter_init.sh

Target# ./mixer_init.sh

Target# ./vpss_init.sh

Target# ./sil9022_i2c_1080p.sh

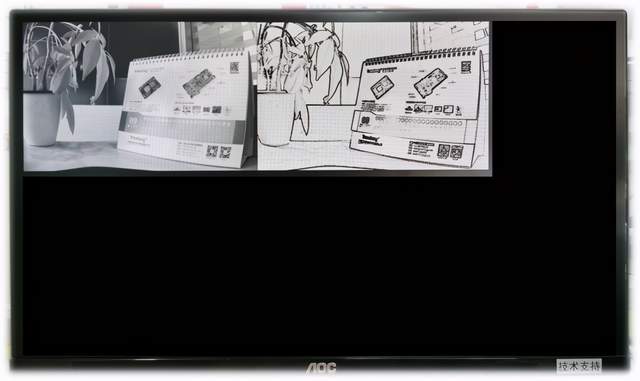

执行如下命令增大阈值,此时图像边缘将会增多,图像线条将会变粗。

Target# devmem 0x43c000b4 w 0xff //设置高阈值为0xff,默认为0xa0

Target# devmem 0x43c000bc w 0xa0 //设置低阈值为0xa0,默认为0x00

执行如下命令设置颜色反转。

Target# devmem 0x43c000c4 w 1 //设置为1,边缘为白色;设置为0,边缘为黑色

3 Vivado工程说明

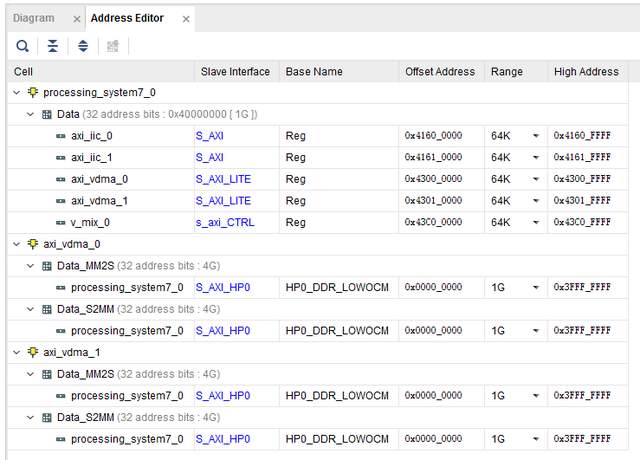

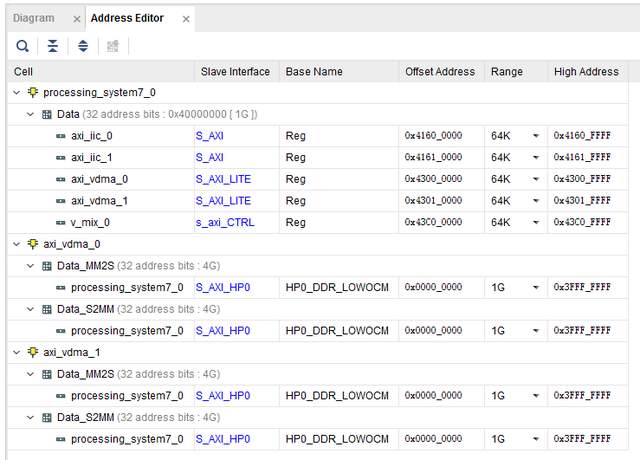

点击BLOCK DESIGN开发界面下的"Address Editor"选项,可查看IP核分配的地址,PS端可通过对应地址对IP核进行控制。

4 IP核配置

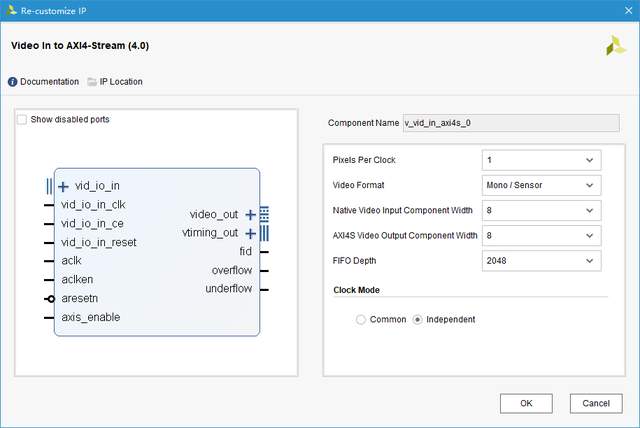

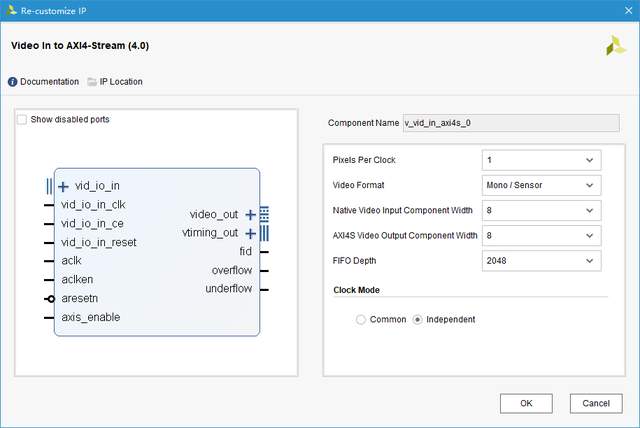

4.1 Video In to AXI4-Stream IP核

Video In to AXI4-Stream IP核可实现视频采集功能。

Video In to AXI4-Stream IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg043_v_vid_in_axi4s.pdf》。本案例使用IP核采集一路摄像头视频,Video Format配置为Mono/Sensor,Pixels Per Clock配置为1,色彩数据位宽为8bit。

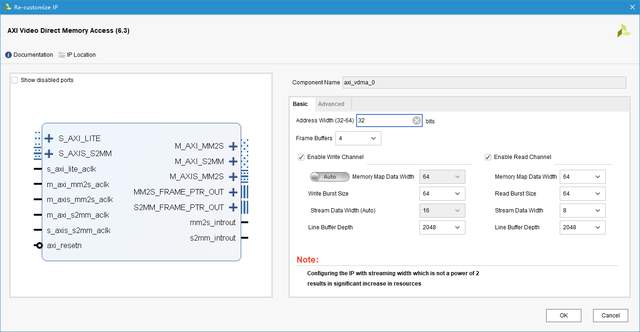

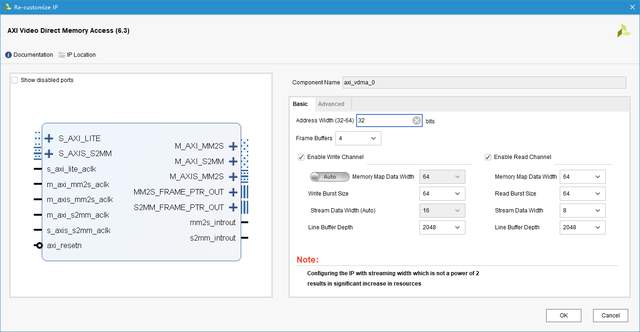

4.2 AXI VDMA IP核

本案例使用AXI VDMA IP核进行视频数据缓存。

AXI VDMA(AXI Video Direct Memory Access) IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg020_axi_vdma.pdf》。AXI VDMA IP核中的S2MM将视频传到DDR中,MM2S从DDR中获取视频。本案例IP核的Frame Buffers为4,Stream Data Width为8。

配置VDMA为读写跟随模式。

4.3 AXI4-Stream Broadcaster IP核

AXI4-Stream Broadcaster IP核将视频复制成两路。

AXI4-Stream Broadcaster IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《

pg085-axi4stream-infrastructure.pdf》,具体配置如下。

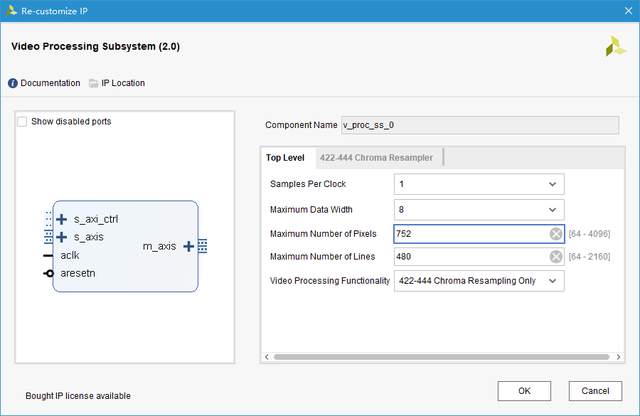

4.4 VPSS IP核

VPSS IP核可实现视频缩放、去交错、RGB/YUV转换、YUV420/422/444转换等功能,本案例使用YUV444转YUV422功能。

VPSS(Video Processing Subsystem) IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg231-v-proc-ss.pdf》,具体配置如下。

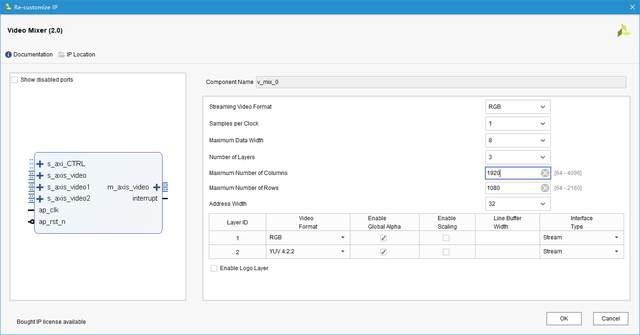

4.5 Video Mixer IP核

Video Mixer IP核可对多路视频进行叠加并输出。

Video Mixer IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg243-v-mix-v2.0.pdf》。本案例通过IP核将两路视频叠加到1920 x 1080的视频中,再输出至HDMI显示屏进行显示,具体配置如下。

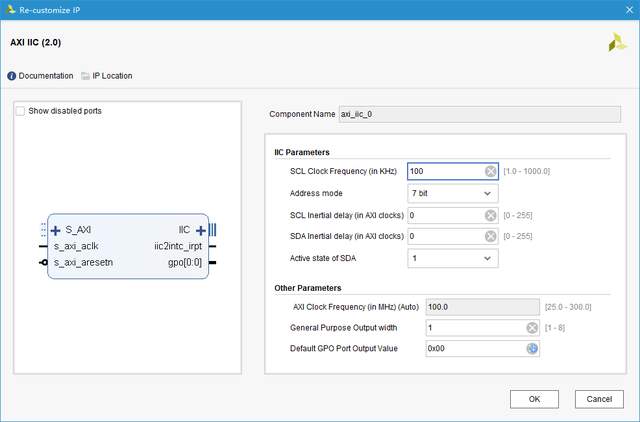

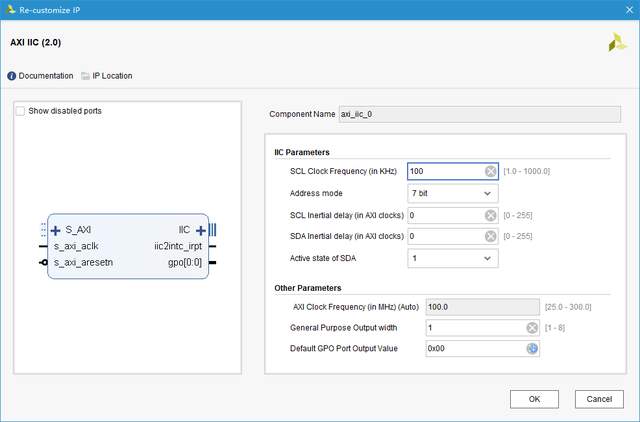

4.6 AXI IIC IP核

AXI IIC IP核可对摄像头进行配置。

AXI IIC IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg090-axi-iic.pdf》,具体配置如下。

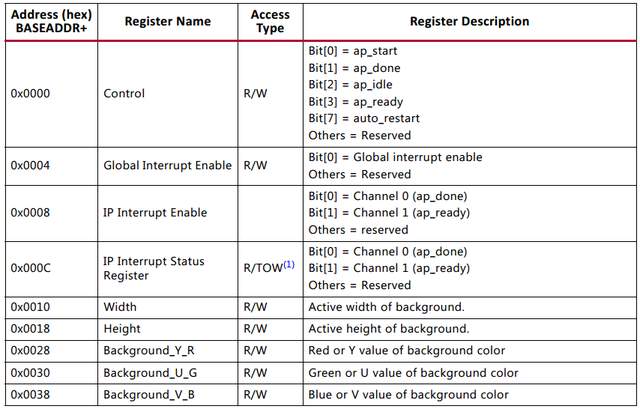

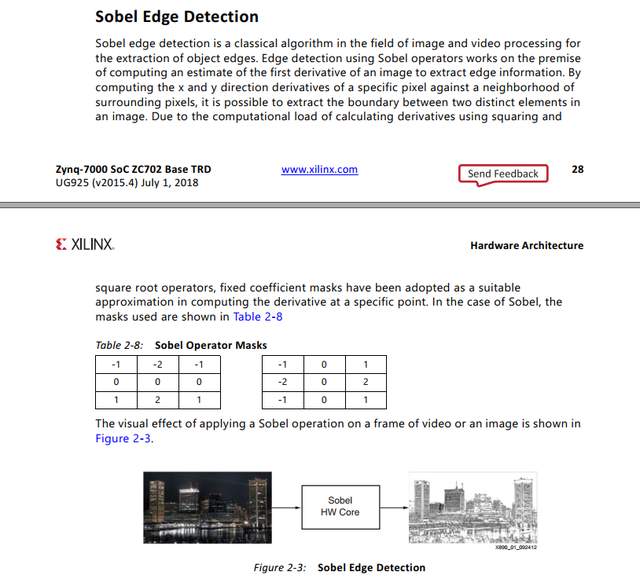

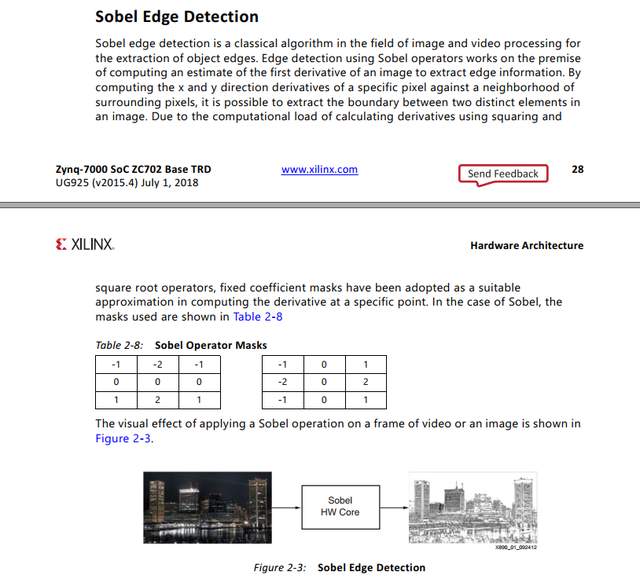

4.7 Image_filter IP核

Image_filter IP核可实现图像Sobel(边缘检测)算法处理功能。

Image_filter IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《

ug925-zynq-zc702-base-trd.pdf》。Image_filter IP核源码基于产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《xapp1167.pdf》文档中的Sobel(边缘检测)算法处理案例进行开发,对应的HLS源码位于产品资料“4-软件资料DemoZYNQ_DemoFPGA-HLS-demossobel_demo”目录下。

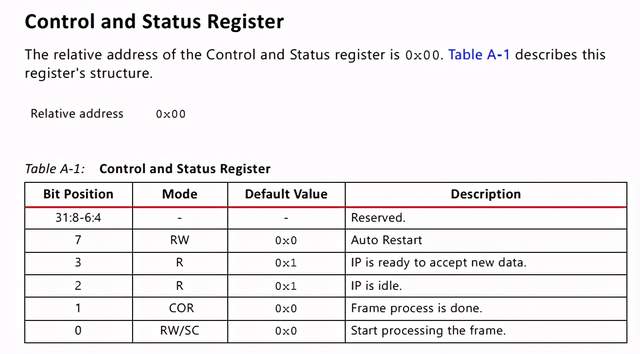

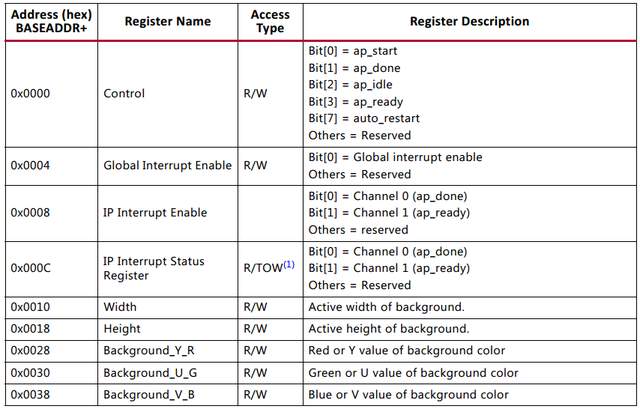

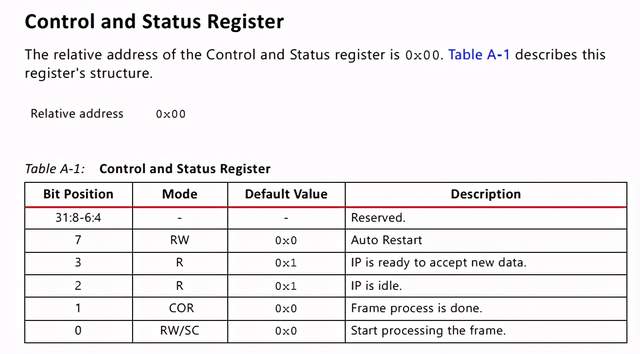

相关寄存器说明如下,寄存器定义可查看工程ximage_filter_hw.h文件。

(1) 寄存器0x00:控制和状态寄存器,可控制IP核的停止和启动。

(2) 寄存器0x14:设置图像的行数,最大支持1920 x 1080。

(3) 寄存器0x1c:设置图像的列数。

(4) 寄存器0xb4:Sobel滤波的高阈值。

(5) 寄存器0xbc:Sobel滤波的低阈值。

(6) 寄存器0xc4:反转Sobel滤波器的输出,即黑白反转。

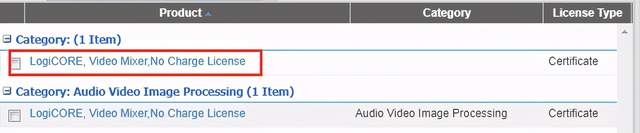

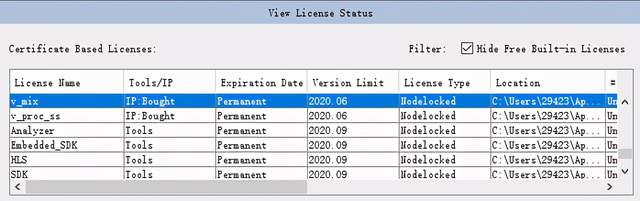

5 IP核License申请

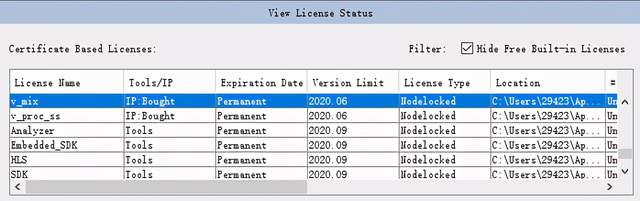

如需重新编译工程或打开Video Mixer IP核,需在Xilinx官网申请Video Mixer IP核的免费License,并将其正确导入。License申请与导入方法,请查阅调试工具安装文档相关章节,其他IP核无需License。

成功导入后,可在View License Status窗口发现新添加的License。

1

1

举报

举报