相关推荐

评论0

202 11

[1.2.6]--2.6QuartusII9.0软件激活

200 11

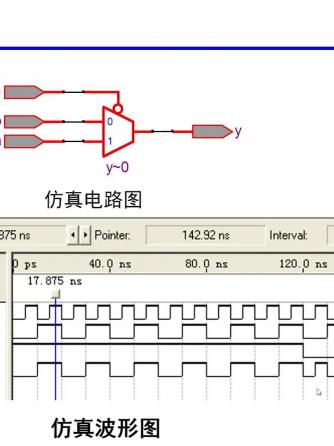

EDA技术与实验:2选1数据选择器实例(1)#EDA技术

199 11

[1.2.4]--2.4QuartusII软件获取方法二

199 11

[2.4.2]--4.3抢答器原理图设计输入

199 11

[4.4.4]--4.4计数器波形仿真

195 11

[3.4.3]--4.4数码管译码器工程分析综合、管脚分配与编译

193 11

[4.2.1]--2.1IF语句

193 11

[1.2.5]--2.5QuartusII软件安装

193 11

[5.4.6]--4.7秒表工程管脚分配与工程编译

193 11

[1.4.2]--4.3一位全加器原理图设计输入

193 11

[3.2.2]--2.2VHDL标识符与对象类型

193 11

[2.4.5]--4.6抢答器器件编程与开发板功能验证

192 11

[3.4.4]--4.5数码管译码器波形仿真

192 11

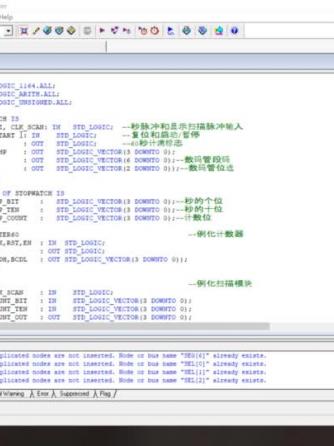

[5.4.2]--4.3秒表VHDL设计输入

190 11

[5.4.3]--4.4秒表60进制计数器波形仿真

189 11

[5.4.5]--4.6秒表整体功能仿真

188 11

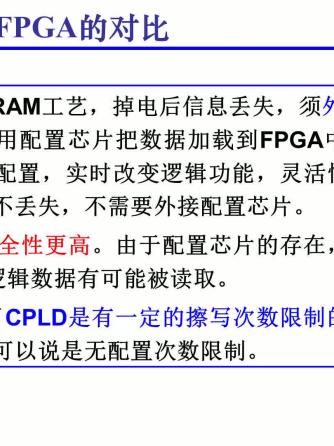

EDA技术与实验:1.2 CPLD 与FPGA比较(2)#EDA技术

188 11

EDA技术与实验:2选1数据选择器实例(2)#EDA技术

185 11