ADC基础知识科普

模拟技术

描述

1.1 概述

ADC(Anlog to DigtialConverter, 模数转换器), 用于实现模拟信号向数字信号的转换。自然界中的声光电等都是模拟信号,我们这里说的主要是电信号。而计算机系统只能处理二进制0和1这种信号,不能直接处理模拟信号,因此需要ADC将模拟信号转换为数字信号,然后进一步处理。ADC是模数之间的桥梁。

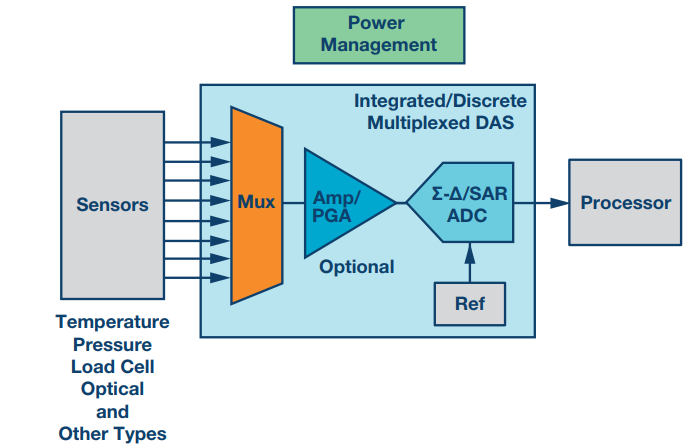

如上图是一个典型多路复用数据采集系统,在这个系统中,可使用多个传感器(Sensors)采集信号,并将多个输入通道扫描至单个ADC中。ADC对传感器采集的模拟信号进行模数转换,将转换结果数字信号通过串口(常见的一般是SPI、IIC等接口)送给处理器(Processor)使用,这就是一个典型的ADC使用场景。当然,在某些情况下,可使用在复用器(Mux)和ADC之间的缓冲器或可编程增益放大器对信号进行预处理,然后交由ADC处理。

1.2 ADC基础知识

主要介绍ADC分类,使用场景及AD转换基本原理。

1.2.1 分类

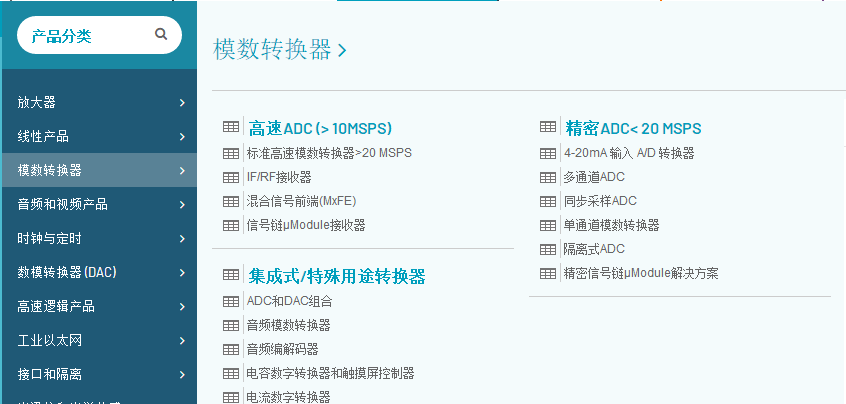

ADC的种类很多,按照不同的分类方法,可分为不同的类型。按照使用场景分,可以分为高速ADC、精密ADC、集成式/特殊用途ADC。

按转换实现的方法分,有逐次逼近型(SAR)、Σ-Δ型、积分型、压控变换型、流水线型等。

1.2.2 不同ADC的应用场景

逐次逼近型(SAR)、积分型、压控变换型等主要用在中低速、中等精度数据采集中。分级型和流水线型主要用于处理高速瞬态信号、快速波形存储与记录、高速数据采集、视频信号量化及高速数字通讯技术等领域。Σ-Δ型ADC主要应用于高精度数据采用的系统,多用于测量领域。芯海科技ADC就是此种类型,可用于于体重秤、严控芯片等场景。

1.2.3 ADC转换的过程

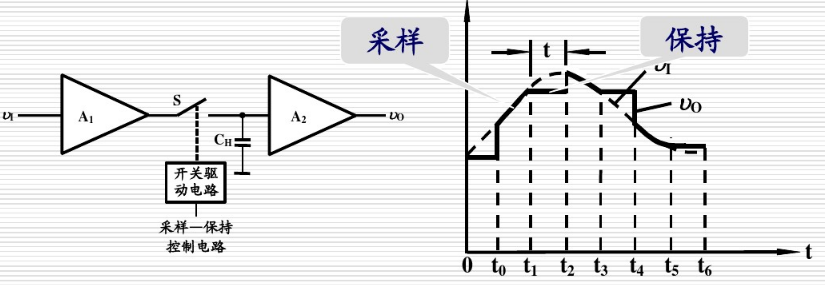

ADC采样过程分为4步,即采样、保持、量化和编码。

采样,将随时间连续变化的模拟信号转化为在时间t上离散的模拟量,采样需满足采样定理(奈奎斯特定理)。保持,模数转换都会消耗一定的时间,为了给后续的量化编码提供一个稳定的值,在采样威廉希尔官方网站 后要求将所采样的模拟信号保持一段时间(模拟上通过电容实现)。

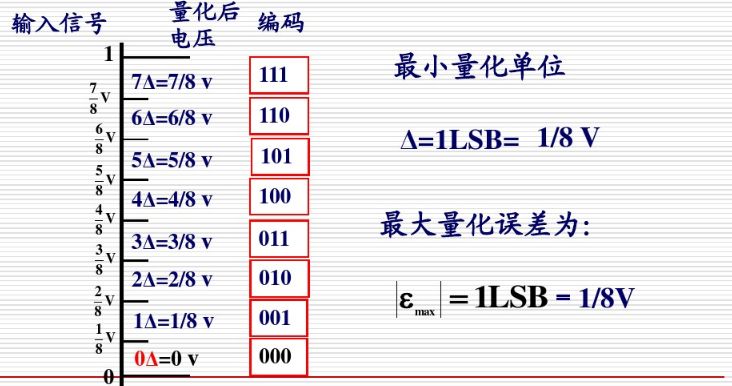

量化,数字信号在时间和幅值上都是离散的,因此采样-保持威廉希尔官方网站 的输出电压,还需按某种近似方程归化到相应的离散电平上,这一转化过程称为量化。编码,量化后的数值还需通过编码用一个二进制代码表示出来,经过编码后得到的就是AD转换结果的数字量,二进制编码的位宽等于ADC的位宽。上图示例是一个3 bit ADC,只舍不入量化方式(量化中把不足一个单位的部分舍弃),量化位数用3 bit来表示连续信号的幅值。信号满量程为0~1V,因此最小量化单位Δ=1V/2^3=1/8V。量化位数越高,ADC的分辨率越高,量化误差越小。一般ADC的分辨率使用LSB标识。

1.2.5 常见基本概念和参数

1) 位宽

即前一节提到的量化位数,常见的有8bit,10bit,12bit,16bit,24bit。比较少见的部分高速ADC有6bit~8bit。

2) 分辨率

ADC所能分辨的最小量化信号的能力,最小分辨能力Δ=输入满量程电压/2^N。分辨率主要由ADC的位数(输出数字量的位数)决定,也与输入满量程有一定的关系。如一个输出满量程为0~5V的ADC、8位的ADC,其最小变化量为5V/2^8,约为19.5mV。若将ADC的位宽增加为10位,则ADC的最小变化量为5V/2^10,约为4.88mV。

3) 量化误差Σ

在量化过程中由于所采样的电压不一定能被Δ(最小量化单位)整除,所以量化前后存在一定误差,此误差称为量化误差。量化误差属于原理误差,无法消除,理论上转换器的位数越高,各离散电平之间的差值越小,量化误差就越小。

4) INL

INL (IntergerNonLinear, 积分非线性), 指ADC实际转换曲线与理想曲线在纵轴方向的差值,单位LSB,用于表示实际转换曲线与理想的偏差程度。

5) DNL

DNL (DifferentialNonLinear, 微分非线性), 指ADC的实际量化台阶与对应于1LSB的理想值之间的差异。理想ADC偏差为0LSB。若DNL<1LSB,意味着传输函数具有单调性,没有丢码。

6) SNR

SNR (Signal NoiseRatio,信噪比), ADC输出信号功耗和噪声功耗的比值,用dB表示。SNR=10*log(P_signal/P_noise),其中信号频谱图中基波分量有效值,噪声=总能量-信号能量和谐波能量。理想ADC的噪声主要来自量化噪声。

1.3 SAR型ADC原理

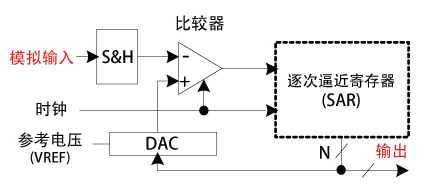

SAR(Successive Approximation, 逐次比较型), 包括一个比较器,一个数模转换器、一个逐次逼近寄存器(SAR)和控制逻辑单元。将输入的模拟信号与已知电压(DAC,数模转换)不断进行比较,一个时钟周期完成一次转换,N位的ADC需要N个时钟周期完成转换,转换完成后输出二进制。

从上面描述可以看出,此种ADC有个问题,位宽越宽,转换需要的时钟周期越多,即如果想提高ADC分辨率,会限制采样速率。所有此种ADC一般用在低速场景。

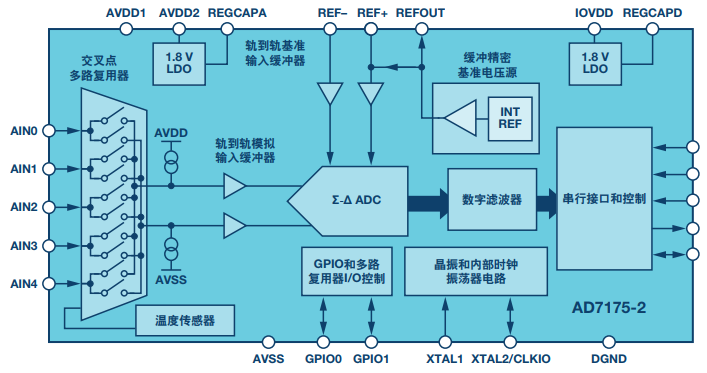

1.4 Σ-Δ型ADC原理

Σ-Δ型(Sigma-Delta-Converter, Σ-Δ型模数转换器), 又称为过采样转换器,它采用增量编码方式,根据前一量值与后一量值的差值的大小进行量化和编码。Σ-Δ型ADC主要由Σ-Δ型调制器和数字滤波器组成。调制器主要完成信号抽样和增量编码,给数字滤波器提供增量编码。数字滤波器完成对Σ-Δ码的抽取滤波,把增量码转换成高分辨率的线性脉冲码调制的数字信号,因此抽取滤波器实际上相当于一个码型变化器。

Σ-Δ型ADC一般精度可以做到很高,24位ADC中很多是此种类型。

1.5 关于ADC的验证

1.5.1 可能的验证方式

从1.3节框图可以看出,ADC分为模拟部分和数字部分。因此推测大概有2种方式,一是用veriloga实现模拟部分功能模型,和数字部分一起,验证环境中将整块逻辑作为DUT进行验证;另一种方式是验证只验证数字部分,数字部分验证ok后提供代码给模拟设计工程师,模拟设计使用ams仿真器进行仿真。

1.5.2 数字验证项

抛开模拟,只看ADC数字实现部分,主要验证项可能有,CRG、寄存器、接口、功能等。

-

STM32H7的ADC基础知识和HAL库API2021-08-20 0

-

五分钟读懂WiFi基础知识2021-12-01 0

-

ADC【DSP基础知识】2016-01-06 462

-

ADC入门_基础知识2016-03-11 1029

-

有ADC和传感器的基础知识吗?2019-02-21 0

-

【科普】卷积神经网络基础知识2017-11-10 1724

-

电源管理基础知识电源管理基础知识电源管理基础知识2017-09-15 1525

-

模拟数字转换器(ADC)基础知识2018-06-05 1473

-

ADC转换器的基础知识详细资料说明2019-07-18 1191

-

模拟基础知识:处理SAR ADC输入驱动难题2021-11-05 2180

-

C语言基础知识科普2022-07-21 1896

-

高速ADC基础知识2023-04-15 2006

-

科普一下CAN总线的基础知识2023-05-16 3279

-

伺服环路ADC测试的基础知识介绍2023-08-21 1449

-

电气基本知识科普2023-09-09 6127

全部0条评论

快来发表一下你的评论吧 !