表面终端金刚石场效应晶体管的研究

模拟技术

描述

摘 要

金刚石因具有极高热导率、5.5eV宽带隙、极高击穿电场、高固有载流子迁移率和低介电常数等优异性能,在高功率、高频、高温及低功率损耗电子器件领域中成为有力的竞争者。然而,研究人员对金刚石半导体掺杂技术进行了几十年的探索和优化,却仍然无法满足当前电子器件的应用需求。最近,随着H终端金刚石表面二维空穴气的发现,研究重心逐渐转向优化H终端金刚石的导电特性及制备场效应晶体管(FET)。综述了H终端金刚石研究的发展历程,从栅层材料选择、表面终端处理、金刚石掺杂和FET结构优化出发,归纳了提升表面终端金刚石FET器件性能的方法,并对表面终端金刚石FET的发展前景进行了总结和展望。

研究背景

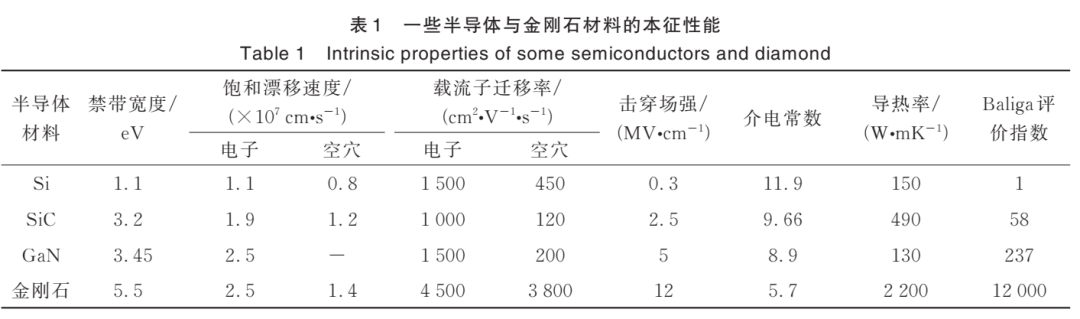

金刚石不仅具有包括最高的硬度、极高的热导率、达5.5eV的宽带隙、极高的击穿电场和高固有载流子迁移率等多种卓越性质[1-2],同时还具有耐化学腐蚀、耐高温、抗辐照能力强和表面稳定性高等优点,因此它在大功率器件、精密加工、热管理、量子传感、污水处理、生物传感等领域得到了广泛应用[3-5]。Si、第三代宽禁带半导体SiC、GaN和金刚石材料[1-2]的基本参数和Baliga高频评价指数[6]列于表1。由表1可知:金刚石在下一代高功率、高频、高温及低功率损耗电子器件中具有极为显著的优势,故其被业界誉为“终极半导体”。

几十年来,研究人员一直试图在各种电子设备应用中实现金刚石的理想性能。与大多数半导体材料一样,金刚石材料必须进行杂质掺杂,以获得稳定的高载流子浓度,但对金刚石进行n型掺杂的研究结果一直不太理想[7]。掺S的金刚石晶格畸变较多,降低了S的电活性[8],且低温时会呈现p型导电[9];而N和Li掺杂后均为深杂质能级,通常为绝缘体[10-11];P掺杂会在金刚石中形成导带底下0.58eV的杂质能级[12],且掺杂后的载流子迁移率很低。目前,虽然有一些研究表明[7,13-15],复杂掺杂物可以实现金刚石的n型掺杂,但都难以重复和应用。

在p型掺杂方面,使用B作为掺杂元素是最常见的方法。然而,B掺杂金刚石后的电离能约为0.36eV,这意味着即使在室温下仍然难以电离,导致载流子浓度较低[16]。而高浓度B掺杂会导致空间电荷效应,从而降低载流子迁移率[17],影响导电性能,并降低金刚石的晶体质量。因此,尽管B掺杂金刚石的工艺相对成熟,且已在污水处理、传感器等行业中得到了广泛应用[18],但其在电子器件领域中的应用仍然受到限制。

近年研究发现,将H终端金刚石表面与气体分子、氧化物、电荷等接触,进行转移掺杂后,可以形成良好导电特性的二维空穴气(Two Dimensional Hole Gas,2DHG),这提供了1种金刚石半导体应用的新途径,同时避免了传统掺杂带来的严格限制[6]。H终端金刚石非常适合平面器件的制备,效应晶体管(Field EffectTransistor,FET)是其应用最广的领域。本文首先综述了近年来H终端金刚石FET器件的研究和发展情况,包括H终端金刚石的发现历程及二维空穴气的产生机理。然后,从栅层材料的选择、表面终端处理、金刚石掺杂和FET结构优化等方面入手,总结了目前研究中对H终端金刚石的优化方向和进展。最后,展望了表面终端金刚石FET器件未来的发展前景。

1 H终端FET的历史发展

1.1 气体分子

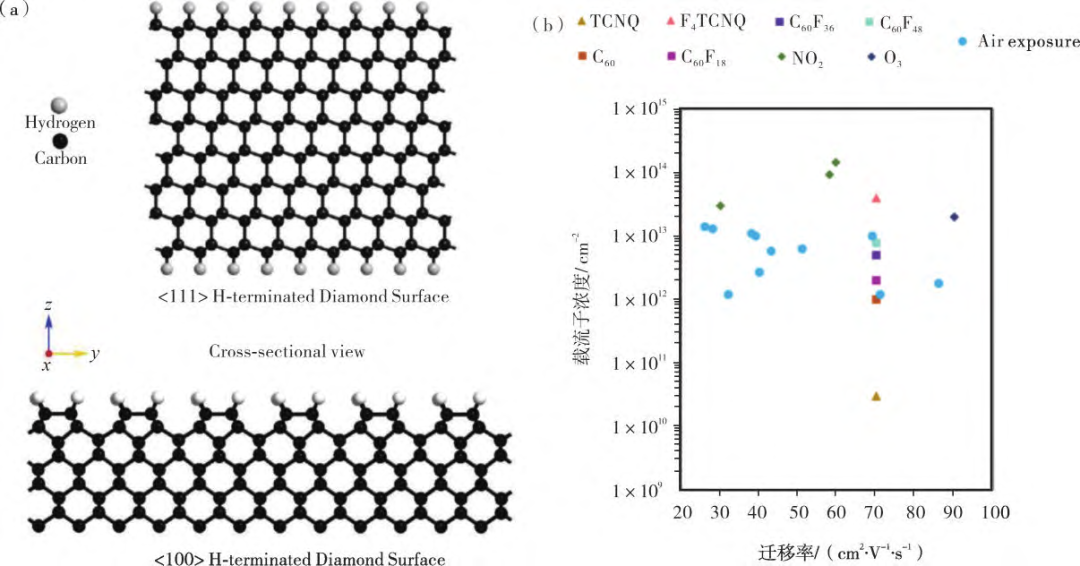

虽然金刚石半导体的B掺杂研究较为成熟,但B的激活能较高,常温下难以电离,限制了其在电子器件领域的发展[16]。最近的研究发现,H终端金刚石(见图1)具有p型导电,这引起了研究人员的广泛关注。

1989年,Landstrass 等[19]研究发现,未使用任何杂质掺杂技术制备的H 终端金刚石表面电导率为1×10-6 Ω-1⋅cm-1。Gi 等[20-21]通过实验证明了电子转移依赖于 H 终端金刚石的环境气氛,并有实验表明 H 终端金刚石表面存在负电子亲和势[22],其导电表面下存在空穴积累层[23]。Maier 等[24]进一步证实了由于表面存在的空气分子能够作为电子受体,H终端和环境空气暴露能够增强金刚石表面的电导率。 经过长时间的理论发展和实验探索,金刚石氢终端表面的转移掺杂导电机理得到了广泛认可。

当H 终端与水蒸气接触时会形成水合氢润湿层,润湿层会吸附一些低非占据电子能态的气体(氧气、甲酸、二氧化碳等),价带电子向低非占据能态吸附层的跃迁,使亚表面层积累足够多的空穴,最终形成导电的二维空穴气(2DHG),从而实现金刚石表面导电[6,25]。 选用不同的气体分子作为掺杂物会明显影响 H终端金刚石的电导率,H 终端金刚石的导电特性波动十分巨大,其迁移率和典型载流子浓度的变化范围分别为 20—100cm2 ⋅V-1 ⋅s-1 和 1×1012—1×1013cm-2[26-27]。这可能是由于存在太多难以控制的变量,如金刚石表面形态、H 终端密度、表面污染、自然发生的大气吸附物、衬底组成和金刚石晶体质量等。空气掺杂 H 终端金刚石的电学特性差异大,但2DHG 的载流子密度很少超过 1×1013 cm-2。

相比于空气吸附转移掺杂,直接选用特定气体分子作为转移掺杂物可显著提高 H 终端金刚石的导电特性(见图 1)。富勒烯分子 C60 及其氟化变体具有较高的电子亲和势,是首批 H 终端金刚石上的电子受体分子之一。C60 作为转移掺杂物时,H 终端金刚石的空穴载流子浓度与空气暴露产生的相当[28-29]。此外,Riedel 等[30]研究发现,在臭氧环境下进行退火可增强 H 终端金刚石表面导电性,这是因为臭氧可能产生部分 O 终端,导致局部键合,消除或降低了电子交换的势垒,提高了表面导电性[30]。 虽然选用特定的气体分子可以提高 H 终端金刚石的电导率,但分子吸附层本身稳定性和均一性很低的问题依旧没有解决,难以应用于电子器件。

1.2 金属氧化物

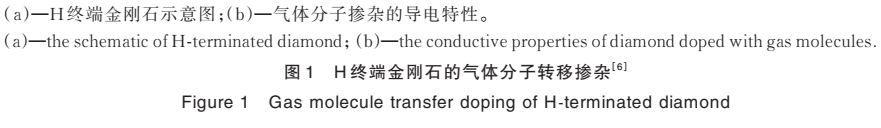

为了综合提高 H 终端金刚石材料作为电子器件的稳定性和导电性,人们将研究重心逐渐转向许多固体包封材料,其中金属氧化物最为普遍。高电子亲和势(ElectronAffinity,EA)和功函数的过渡金属氧化物(TransitionMetalOxides,TMOs)已被证明是有效的 H 终端金刚石表面掺杂物。 当转移掺杂物的电子亲和势较高时,表面电子受体导带位于 H 终端金刚石价带下方,费米能级对齐会导致能带向上弯曲从而在金刚石表面形成2DHG,这一发现引起了众多学者的广泛关注。2013 年,Russell 等[31]研究发现,三氧化钼(MoO3)可以诱导转移 H 终端金刚石表面电子,使 2DHG 载流子浓度提升了一个数量级,且在金刚石/MoO3 界面中发现了清晰的电荷分离。

之后,五氧化钒(V2O5)[32-33] ,三氧化钨(WO3)[32,34],三氧化铼(ReO3)[23,34],五氧化铌(Nb2O5)[32]和三氧化铬(CrO3)[35]等相继被用作掺杂物。其中 MoO3、V2O5 和 WO3 的载流子密度超过1×1014 cm-2[32,34],V2O5 和 MoO3 可在 300℃ 下实现高温稳定性[26,36],而 ReO3 可达 400℃[34]。相比于气体分子,TMOs 是 1 种更有吸引力的电子转移掺杂物,它们可在更大的温度范围内具有更强的稳定性,并且在由具有可控性能的固体材料驱动下,可产生稳定可靠的高载流子浓度。图 2 为与金刚石带隙有关的 TMOs 材料导带的比较[6]。

后续实验发现,在不引入其他气体分子或表面终端时,具有较低EA 的 Al2O3 依然能够作为 H 终端金刚石的转移掺杂物,产生 2DHG[37]。这一现象引起了学者们的讨 论,可能的解释有两种:其一为ALD 技术制备 Al2O3 层会产生间隙氧和 Al 空位[38];其二为 Al2O3 与 H 终端金刚石存在相互作用键合[39]。这两种解释都能与实验较好符合,同时表明了电荷掺杂和键合也可以在 H 终端金刚石表面产生 2DHG。 这些金属氧化物大多就是 FET 器件中较为常用的栅层材料,制备工艺较为成熟,且稳定性良好,这一发现极大地促进 了 H 终端金刚石在电子器件领域的发展。

1.3 金属电极接触

尽管 H 终端金刚石半导体材料已经具有良好的导电性、环境稳定性和热稳定性,但使其应用于电子器件领域,还需要研究其与金属等电极材料的接触特性。 1994 年,Aoki 等[40]研究了 CVD 制备的 H 终端金刚石表面与各种金属的接触特性,结果表明,界面肖特基势垒高度(schottkybarrierheight,SBH)与 H终端金刚石表面沉积金属的功函数有很强的相关性。这是由于 H 终端金刚石表面可降低费米钉扎,使得其表面状态受到金属功函数的影响,高功函数金属在 H 终端金刚石上表现出线性欧姆响应,而低功函数金属被用于产生与大肖特基势垒的接触[41-42]。

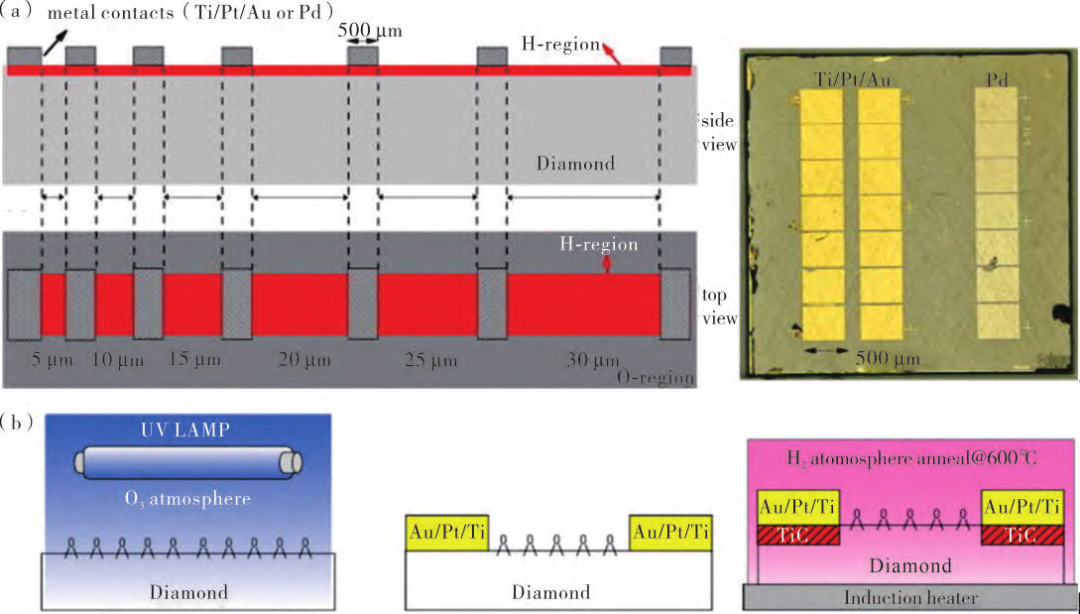

在 MOSFET 器件中,源漏级的金属电极需要与 H 终端金刚石具有较好的欧姆接触。具有较高功函数的 Au、Ag、Cu、Ir、Pt 和 Pd 被证明可以在 H终端金刚石表面产生欧姆接触(见图 3(a)),是备选的 H 终端金刚石 FET 的金属电极[43-48]。这些金属中,由于 Au 用于电子器件领域的沉积工艺较为成熟,它成为了 H 终端金刚石上最常用的欧姆接触电极[47-49]。

此外,一些研究表明部分碳化物同样可以与 H终端金刚石实现欧姆接触[50-51]。Jingu 等[50]首先将Ti 制备在 O 终端金刚石上,然后用氢等离子体金刚石进行处理以获得 H 终端,最后测得 TiC 与金刚石的最终接触电阻约为9Ω⋅mm,TiC 与 H 终端金刚石接触的制备流程如图 3(b)所示。Vardi 等[51]研究了由钨形成的碳化物接点,其接触电阻为 2.6Ω⋅mm,且具有良好的机械稳定性。这些研究还表明,碳化物接触电极可以在氢等离子体暴露下稳定存在。 因此,高功函数金属和碳化物可以与 H 终端金刚石实现欧姆接触,且工艺较为简单集成,可以作为FET 器件的源漏电极。

1.4 H终端MOSFET实现

随着H终端金刚石材料的研究日益深入,其电子器件的设计开发呼之欲出,其中FET是最被关注的领域。 在1994年,Kawarada等[52]使用CVD生长的H终端金刚石衬底(100),通过空气暴露转移掺杂实现导电性,结合Al栅极的肖特基栅、Au源漏极的欧姆接触,首次实现了H终端金刚石三端增强型FET 的制备。该器件的栅极长度为 10µm,其最大漏极电流为1.6mA⋅mm-1,非本征跨导高达200µS⋅mm-1;将栅极长度增加到41µm,由于更大栅极的耗竭区域增加,可以完全关闭器件,进而将非本征跨导降低到20µS⋅mm-1,最大漏极电流降低到0.14mA⋅mm-1。这项工作开创性地验证了将H终端金刚石用于电子领域的潜力,从这项工作开始,利用H终端金刚石转移掺杂的FET技术得到了长足的发展。

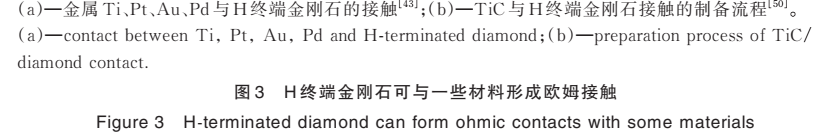

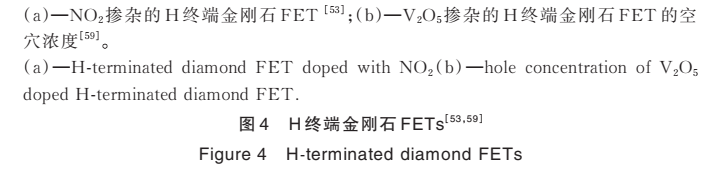

使用气体分子作为转移掺杂物可以产生2DHG,有 望借此制备出 H 终端金刚石 FET 器件。但气体分子的稳定性较差,于是部分研究者利用Al2O3等绝缘层对 H 终端表面进行钝化封装,提高了气体分子转移掺杂产生 2DHG 的稳定性[53-54]。NO2作为转移掺杂物时的空穴浓度比空气掺杂时要高一个数量级[55-56],是较优的气体分子转移掺杂物。2022 年,MakotoKasu 等[53]在高质量异质外延金刚石衬底上使用 NO2 作为转移掺杂物,利用 Al2O3 进行钝化封装,制备了 H 终端金刚石 MOSFET(见图4(a))。该器件具有 7.54mΩ⋅cm2 的低比导通电阻和0.68A⋅mm-1的高漏极电流密度,沟道关闭状态下的击穿电压高达-2568V,器件还具有 874.6MW⋅cm-2的最大可用功率密度,达到了当时金刚石器件的最高报告值。后续,他们进一步优化工艺,将击穿电压进一步提高到了-3326V[54]。

钝化封装技术一定程度上提高了气体分子掺杂后器件运行的稳定性,但这不仅增加了制备工艺,也依旧难以保证掺杂后 FET 器件的均一性。而在 H终端金刚石表面直接沉积氧化物实现转移掺杂,既简化了制备工艺,又保证了 FET 的稳定性和均一性[57]。Colangeli 等[58-59]利用 V2O5 制备了器件,研究了不同金刚石晶面制备的 FET 的空穴浓度(见图 4(b)),其高电子亲和势允许 H 终端金刚石产生2DHG。Liu 等[60]利用电子束蒸发技术直接在 H 终端金刚石上生长 Y2O3 氧化物绝缘体,制备了增强型H 终端金刚石 FET,Y2O3 薄膜中的正电荷可能补偿了空穴积聚,使得 FET 具有明显的常关特征,最大漏源电流为 114.6mA⋅mm-1。

2 表面终端金刚石FET 的研究现状

在大多数情况下,H 终端金刚石 FET 表现出常开特性,难以实现安全、节能和逻辑威廉希尔官方网站

的应用,特别是由耗尽模式和增强模式组成的 H 终端金刚石NOT 和 NOR 逻辑威廉希尔官方网站

,因此迫切需要研制增强型H 终端金刚石 FET[61]。此外,为了提升器件性能以 满足不同的应用需求,研究者们通过对栅层的制备、表面终端、金刚石掺杂、FET 结构等方面研究,优化了金刚石 FET 的阈值电压、载流子浓度、载流子迁移率、击穿电压等。

2.1 栅介电层材料

2.1.1 铁电栅层材料

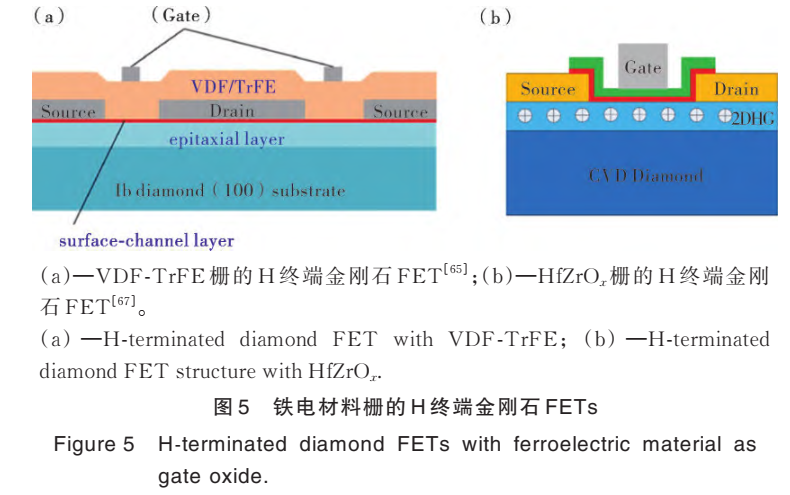

铁电材料作为 FET 的栅层时,其负电容特性可以大幅降低亚阈值摆幅,使其小于传统 MOSFET器件的玻尔兹曼极限 60mV⋅dec-1[62],提高了 FET的开关速率。此外,铁电材料具有剩余极化,有望同时实现无外加电场时保持 FET 器件的开关状态。 2009 年,Liao 等[63-64]首先使用 Pb(Zr0.52,Ti0.48)O3(PZT)铁电材料作栅,Al2O3 作为绝缘层,掺硼单晶金刚石半导体制备了 FET,可应用于非易失性存储器和微机电加工技术。传统铁电材料 PZT 等的复杂制备工艺容易破坏 H 终端金刚石表面[65],要求插入绝缘层以提高铁电材料质量,而 2DHG 进一步缩小了绝缘层材料的选择,这严重限制了 H 终端金刚石的铁电 FET 发展。相比于 PZT,有机铁电材料聚偏氟乙烯(poly(vinylidenefluoride),PVDF)及其共聚物为柔性薄膜,其制备简单、化学惰性好且受界面问题影响较小[66]。 2016 年,Kawae 等[65]使用偏氟乙烯(VDF)-三氟乙烯(TrFE)共聚物铁电材料作为栅极,制备了H 终端金刚石 FET(见图 5(a))。

当栅极电压从 20V扫至-20V 时,饱和漏极电流最大值为 50mA⋅mm-1,最大开关电流比和线性迁移率分别为 108 和398cm2⋅V-1⋅s-1;此外,通过 VDF-TrFE 栅极的剩余极化调制 FET 结构的漏极电流,在不施加直流栅极电压的情况下获得了 103的开关电流比。 HfZrOx 铁电材料进一步克服了其他铁电材料难以集成、需要高温退火、高工作电压、大厚度等缺点。Zhang 等[67]首次展示了一种具有铁电 HfZrOx/Al2O3 堆叠栅极介质的 H 终端金刚石负电容 FET[67](见图 5(b))。在 7.3—9.2V 宽的记忆窗内,测得的最大开关比为 109,栅电压从-10.0V 到 10.0V,亚阈值摆幅约为 58mV⋅dec-1,小于玻尔兹曼极限。这些结果表明,HfZrOx/Al2O3/H 终端金刚石 FET 为金刚石增强型 FET、负电容 FET 和高密度集成非易失性存储器提供了新的可能性。

2.1.2 其他栅层材料

一些栅层材料因其优异特性在Si 半导体器件、热离子电子源等领域有所应用,这些栅层材料的选用可能会简化 H 终端金刚石器件的制备工艺,制备增强型 FET,优化其导电特性[68]。 金属 Y 的功函数较低且沉积工艺简单,不会破坏金刚石的表面终端,是增强型金刚石 FET 的候选栅层材料。Zhang 等[69]首次将 Y 应用于 H 终端金刚石 FET,Y 和金刚石间有 10nm 厚的 Al2O3 介电层。在栅极电压为 7V、漏极源电压为 20V 时,栅极长度为8µm 的 FET 的最大漏极源电流为-53.9mA⋅mm-1,电流开关比超过 109,亚阈值摆幅为 198mV⋅dec-1。但较厚的介电层导致 FET 仍为常开模式,因此该组进一步优化了介电层厚度,分别采用了 5nmAl2O3介质层[70]和无介电层[71]方案,成功制备了常关 Y 栅金刚石场 FET。

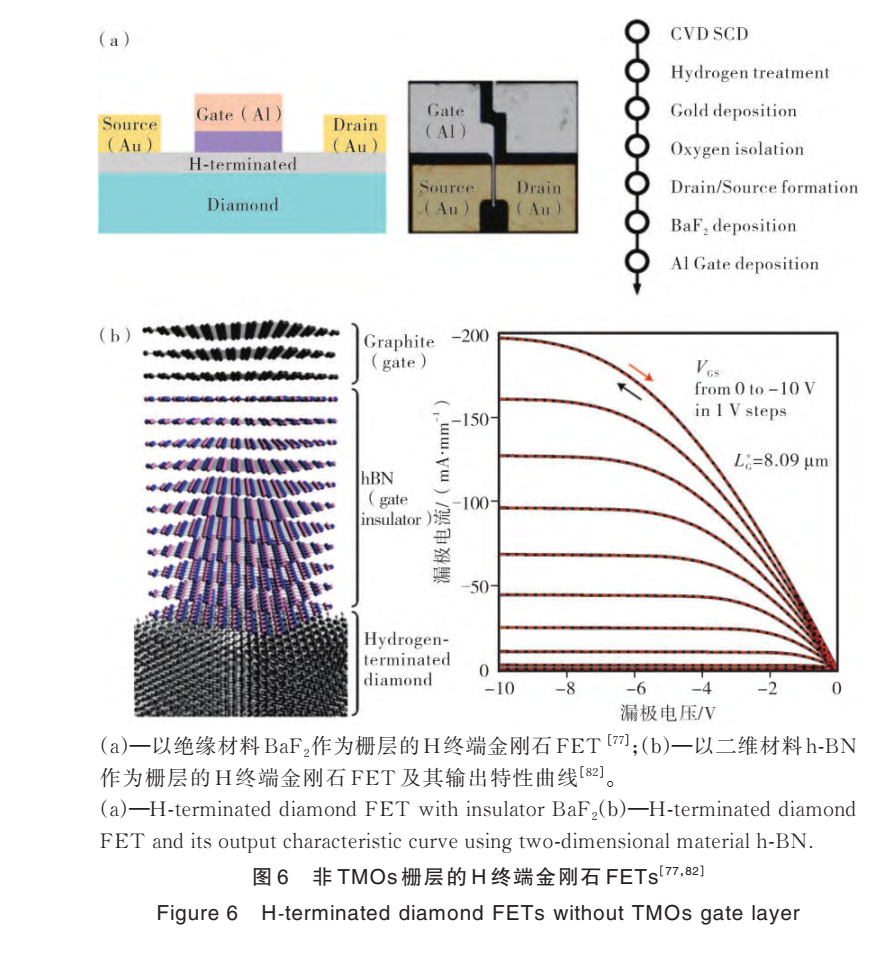

然而,随着介质层的降低,FET 的阈值电压提高且在大电压下栅层易被击穿,限制了Y 栅 FET 的应用。 直接对金属进行氧化制备 H 终端金刚石 FET的栅层,可以简化制备工艺。Wang 等[72]利用 6 nm 厚的 Al 薄膜在室温空气中的自氧化制备了 AlOx层,实现了 H 终端金刚石 FET。AlOx介质层能有效降低泄漏电流,VDS =-15V 时,阈值电压为-0.4V。Zhang 等[73]利用电子束蒸发技术在 H 终端金刚石表面沉积了 5nm 的 Ti 薄膜,然后在 120℃的空气中热氧化 10h,形成 Ti/TiOx,成功制备了增强型金刚石 FET。在 VDS 为 -8V 时,FET 的阈值电压为-0.14V,Ti 和 H 端金刚石之间功差的不同,从而耗尽了 H 终端金刚石的空穴载流子,使得器件表现为常关特性。 六硼化镧(LaB6)具有低功函数、高熔点、低挥发性、低电阻率和高化学稳定性等特点,是热离子电子源领域的常用材料[74],Wang 等[75]采用 LaB6 制备了一种增强型 H 终端氢金刚石 FET,其产生增强模式的原因是 LaB6 层的电子流入 2DHG 沟道并对空穴进行补偿,导致导电沟道关闭。氟化钡(BaF2)薄膜是 1 种应用广泛的宽禁带能(10.6eV)绝缘材料[76],He 等[77]利用 Al/BaF2 栅极材料制备了高性能增强型金刚石 FET(见图 6(a))。该增强模式主要是由于栅极金属对通道的肖特基势垒损耗效应,其次是 BaF2 层中存在的正固定电荷。器件在 VGS 为-2.1V,有效空穴迁移率约为 225.0cm2⋅V-1⋅s-1。

为解决一些栅层材料制备工艺会破坏表面 H终端和栅层材料本身的问题,一些研究者提出了使用 Al2O3 作为过渡栅层[78]。Liu 等[79]研究了高介电常数材料 ZrO2/Al2O3 双分子层的能带结构、ZrO2/Al2O3 双分子层的击穿场强及栅漏距离对金刚石FET 性能的影响。他们还采用 ALD 制备 Al2O3 薄膜作为 TiO2 和 H 终端金刚石表面之间的缓冲层,抑制了等离子体放电效应,降低了漏电流[80]。但采用两种栅层材料不可避免地增加了 H 终端金刚石FET 的工艺流程,提高了制备成本。

目前使用的各种栅层与表面终端金刚石接触时,其转移掺杂形成的电离表面受体会产生空穴散射,降低了空穴迁移率,限制了表面终端金刚石器件的性能。而二维材料无悬挂键的特性可以提供更良好的界面状态,提高器件载流子迁移率。Sasama 等[81-82]以单晶六方氮化硼(h-BN)作为栅极电介质,制备了常态关的 H 终端金刚石 FET,并测试了输出特性曲线(见图 6(b))。界面处的表面受体密度降低,但 2DHG 具有较高的室温霍尔迁移率(680cm2⋅V-1⋅s-1),与其他 p 通道宽带隙 FET 相比,器件具有较低的片电阻(1.4kΩ)和较大的 ON 电流(1600µm⋅mA⋅mm-1),开关比为 108。但使用二维材料作为栅层会导致在大电压情况下,栅极可能首先被击穿,这会显著降低 H终端金刚石 FET 的击穿电压[82]。

2.2 表面端基

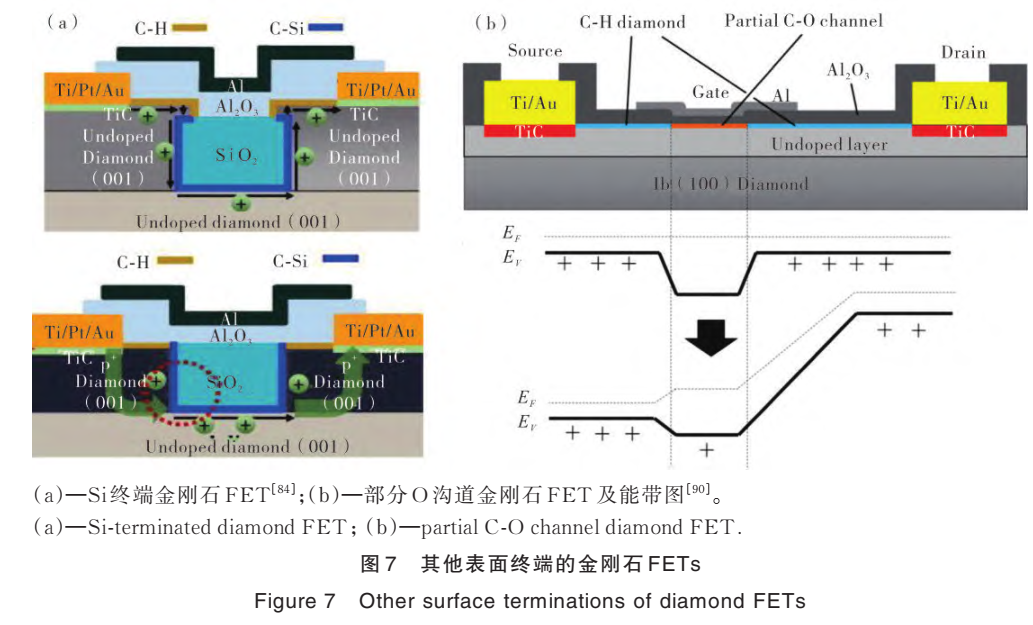

除 H 终端金刚石外,O、F、Si 等终端的金刚石也曾被广泛研究,他们的电子亲和势差别较大,因此改变金刚石表面终端构成,可以极大地影响 2DHG 的导电特性[83]。 相比于其他氧化物绝缘层,SiO2 具有最宽的带隙和更简单的制备流程,更有利于功率器件的制备与应用,因此对 Si 终端金刚石 2DHG 的性质及电场效应对其导电性的影响进行研究十分有必要[84]。2015 年,Schenk 等[85-86]研究了在真空 Si 终端金刚石的形成和表面表征,发现了氧化 Si 终端金刚石上的能带弯曲。 2020 年,Fei 等[84]在 SiO2 掩膜的选择性外延生长过程中,利用 Si 终端取代掩膜下金刚石原本的 O终端。研究发现:高温的选择性生长及还原气氛使SiO2 中的 Si 原子与金刚石表面相互作用,从而形成由金刚石表面单层或多层 C-Si 键组成的 Si 终端金刚石,利用 Si 终端金刚石制备的 FET 均表现出增强模式特性,且 Si 终端金刚石的导电性同样受到电场调制。

之后,浮现出了一些新的 Si 终端金刚石导电沟道的制备方法,Zhu 等[87]在还原气氛中对 SiO2 栅绝缘体进行退火,在(111)金刚石衬底上构建了金刚石/Si 界面,采用 Si 终端金刚石的导电通道制备了相应的 FET(见图 7(a)),检测表明 SiO2 薄膜和(111)金刚石之间界面良好,这确保了其较高的沟道空穴迁移率 200cm2⋅V-1⋅s-1 和较低的界面态密度3.8×1011 cm-2⋅eV-1。2022 年,Fu 等[88]利用分子束沉积技术实现原子尺度 Si 沉积,优化了 Si 终端金刚石的制备方法。与 H 终端不同,O 终端金刚石的电子亲和势高达+1.7eV[89],难以实现转移掺杂产生 2DHG,因此一些研究人员想到以此来制备增强型金刚石表面终端 FET[90-91]。Kitabayashi 等[90]利用氧化部分导电沟道制备了 H 终端金刚石 FET,该器件在室温下表现出超过 2kV 的高击穿电压和常断特性(见图 7(b))。Chen 等[91]采用 Al2O3纳米粒子掩膜的超强力臭氧工艺制备了部分 O 终端金刚石,与 Al/H 终端金刚石相比,Al/O 终端金刚石结构具有更高的 SBH,可以很好地抑制金刚石 FET 关闭状态下的漏电流。

2.3 金刚石掺杂与FET 结构

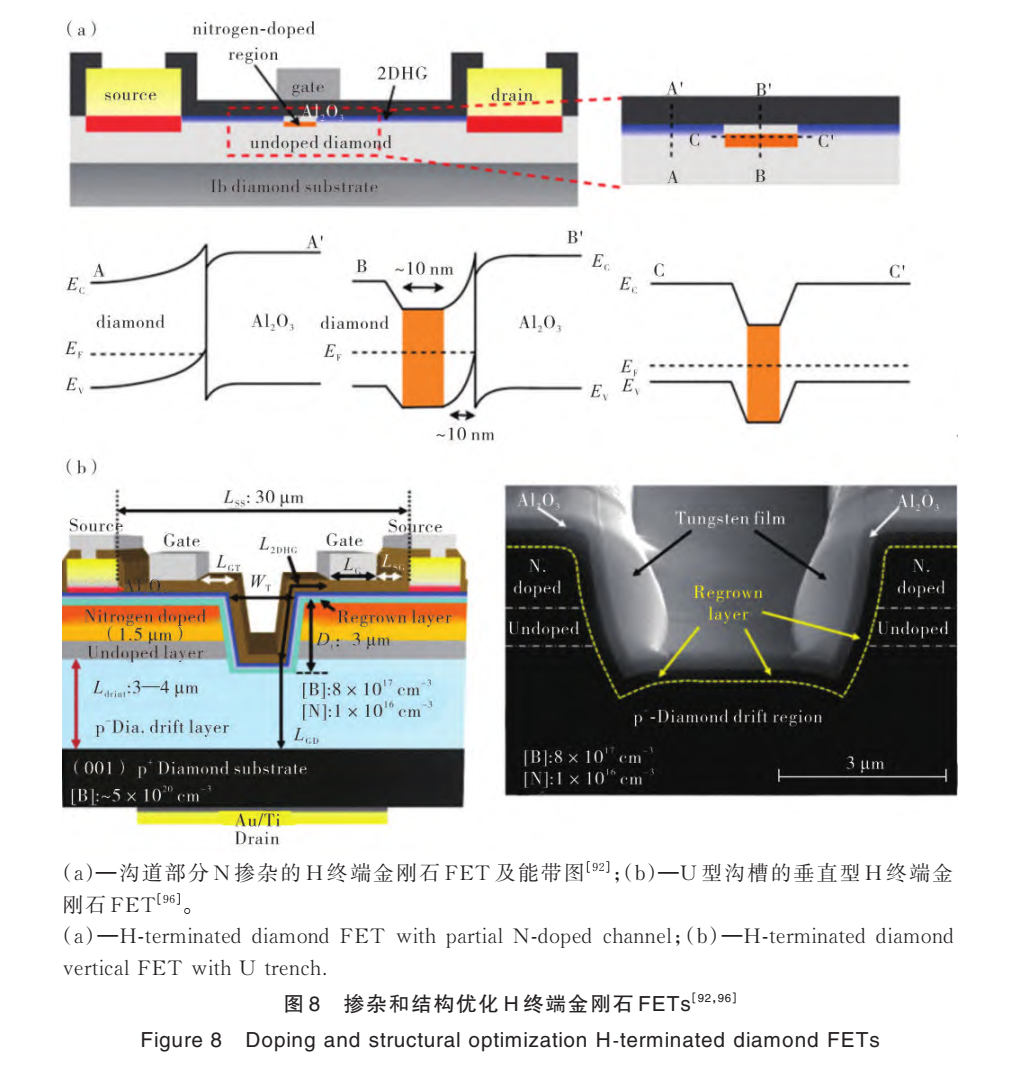

除了对金刚石表面终端和栅层的优化外,一些研究者通过改变金刚石 FET 结构,调控金刚石的掺杂[92-93]和晶体取向[59]等,从而优化表面终端金刚石 FET。对金刚石材料进行掺杂,可以显著改变其载流子浓度,调控 2DHG 导电特性,增加 FET 的耐击穿场强。Kawarada 等[92]使用离子注入在 H 终端导电沟道下方形成一层薄的 N 掺杂层,实现了增强型金刚石表面终端 FET(见 图 8(a))。N 是深层供 体(1.7eV),氮掺杂层抑制了近表面空穴的积聚,FET 的阈值电压高达-2.5V,室温击穿场强为2.7MV⋅cm-1。在 64 个具有相同栅极长度的设备中,75% 表现为增强型特性。 对源漏区的金刚石材料进行掺杂,可以优化其与金属电极的接 触,实 现低欧姆接触电阻。Zhu等[94]报道了一种高漏极电流密度的增强型 H 终端金刚石 MOSFET,在多晶金刚石衬底上沉积了大量掺硼层作为源漏区,以栅极宽度归一化计算的最大电流密度为-400mA⋅mm-1。进一步研究发现,掺杂 B 的源和漏极可以提供高浓度的空穴,提高了由H 终端引起的表面 p 型通道电输运特性[93]。

此外,部分研究者借鉴传统 MOSFET 器件的结构,制备出了导通电流更高的 H 终端金刚石器件。Tsunoda 等[95]研究了一种具有沟槽栅结构的低导通电阻的(001)垂直型 H 终端金刚石 FET(见图 8(b))。研究发现:在引入沟槽栅结构后,器件的有源面积减小,显著提高了 FET 器件的集成度,并获得了更大的导通电流。在 VDS=-50V 和 VGS=-20V 时,最大漏极电流密度超过 20kA⋅cm-2,这是目前(001)晶面垂直型金刚石 MOSFET 的最高值。之后,该组又制备出了 U 型槽的垂直型 H 终端金刚石器件,获得了垂直型器件的最高击穿电压 580V[96]。然而,具有沟槽垂直型 FET 器件会集聚电场,大幅降低了器件的击穿电压,限制了 H 终端金刚石垂直型器件的发展。

3 总结与展望

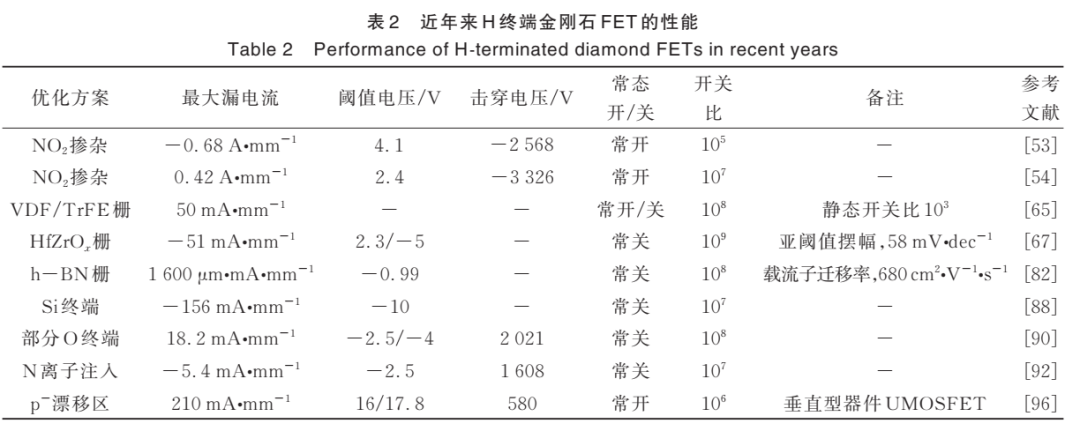

本文介绍了H 终端金刚石转移掺杂物的发展,综述了当前 2DHG 的产生机理。为了进一步提高表面终端金刚石 FET 的载流子浓度、迁移率、击穿电压,获得性能优良的增强型 FET,需要从栅层材料选择、表面终端、结构和掺杂等技术手段着手优 化,总结了近年来不同优化方案下 H 终端 FET 器件的性能(见表 2)。本文总结了当前优化方案的主要出发点和问题。

栅层材料可以极大地影响2DHG 的导电特性。选择常规的氧化物绝缘体作为栅层,其载流子散射较为严重,且无法获得增强型特性;选择非常规栅层时,高击穿电压、优良的导电特性和增强型 FET 往往不可兼得。这可能是由于界面处的电荷转移较容易,往往其载流子散射严重或难以承受较高的电压,而界面处电荷转移困难,则会导致载流子浓度较低,阈值电压较高,FET 开关性能差。需要更加深入地了解 H 终端金刚石的 2DHG 导电机制,寻找栅层材料,以获得更好的界面状态。 从表面终端处理、结构和掺杂等方式可以特定解决部分问题。通过表面终端处理,有望优化 FET的击穿电压并获得增强型特性。

FET 结构的改变可以大幅优化其导电特性,而掺杂有望优化电极与金刚石的接触并获得增强型特性。 当前,H 终端金刚石 FET 已经有了长足的发展,各种优化技术相结合,可以进一步提升其导电特性和击穿电压,而金刚石本身具有优良的导热率,可以一定程度上缓解功耗散热的问题,这使得其在高温、高功率和高频的电子器件领域必有一席之地。H 终端金刚石与铁电材料等其他功能材料结合,在光学传感、非易失性存储等领域也有望得到应用。 然而,金刚石无法 n 型掺杂,极大地限制着金刚石 FET 器件击穿电压的提升,无法发挥金刚石本身的优良性能,无法制备常规的 MOSFET、IGBT 等器件,难以与 SiC 等半导体材料竞争。此外,金刚石器件的大规模应用仍受限于大尺寸、高质量的金刚石晶圆制备,有待进一步解决。

审核编辑:刘清

-

功率场效应晶体管(MOSFET)原理2012-08-20 0

-

如何判断场效应晶体管方向,学会这几步轻松搞定2019-03-29 0

-

MOS管与场效应晶体管背后的联系,看完后就全明白了2019-04-15 0

-

场效应晶体管在威廉希尔官方网站 中的特别应用,你未必全都清楚2019-04-16 0

-

场效应晶体管的分类及作用2019-05-08 0

-

场效应晶体管的选用经验分享2021-05-13 0

-

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?2023-02-24 0

-

场效应晶体管的分类及使用2010-01-13 783

-

什么是场效应晶体管2009-05-24 7087

-

结型场效应晶体管是什么?2010-03-04 3797

-

场效应晶体管放大器2010-04-16 5251

-

功率场效应晶体管的工作特性2019-10-11 11274

-

如何进行场效应晶体管的分类和使用2020-07-02 1490

-

场效应晶体管的分类说明2020-09-18 8843

-

场效应晶体管的作用2023-05-16 2495

全部0条评论

快来发表一下你的评论吧 !