如何通过高性能CPU和FPGA可重编程的SoC架构应对5G挑战

移动通信

描述

1.引言

我们目前处于蜂窝连接的转型时期,未来无处不在的无线连接正在兴起。在全球范围内,2G、3G和4G的成功推动手机使用量达到了令人难以置信的75亿部。令人震惊的是,这使得移动设备的数量比全球人口还要多。或许更具影响力的是,蜂窝连接对那些之前被数字化剥夺权利的人产生的影响; 例如,2016年撒哈拉以南非洲地区每100人通常有1部固定电话,但有74台移动连接设备。

展望未来十年,随着5G的出现,无线基础设施将变得更加普遍,甚至与我们日常生活的方方面面完全融为一体。 5G延续了先前蜂窝标准(在驱动带宽方面)的模式,但也将其扩展到更多设备和使用模式。

主要趋势包括:

1.对增强型移动宽带(eMBB)和其他应用的带宽增加需求,特别是以10倍现有吞吐量或者更高速率驱动的瞬时可用带宽。

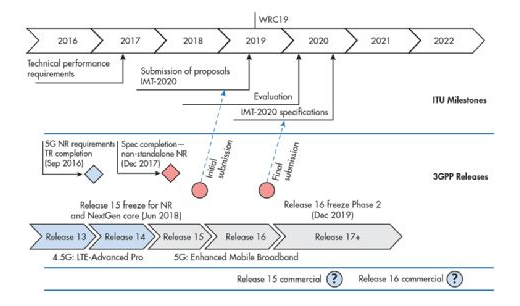

a. 这将是5G标准化带来的首波驱动力,其中3GPP已于2017年完成非独立(即LTE辅助)新无线电(NR),2018年可提供5G独立版,如图1所示。

b. 5G的部署也将根据频段情况分阶段进行,首先部署6GHz以下,然后是毫米波(mmWave)频率的连续频段,以便在稍后阶段支持关键eMBB应用。

图1:5G的ITU和3GPP时间表

2.随着物联网(IoT)蜂窝网络连接的到来而连接到大量的设备。预计到2020年将有500亿台蜂窝网络连接的设备。这些需求当中的一部分可以通过现有标准满足,同时也要靠Release 16版本中海量机器类通信(mMTC)的现有规范去实现了。

3. 新的应用模式也在不断涌现,这对移动设备及其蜂窝无线基础设施提出了新的要求。示例包括:

a.用于连接多个电池供电物联网端点的低带宽、低功耗的要求,以实现mMTC相关的连接和监控;

b.用于车辆到车辆和车辆到基础设施的连接(C-V2X)高可靠性、低延迟蜂窝网络,以补充现有的V2X解决方案

c.为远程手术和增强/虚拟现实等新兴应用提供的高可靠性、低延迟支持

后两类应用将通过即将推出的3GPP超可靠、低延迟连接(URLLC)标准来解决。

4. 对边缘分析和移动边缘计算(MEC)的新需求。计算重心正在从以前估计的将数据发送到集中式计算资源进行处理,转变为移到位于数据生成原点附近的分布式计算资源的新范例。造成这种转变的原因是多方面的:新兴应用严格的延迟要求、越来越庞大的数据量,以及优化稀缺网络资源的愿望等等许多方面。

2.基带

在本文中,我们考虑如何通过具有高性能CPU子系统和包括FPGA可重编程加速硬件处理单元的SoC架构来成功应对5G的独特需求。

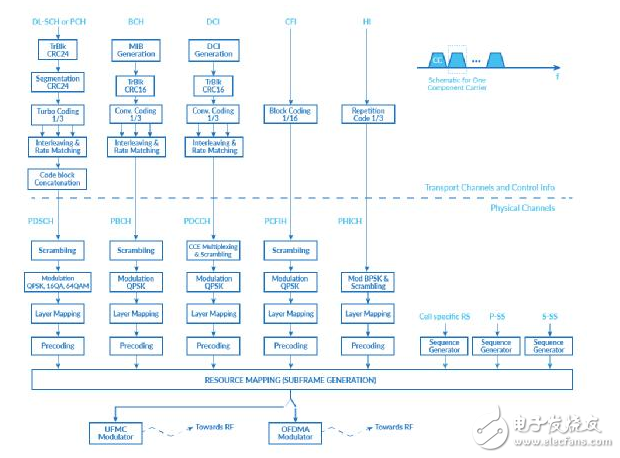

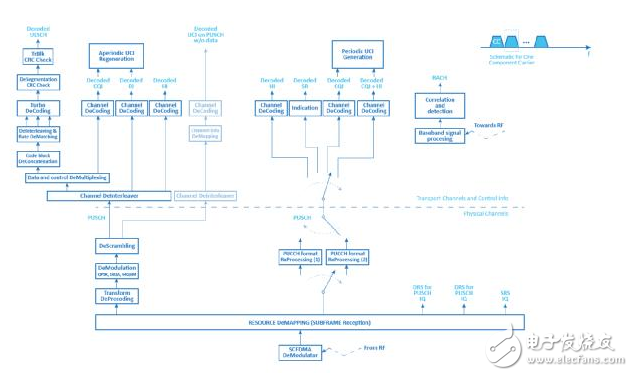

基带从网络接口(例如以太网)获取数据,并将其转换为通过前传(Fronthaul)接口传输到射频前端进行传入/传出的复杂样本。以下高级原理图包括用于LTE下行链路的发送器(图2a),以及用于上行链路的接收器(图2b)。

(a)下行链路

(b)上行链路

图2:基带处理的高级原理图

3.基带L1处理的案例研究

在这里,我们举例说明如何将基带处理(尤其是Layer-1层)映射到关键处理元器件上,如处理器子系统、CPU和DSP内核,以及固定和灵活的硬件加速,如图3所示。

图3:关键基带处理元器件

3.1. 前传(天线接口)连接

除了前面描述的处理元器件之外,还有一个灵活的天线接口功能模块:这是连接基带和射频单元所需的元件。传统上,这是通用公共无线电接口(CPRI),有时是开放式基站架构计划(OBSAI)兼容的部分。

然而,越来越多的方案在转向指定一个更灵活的前传接口,以允许基带和RF前端之间的不同映射(如图4所示)。IEEE对下一代前传接口NGFI(IEEE1914)进行了持续的跟进,包括用于基于分组的前传传输网络标准IEEE1914.1和以太网无线电(RoE)包封和映射标准IEEE1914.1。同时,还有其他行业项目指定了5G前传接口并可共享,例如eCPRI。

鉴于前传接口面临的各种规范、标准和要求,FPGA很适合其应用,并通常用于支持此接口,如图3所示。

3.2. 可加速5G上市时间的分立结构

图4将5G所需的处理元器件映射为具有独立器件的分立式架构,包括CPU SoC、辅助FPGA加速和天线接口。此配置反映了在可以提供经过优化的5G专用集成威廉希尔官方网站 ( ASIC)之前,可以在5G原型设计和早期量产中部署的实施方案。

·CPU系统级芯片里面包括:Arm处理器组合以及用于Layer-1处理和硬化加速器的DSP内核,用于固定的、明确定义的功能。

- 在此示例中,假设现有的4G ASIC SoC可用,因此具有通用加速(例如MACSEC)以及LTE特定加速:前向纠错(特别是turbo编解码器)、快速傅立叶变换和离散傅里叶变换,以在上行链路上支持SC-FDMA。

·灵活的天线接口

- 如前所述,前传天线接口非常适合用FPGA来实现。这是在线配置的,数据从射频单元发出(在上行链路上),然后是被转换为诸如以太网等具有标准连接的协议。

·硬件加速FPGA

- 辅助加速FPGA实现了在基带SoC上不可提供的所有必要的计算密集型功能。这可以是5G特定的功能或先前未曾规划的功能。

- 在此处显示的示例中,使用了CCIX互连。该标准允许基于不同指令集架构的处理器将缓存一致性、对等处理的优势扩展到包括FPGA和定制ASIC在内的多种加速器件上。

图4:可加速5G上市时间的分立结构

3.3. 基于Chiplet的5G实现

图5显示了与图4所示类似的架构,但是使用了基于系统级封装芯片(chiplet)的方法进行了重新配置。 在这种情况下,一个采用了更高带宽、更低延迟和更低功耗的接口将CPU SoC片芯晶粒与辅助硬件加速chiplet芯片连接起来。 支持前传连接到射频单元的FPGA器件在该示例中可以但并不是封装集成在其中的;但实际上,如果有足够的资源,它可以是与硬件加速chiplet芯片相同的chiplet器件。

图5:基于Chiplet的方法可实现更高的集成度

用于封装集成的两种主要技术是使用硅中介层或有机基板,以及某种形式的超短距离(USR)收发器。

3.4.完全集成的5G实现方式

最后,图6展示了本文考虑的最终、最高集成度的基带架构。该方法包括与先前相同的处理元件,具有相同的功能,但嵌入式FPGA(eFPGA)集成在了芯片内。

图6:采用单片集成的、应用于5G基带的异构多核系统级芯片

这种紧密集成的单片集成方法具有许多优点。与基于chiplet的方法相比,该接口具有更高的带宽、更低的延迟和更低的每比特能耗。此外,资源组合可以根据所考虑的特定应用进行定制,因此避免了不需要的接口、存储器和核心逻辑单元。这样可以实现以上所考虑的三种架构中最低单位成本。

如前所述,现在的主要目标是提供更快的上市时间、更高灵活性和未来可用性。之所以能加快了上市时间,是因为SoC可以提前流片,因为可以针对eFPGA进行后期修改(例如5G标准中Polar码的出现)而不是完成即固定的ASIC。来自新算法或者未预计算法(例如新的加密标准)的灵活性可以通过嵌入式可编程逻辑而不是软件或外部FPGA来解决。最后,未来可用性可以延长SoC的生命周期,因为诸如URLLC和mMTC等新标准等大批量新兴需求可以通过现有产品解决,而不需要进行新的开发。

总结

CPU和可编程加速(嵌入式或独立FPGA)的紧密耦合,使开发人员能够去创建可以一个应用于多个不同市场的平台产品。 这增加了特定产品的市场适用性并提高了开发投资回报。 这甚至可以在流片后再对市场进行定位(或重新定位),即最大化的可编程性所提供的内在灵活性可支持相当大的创新空间。

或许从5G的角度来看更为重要的是,高度可编程的解决方案可以加快产品上市速度。例如,在标准最终确定之前,不再需要推迟SoC的流片时间,后续改变的需求可以在软件或可编程硬件中实现。这对于早期5G部署所面临并在不断增加的压力,以及应对新标准的不断涌现,这是一个突出优势。

文章作者:Achronix半导体公司高级产品营销经理,Alok Sanghavi

-

5G时代的挑战,毫米波解决方案的测试和验证设计2018-07-23 0

-

5G无线技术创新:相控阵天线设计2018-12-06 0

-

在5G背景下,如何从容应对无线测试技术所带来的挑战?2019-04-22 0

-

欧盟5GPPP 5G架构白皮书概要介绍2019-07-11 0

-

5G无线机遇与挑战并存2019-08-02 0

-

怎么面对5G波形的测试挑战?2019-08-09 0

-

高性能LTC5593双无源下变频混频器2019-09-19 0

-

应该如何选择合适的电源为5G基站组件供电?2020-11-23 0

-

运营商应对5G网络测试的挑战盘点2021-01-11 0

-

5G 器件的设计与开发: 5G 性能范围2022-04-10 0

-

5G网络架构,5G中的SDR和SDN是什么?2023-05-05 0

-

5G:云网络的产业基础集成架构2023-08-04 0

-

高性能双无源混频器挑战5G MIMO接收机2021-04-21 635

-

紫光展锐发布系统级安全的高性能5G SoC移动平台T8202022-11-30 1379

-

Arm架构在5G商用中的优势与挑战2023-12-04 524

全部0条评论

快来发表一下你的评论吧 !