完整的ARINC429 协议和422协议的FPGA 硬件调试简介并完成多路机载总线收发器设计与实现

军用/航空电子

描述

摘要:本文以workbench 为平台,vxworks 为操作系统,chipscope 为分析工具,介绍了完整的ARINC429 协议和422协议的FPGA 硬件调试,通过硬件调试发现modelsim 仿真所不能发现的问题并分析问题解决问题,从而完成多路机载总线收发器的设计与实现。

在航空电子综合化系统中,快速、有效的数据传输对整个航空电子系统的性能有很大的影响,因此数据总线被称为现代航空电子系统的骨架,利用FPGA 技术设计集成多路ARINC429[1] 和422[4] 通道的通信芯片,可以有效的提高数据通信模块的处理能力和集成度,降低成本,本文以verilog 语言为基础, 通过ISE 编程,modelsim 仿真, 仿真无误后综合实现,用impact 将bit 文件烧写到FPGA 中,进行硬件调试,并用chipscope 进行分析,为了更加方便的进行调试,以workbench 为平台建立驱动。关于429 协议和422 协议已经非常成熟,因此本文主要从硬件调试的角度介绍多路机载总线收发器的实现。

1 FPGA 逻辑设计原理

很多情况下,我们需要一块板子既具有429[2-3] 功能又具有422 数据传输功能,因此我们将429 逻辑和422 逻辑[6] 建立在一个模块下,分别给429 逻辑和422 逻辑分配不同的地址空间,通过不同的地址空间控制429 和422 协议的片选信号,同时LOCALBUS 数据是双向数据,429 和422 数据是单向数据,因此需要加一个双向缓冲器,实现单向数据和双向数据之间的转换。协议部分已经非常成熟,在此不做赘述。

2 原型验证板验证

2.1 原型验证板原理

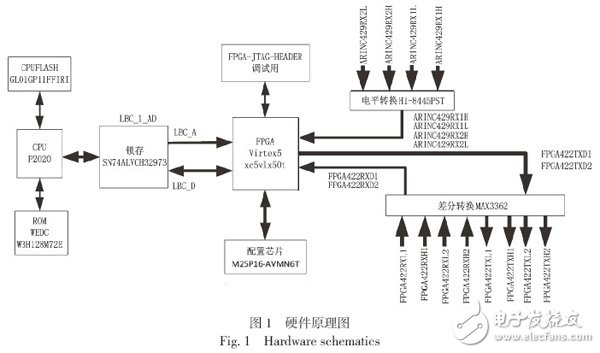

我们所用的威廉希尔官方网站

板名称为:MFD-GPM1018。设计原理如图1:CPU 控制FPGA 数据的写入和读出,FPGA 通过429 或者422 接收到的数据按照相应的协议转换之后由cpu 读出,cpu 通过Localbus 提供FPGA 要发送的数据并配置寄存器。

CPU 读出来的数据通过LBC-1-AD00——07 到锁存器把地址和数据按一定的控制规则转换为单独的地址信号和数据信号。LBC-1-AD00——07 表示某时刻是地址信号某时刻是数据信号。ROM 存储cpu 运行过程中的中间数据程。H1-8445 电平转换,将429 数据电平由bus 总线所要求的电平转

换为FPGA 需要的3.3V。ASP105885-01 是连接器将429、422 数据连接到GPM 调试版上,进行硬件调试。MAX3362 将串行数据转换为差分的形式。M25P16-AVMN6T 是FPGA 的配置芯片,通过JTAG 接口将bit 文件加载到FPGA 中这样配置之后,下次上电之后就可以直接将bit 文件load 到FPGA 中而不需重新加载。

2.2 硬件调试过程

在Workbench 开发平台vxworks[3] 操作系统下,首先连接串口网口从调试板到PC 机,新建超级终端,选择通信速率为115200,其他都为默认值,网口下载操作系统到cpu 中,串口用来控制cpu,串口网口连接好后,连接JTAG 接口,(JTAG连接线连USB 下载线连到PC 机),电源电压设置为28V,然后上电,通过调试板上的电压转换器转换为5V 供FPGA 板子使用,上电之后通过IMPACT 下载.bit 文件到FPGA 中,这种配置类型断电即丢失,下次上电后需要重新下载,同时打开超级终端,建立串口连接,此时vxworks 操作系统将会自动启动,在此操作系统下输入一些命令控制cpu,常用的就是读(d)和写(m)命令,并且打开chipscope,来进行调试。

为了充分验证逻辑功能的正确性:我们分别进行内回环测试,也就是在逻辑内部实现自收自发,然后进行外回环测试,将板子上发送接口与接收接口连接起来,实现回环收发,测试都无误后进行外部测试,对429 协议采用429 的仿真卡进行测试,对422 协议采用串口调试工具进行测试。

2.2.1 429 测试

429 的仿真卡发送429 差分数据,通过FPGA 接收,判断接收到的数据是否是发送的数据,以此来检测接收逻辑的正确性。

429 仿真卡BUStools /ARINC v3.20 仿真验证:

1)TX setup : 设置发送通道,波特率、奇偶校验

2)DEFINE :ADD new message 添加发送通道,我们需要TXD1、TXD2,设置发送数据参数:data——BIN 设置32—9位数据,前8 位数据通过Label 设置,Label 是一个233 数据类型,2 指的是2 位,比如设置为256,则为10101110, 映射到发送的数据为0111 0101,即为0x75,最高位为奇偶校验位,在发送过程中自动产生。

3) 设置完成后,点击run,停止发送的话点击stop。

通过超级终端读出接收到的数据与发送的数据一致,测试正确。

2.2.2 通过串口调试工具进行422 测试

422 的发送端口和接收端口通过232 连到PC 机上,PC机通过串口调试工具发送一串数据,经过232 转422 接收这些数据,接收到的数据在超级终端中打印,检测接收是否正确,类似的,调用驱动422 发送一串数据,通过232 到PC 机通过串口调试工具看到发送出来的数据,检测发送的数据是否正确。调试过程中比较关键的一点就是发送和接收端口波特率要设置一致。

如图2 所示,波特率设置为115 200,奇校验,数据位8 位,停止位1 位,422 发送数据,发送出来的数据经232 显示到PC 机串口接收窗口中,如下图接收框显示数据。

如图2 所示,通过串口调试工具,手动发送数据1、2、3、4、5、6、7、8、9、10,经232 转422 转换为422 数据形式,再经fpga 处理。则在超级终端上显示出接收到的422 数据个数以及数据。

2.2.3 驱动程序

驱动相当于用户与底层FPGA 逻辑的一个接口,里面包含一些初始化函数、发送函数、接收函数,初始化包括配置寄存器,波特率配置,通道选择,奇偶校验设置等,最后根据需求直接写一个测试函数,那么在硬件测试时先通过workbench[5] 进行调试,调试无误后,通过wftp 下载到cpu 中,然后通过超级终端直接调用测试函数即可,就不需要之前手动单步通过写、读操作来进行配置和测试了。

429 与422 通过检测状态位来控制发送接收的驱动测试流程如图3 所示。在上述测试过程中,发送一个数据则接收一个数据,仅仅检测到了接收与发送功能上的正确性。考虑到在应用过程中,并非发送一个数据接收完再发送一个数据,比如发送若干个数据之后,此时才开始进行接收,那么在这种情况下,接收fifo 缓存中将存在若干个数据,因此引入fifo的data_count 计数,表示此时缓冲中储存有多少个数据,然后依次把这些数据给读出来,这种情况下,也存在溢出的可能性,因此引出溢出状态位。

改进后引入fifo 计数和溢出状态检测的驱动测试流程如图4 所示。

3 调试过程中遇到的关键问题及分析

调用驱动对422 进行外回环测试0 通道发0 通道收1 通道发1 通道收,这时出现问题:当发送多个数据接收多个数据,或者多次测试时会出现接收数据错误或者未接收到数据的现象,但是通过超级终端单步测试确是是正确的。用chipscope[7] 抓信号,发现接收数据时,会出现接收完数据后,fifo 非空的状态,正常应是空状态,这样就把之前的数据再次接收了一遍,抓到的错误如图5,其中test 是我们为了测试方便加的一个参数用来检测DAT 变化,因为DAT 是双向数据无法抓到。

分析原因是由于发送的数据被接收后,再次发送数据前检测状态位未来得及告便,导致错误,于是在检测状态位后面加延迟taskdelay(1),测试正确,但是与之而来的问题是这样大大影响了波特率,因为1 代表1/60ms,而波特率是ns 级的,于是用一个读寄存器操作来代替这个延迟,读一个寄存器状态需要的时间大约为us 级,具有一定的延时但性能又优于taskdelay,并且读寄存器也不会影响其他的正常功能,至此以为问题解决了。但是后来为了完善功能,在逻辑中添加count,修改驱动进行测试,发现打印到超级终端上的fifo 计数不正确,发送一个数计数却是31,继续发送一个逐个计数为61,91…. 用chipscope 抓信号发现在tf_push 有效时(tf_push 控制发送fifo 的写信号),同一数据输入到fifo 了31 次,根据逻辑tf_push 在写信号有效以及地址是发送缓冲地址且此时是正常工作状态时就有效,那么根据chipscope 抓到的,发现在一个地址有效,写信号有效的周期内,tf_push 持续有效,持续计数就说明此时有效了多个时钟周期,每个时钟周期数据写入到发送fifo 中一次,但是我们期望的是写信号有效地址有效一个周期内,数据只写入一次,因此我们修改逻辑,使tf_push 有效的周期缩短为一个时钟周期,同时根据这个问题,也判断了之前接收数据总出错,出现一个数据接收两次的现象,需要加适当的延时才不会出错的原因正是如此。 明白这些之后,我们又把驱动中检测状态位与接收之间的延时去掉,再次测试,这次果如预期的一样不再出错,至此才找到了根本原因。对于这个问题Modelsim 是发现不了的,因为Modelsim 仿真时输入激励比如写信号wr_n 有效设置的就是一个时钟周期,因此chipscope 能够发现modelsim 发现不了的

问题,这也就是硬件调试的功效。

修改前tf_push 如图6所示。

修改后的tf_push,持续一个时钟周期,如图7 所示。

针对这个问题,我们总结写底层逻辑时控制读信号和写信号使其持续时间为一个时钟周期是非常有必要的,可以有效避免数据重复读入和写出。

4 结束语

文中以FPGA 为基础,主要介绍了多路422 协议429 协议总线完整的FPGA 硬件调试,涉及硬件原理 、调试过程、调试中用到的工具、驱动程序以及对调试过程中遇到问题的分析方法,经过这一系列的调试无误,此部分将可以接受检验,实现稳定的数据通讯功能。最后将逻辑固话到FPGA 中,上电自启动,自此我们完成了完善的多路机载总线收发器的设计和实现。

-

基于USB的ARINC429总线接口模块设计2008-10-14 0

-

[原创]MIL-STD-1553B ARINC429 CAN等总线协议2010-05-04 0

-

基于PC/104设计与实现ARINC429接口模块2019-04-16 0

-

采用专用接口威廉希尔官方网站 PCI9054实现ARINC429总线接口板设计2019-04-26 0

-

基于AEC429-PCI-22/S5总线接口卡的ARINC429总线数据的仿真发送与采集系统2019-05-29 0

-

多通道ARINC429总线数据接收和发送的实现2019-06-13 0

-

怎么设计便携式ARINC429总线通信设备?2019-08-19 0

-

怎样去设计ARINC429总线接口板?有哪些步骤?2021-05-27 0

-

航空用ARINC429总线收发系统设计与实现2009-07-16 862

-

USB的便携式ARINC429总线通信设备技术2010-05-06 2587

-

什么是ARINC429总线?2011-04-19 12680

-

PCI总线ARINC429通信卡实现方法2011-05-18 782

-

一种PCI总线ARINC429通信卡实现方法2011-09-30 1052

-

实例分析1553B和ARINC429总线实时协议转换系统2017-10-27 3161

-

如何使用FPGA实现ARINC429接口和总线数据接收2021-02-03 1663

全部0条评论

快来发表一下你的评论吧 !