基于TMS320VC5402芯片和ADuC841转换器实现数据采集处理系统的设计

测量仪表

描述

1、引言

当前,越来越多的设计应用领域要求具有高精度的A/D转换和实时处理功能。在实时数据采集处理系统设计中,一般需要考虑数据采集以及对采集数据的处理。而对于大数据量的实时数据采集处理系统来说,保持数据高速传输也是该系统性能的关键因素。

采用TMS320VC5402和转换器ADuC841构成双CPU处理器平台,充分利用TMS320VC5402的对大容量数据和复杂算法的处理能力,ADuC841接口的控制能力以及各自拥有的DMA控制器构建实时数据采集处理系统。双CPU通过DMA方式实现数据交换,将数据传输和系统控制分开,提高了数据传输速度,降低了处理器负担,提高系统运行效率。采用此解决方案。大大提高了系统的信号采集和处理能力。

2、系统硬件设计

2.1 ADuC841简介

ADuC841是ADI公司ADuC84X系列中性能最完善的一款微转换器,它具有单周期指令,20 MI/s的8052内核;内置一个8通道、高速420 Ks/s、高精度自校正、12位逐次逼近的ADC,具有DMA控制:2通道12位DAC;2通道PWM方式∑-△型DAC;片上15 ppm/℃高稳定电压基准;片上温度传感器;62 KB片内Flash/EE程序存储器;4 KB的片内Flash/EE数据存储器。还包括看门狗定时器和电源监控器、ADC与数据存储器之间的DMA方式、存储保护功能、通用异步串行收发器(UART)、SPI和I2C总线接口等功能模块。

ADuC841片内的ADC的转换速率为2.38μs/次(420 kHz的采样率)。当A/D转换时,ADuC841必须在2μs内读取A/D转换结果并将其传输且存储到外部存储器中以便后续处理,否则将导致下一个转换结果出现后丢失前一个转换结果。由于中断服务子程序中存储转换结果和微转换器跳转到ADC的中断服务子程序都需要时间,因此很多应用无法响应高的中断速率。采用ADC的DMA方式传输数据能够解决上述问题,通过设置特殊功能寄存器ADCCON2中的中断响应位即可使能ADC的DMA方式。这种方式下,无需CPU的软件中断响应干预,可通过硬件直接检测相应控制位就能将ADC的转换结果直接输出并存储到片外的静态RAM中,并提供了一个高速数据传输通道,从而保证了ADC能以最高速率(420 kHz)完成数据采样和转换,并进行高速信号传输。

2.2数字信号处理器TMS320VC5402简介

TMS320VC5402 是 TI 公 司 的TMS320C5000系列之一,它采用改进的哈佛结构,具有分离的程序总线和数据总线,采用4级流水线作业,其运行速度可达100 MI/S,具有高速运行的特点。同时提供丰富的指令集,增强的模块化结构设计,具有通用性,拓展了应用领域。TMS320VC5402可寻址3个独立的存储空间,包括1 MB×16的程序空间,64 KB×16的数据空间以及64 KB×16位的I/O端口空间。片内提供16 KB×16的双存取RAM和4 KB×16的ROM,并具有直接存储器访问(DMA)功能,通过HOLD允许对外部程序、数据以及I/O空间进行直接存储器访问。TMS320VC5402存储器直接存储控制DMA可在不占用CPU资源的情况下,实现DSP存储器间数据的自由传输。TMS320VC5402有6个可独立编程的DMA通道,每个DMA通道由各自的寄存器控制。

2.3系统的硬件结构

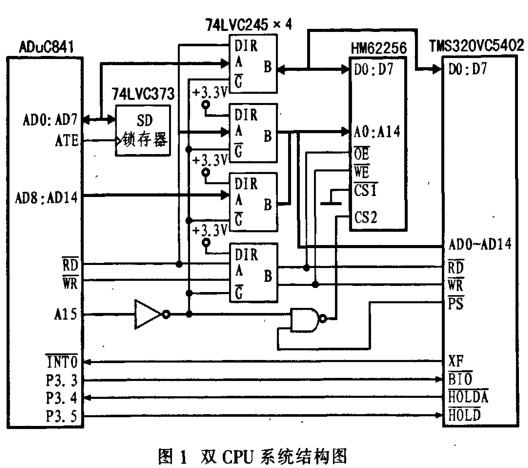

设计DMA共享存储器实现双机通讯需要考虑以下几点:(1)设计ADuC841和TMS320VC5402之间数据总线和地址总线的隔离威廉希尔官方网站 。隔离威廉希尔官方网站 在双CPU不通信时隔离地址总线和数据总线,而在DMA通信时则选通。(2)设计ADuC841和TMS320VC5402都能对存储器读写的选通信号和读写信号。(3)设计控制TMS320VC5402信号及其响应信号。

考虑上述问题,采用ADuC841与TMS320VC5402的双CPU系统结构如图1所示。存储器HM62256既是TMS320VC5402的全局数据存储器,又是ADuC841的外部存储器。A15为片选信号,地址范围为8000H~FFFFH。两个CPU分别通过总线和数据存储器HM62256相连,实现存储器共享。

隔离威廉希尔官方网站 采用4片74LVC245双向缓冲器实现,由于ADuC841的P0口是分时复用的地址/数据总线,所以需采用一片74LVC373地址锁存器将P0端口的地址信号从地址/数据总线中分离出来。而ADuC841的16位数据总线需要双向缓冲,由于ADuC841要对HM62256进行读写操作,所以缓冲器的方向由ADuC841的读信号RD控制,当ADuC841读数据时,RD为低电平,使数据缓冲方向为HM62256至ADuC841;写数据时,RD为高电平,数据缓冲方向为ADuC841至HM62256。缓冲器的使能线由A15反向信号控制,当A15为高电平时,选通缓冲器,否则缓冲器为高阻态。A15还是HM62256的片选信号,若要ADuC841和TMS320VC5402都能选通HM62256,需将A15和PS的与非信号作为HM62256的片选信号。ADuC841选通时,PS为高电平,ADuC841的A15有效。TMS320VC5402选通时,当A15为低电平时,PS有效。

ADuC841通过P3.5、P3.2(INT0)分别与TMS320VC5402的HOLD、XF引脚相连,P3.5向TMS320VC5402申请总线控制,TMS320 VC5402响应ADuC841的请求后,HOLDA信号变低,TMS320VC5402的CPU挂起,并出让外部总线。ADuC841通过A15打开总线驱动器,并经与非门后选中HM62256,获得HM62256的控制权,实现对HM62256的读写操作。而TMS320VC5402可通过XF向ADuC841请求中断,ADuC841在响应中断INT0后,通过P3.5将HOLD信号转换为高电平,此时总线控制权重新交给TMS320VC5402。

3、系统软件设计

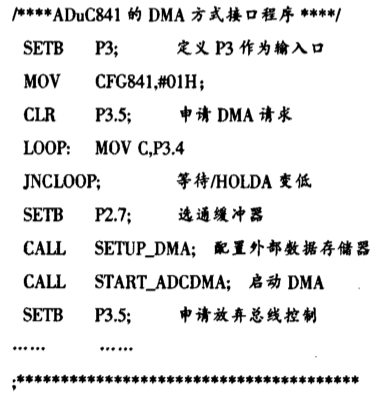

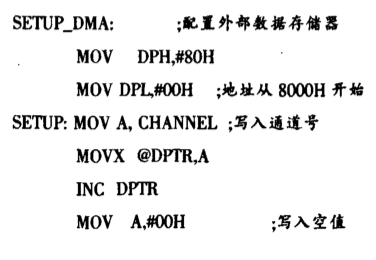

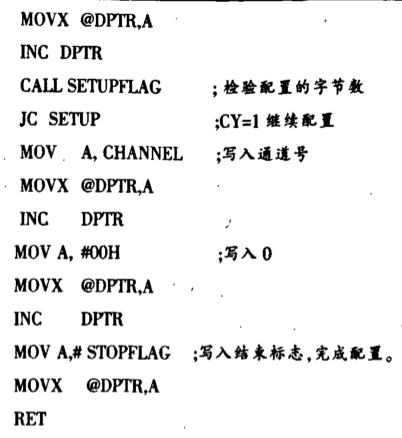

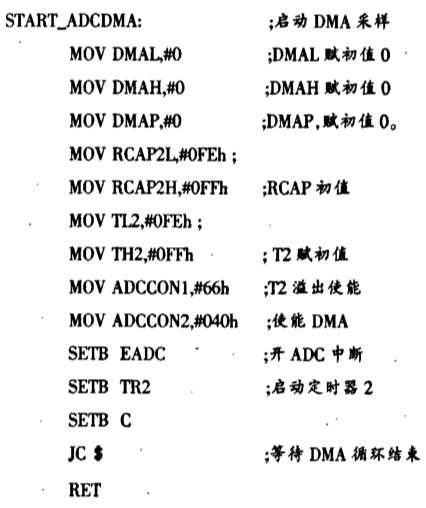

系统上电时,ADuC841由P3.5向DSP申请总线控制HM62256,设置DMA方式,通过配置3个特殊功能寄存器ADCCON1~ADCCON3,ADuC841的ADC工作在不同模式下。其中在DMA模式下,ADC可连续转换,并将采样值直接输出并存储到片外的HM62256中而无需来自CPU的任何软件干预,从而保证ADC能以最高速度(420 kHz)完成采样和转换并进行高速信号传输。A/D转换后,ADuC841通过ADC中断,P3.5发送高电平至TMS320VC5402的HOLD引脚,向TMS320VC5402申请放弃总线控制,HM62256的总线控制权重新交换给TMS320VC5402,由TMS320VC5402进行数据处理。当TMS320VC5402处理完数据后,首先将运算结果放回HM62256,然后通过XF信号线通知ADuC841,ADuC841响应后,向DSP申请总线控制接管HM62256,读出运算结果,然后进行下一步处理。以下是ADuC841的部分DMA接口程序代码:

4、 结束语

对于实时数据采集处理系统,选取合理有效的核心算法是至关重要的,然而,选择数据传输方法也是相当重要,在一些实际情况下,数据传输时间可能超过数据处理的时间。通过合理使用DMA高速数据传输是提高数据传输效率的一种途径,有助于产品的开发。

责任编辑:gt

-

HPI方式自举在TMS320VC5402 DSP芯片上的实现2009-08-20 0

-

MAX121/TMS320VC5402的高速数据采集接口设计2018-11-29 0

-

基于ADuC841的USB接口数据采集系统设计2018-12-12 0

-

怎样去设计TMS320VC5402与模拟芯片TLC320AD50C的接口?2021-04-23 0

-

基于TMS320VC5402的汽车防撞信号处理系统设计与实现2009-08-28 511

-

基于ADuC841和TMS320VC5402的实时数据采集处2010-12-14 885

-

基于ADuC841的数据采集及无线收发系统2010-12-29 870

-

MAX121与TMS320VC5402在高速数据采集中的接口2008-10-09 997

-

基于TMS320VC5402的超声检测高速采样系统2011-07-07 886

-

TMS320VC5402 DSP与串行AD73360 A/D转换器的接口设计2015-11-02 657

-

基于TMS320VC5402的DSP基本系统的设计2017-10-20 991

-

TMS320VC5402和TMS320UC5402引导加载程序的特点和操作详细概述2018-04-26 1252

-

TMS320VC5402 数字信号处理器2018-10-09 915

-

基于DSP芯片TMS320VC5402的PCI图像采集卡2018-10-08 1860

-

数字信号处理器TMS320VC5402与音频模拟芯片TLC320AD50C的接口设计2019-02-09 763

全部0条评论

快来发表一下你的评论吧 !