英特尔先进封装的玻璃基板技术解析

制造/封装

描述

美国芯片巨擘英特尔9月18日宣布推出业界首款用于下一代先进封装的玻璃基板,计划于2026 年至 2030 年量产,凭借单一封装纳入更多的晶体管,预计这将实现更强大的算力 (HashRate),持续推进摩尔定律极限,这也是英特尔从封装测试下手,迎战台积电的新策略。

英特尔赶在创新日 (9月19 日) 活动开跑前,抢先宣布推出业界首款用于下一代先进封装的玻璃基板方案。

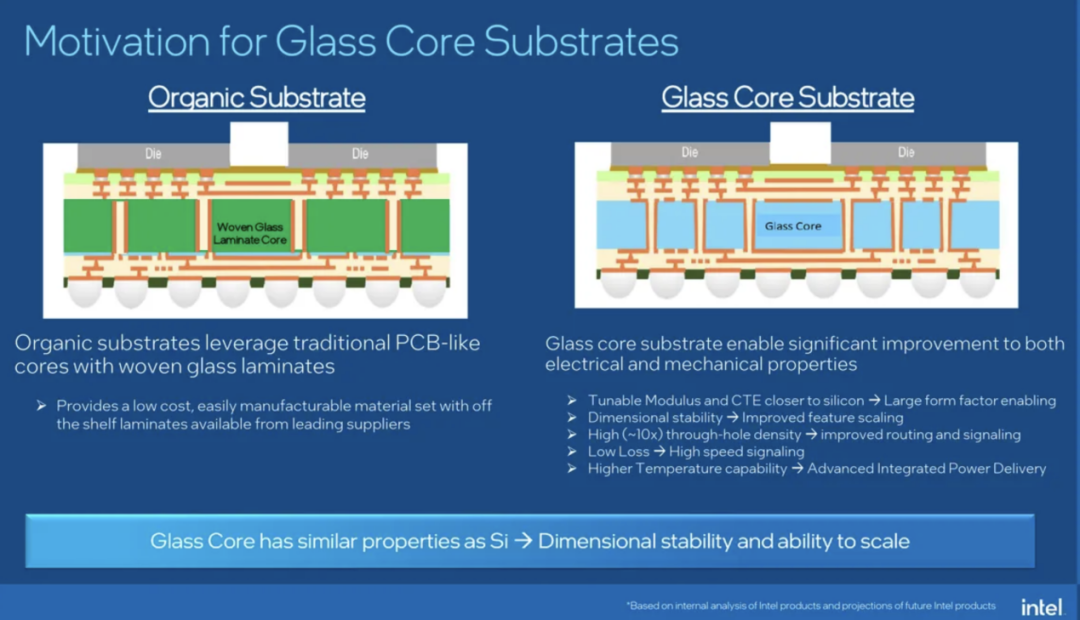

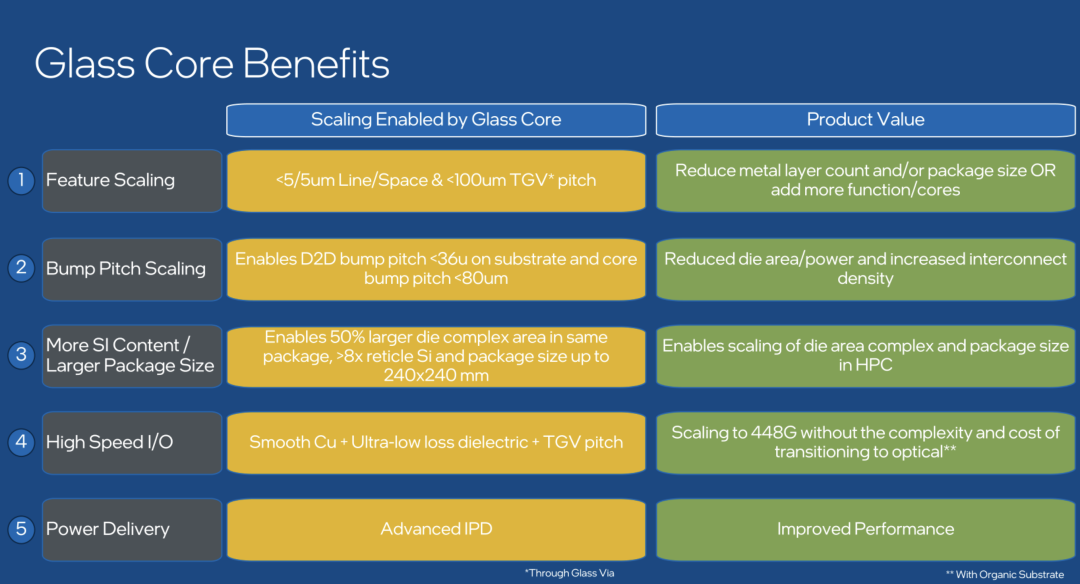

随着对更强大计算的需求增加,以及半导体行业进入在封装中使用多个“Chiplet”的异构时代,信号传输速度、功率传输、设计规则和封装基板稳定性的改进将至关重要。这就使得当前正在使用的有机基板面临巨大的挑战,而这也正是玻璃基板所具备的。

英特尔表示,玻璃基板具有卓越的机械、物理和光学特性,允许在封装中连接更多晶体管,从而提供更好的扩展性并能够组装更大的小芯片(Chiplet)复合体(称为“系统级封装”)。芯片架构师将能够在一个封装上以更小的占地面积封装更多的块(也称为小芯片),同时以更大的灵活性和更低的总体成本和功耗实现性能和密度增益。

换而言之,玻璃基板首先能为芯片提供结构稳定性(硅芯片非常脆弱),并且它们也是将来自硅芯片的信号传送到其他封装芯片(即小芯片)或芯片背面有大量相对较大的引脚/焊盘。而且,随着多年来芯片尺寸的增加,以及高端芯片所需的引脚/信号数量的增加,对用作基板的更新、更好的材料的需求也在增加,这正是推动英特尔发展的动力。英特尔高级副总裁兼组装与测试开发总经理Babak Sabi表示:“经过十年的研究,英特尔已经实现了行业领先的先进封装玻璃基板。我们期待提供这些尖端技术,使我们的主要参与者和代工客户在未来几十年受益。”

英特尔称,凭借这些功能,玻璃基板上的互连密度可以提高 10 倍,并允许实现高组装良率的超大型封装,预计在 2026 至 2030 年推出完整的玻璃基板解决方案。

英特尔提及,玻璃基板重大突破使封装技术能够持续扩展,在单一封装中容纳 1 兆个晶体管的目标,并将摩尔定律延续到 2030 年之后。

英特尔表示:「我们将首先在人工智能 (AI)、绘图处理和资料中心等高性能领域看到使用玻璃基板的芯片。」

英特尔此一突破性成就是英特尔也在为其美国芯片代工厂增强先进封装能力的另一个迹象,也是英特尔迎战台积电的新策略。

据报导,英特尔对手台积电 (TSM-US) 的亚利桑那州厂计划生产 4 纳米和 3 纳米芯片,但目前并无在亚利桑那州或美国境内打造封装厂的计划,主要卡关因素是成本高昂,因此这些先进芯片不会在美国完成封装。

英特尔先进封装资深经理 Mark Gardner 于今年 5 月份指出,英特尔芯片制造工厂和组装、测试、封装站点分布在世界各地,相较台积电目前大部分芯片制造设施都在中国台湾,英特尔优势在于提供安全供应链、分散地缘风险,也可提供客户部分 IDM 流程,弹性选择。

Gardner 称:「英特尔晶圆制造服务愿意让客户只使用服务的一部分,也就是说,他们可以委托其他晶圆代工业者生产芯片,英特尔只做封测。」

一、基板的变

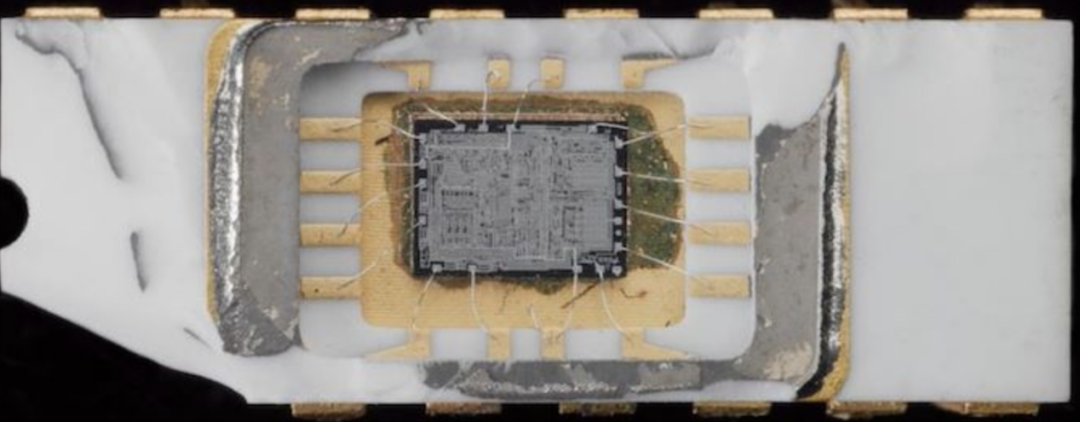

据anandtech介绍,芯片产业对基板的需求,最早可以追溯到大规模集成芯片的早期,当时的芯片设计达到了成千上万个晶体管。这些小型晶体管需要连接到更大的引脚,以便由相对庞大的人力安装到系统中,从而产生了第一个芯片封装,例如双列直插式封装。

在当时,它们使用框架(通常是引线框架)来固定实际的硅芯片,框架(或焊线)提供芯片和外部引脚之间的信号路径。

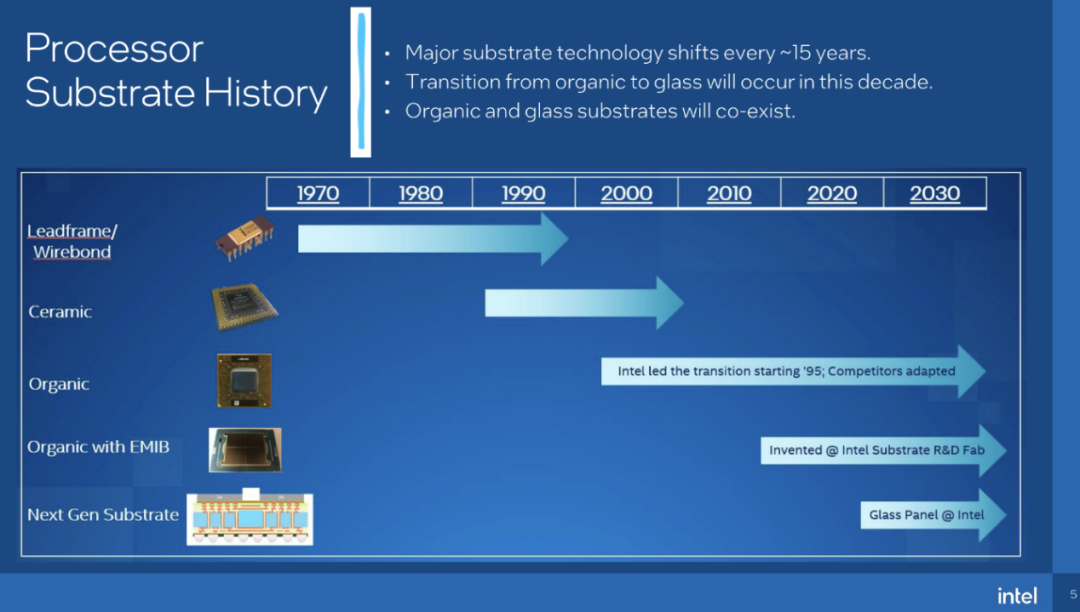

自 70 年代以来,基板设计发生了多次演变。金属框架在 90 年代被经典陶瓷芯片所取代,然后在世纪之交被有机封装所取代。最重要的是,每次迭代的基板都比上一次具有更好的性能,从而可以更轻松地将大量信号和电源引脚布线到日益复杂的芯片上。

虽然现在你仍会到处发现引线框架和陶瓷芯片,但有机基板在过去几十年中一直是该行业的支柱。

据了解,有机基板的材料主要由类似 PCB 的材料和编织玻璃层压板制成,允许通过芯片路由相当多的信号,包括基本的小芯片设计,例如英特尔的移动处理器(具有单独的 PCH 和 CPU 芯片)以及 AMD 基于小芯片的 Zen 处理器。

但有机基板已经成为限制因素一段时间了,尤其是在高端芯片中。英特尔认为,有机基板将在未来几年达到其能力的极限,因为该公司将生产面向数据中心的 SiP,具有数十个tiles,功耗可能高达数千瓦。此类 SiP 需要小芯片之间非常密集的互连,同时确保整个封装在生产过程中或使用过程中不会因热量而弯曲。

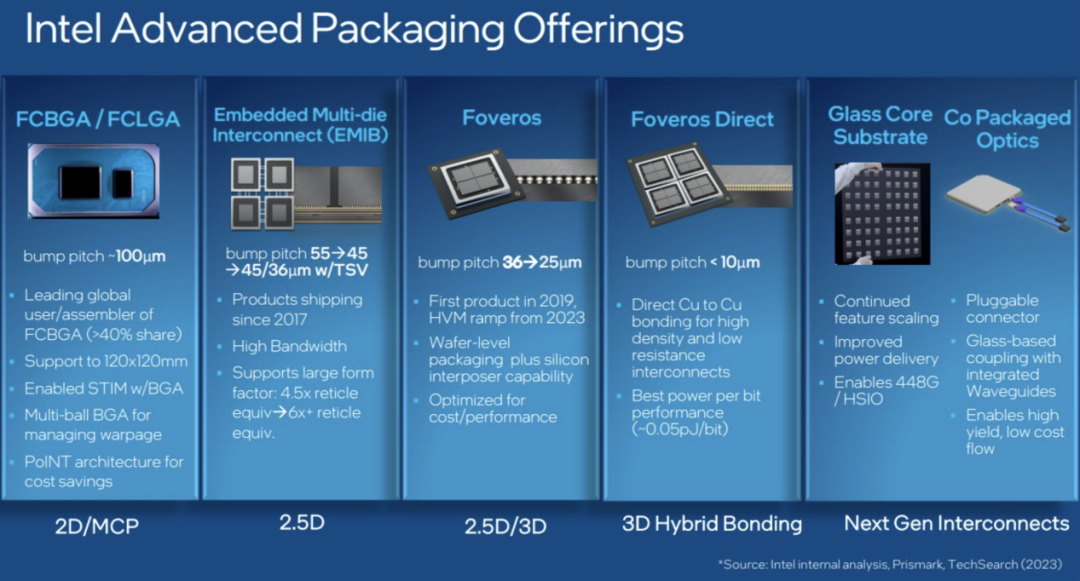

因此,英特尔也一直在寻找有机基板的真正替代品,一种能够与大型芯片完美配合的基板,这虽然不能在最高级别取代 CoWoS/EMIB 的需求,但可以提供比当前有机基板更好的信号性能和更密集的布线。

值得一提的是,英特尔在实现下一代封装方面拥有悠久的历史,在 20 世纪 90 年代,他们引领了行业从陶瓷封装向有机封装的转变,也是第一个实现卤素和无铅封装的公司,并且是先进嵌入式芯片的封装技术的发明者。

二、英特尔的玻璃基板革命

英特尔院士兼 Substrate TD 模块工程高级总监 Rahul Manepalli在一个视频中表示,与有机基板相比,玻璃芯基板在封装技术方面提供了实质性改进。与有机材料一样,玻璃还可以制造成各种尺寸。

按照Rahul 的说法,有机基材是一种复合材料,而玻璃是一种均质的非晶态材料。这就使得英特尔能够调整玻璃基板的特性,使其更接近硅的特性,从为许多性能和密度增强提供了机会。

根据英特尔的介绍,其玻璃芯基板的核心在于用玻璃取代有机封装中的有机、类似 PCB 的材料。换而言之,英特尔不会将芯片直接安装在纯玻璃上,而是把基板核心的材料替换成玻璃。同时,金属重新分布层(RDL)仍然存在于芯片的两侧,提供各种焊盘和焊点之间的实际路径。

英特尔称,为了弥合机械和电气之间的差距,他们还能够在玻璃通孔(TGV)上实现更紧密的间距,从而通过基板本身传输信号,从而允许整体上有更多数量的通孔。按照英特尔提供的数据,他们能够将 TGV 的间距控制在 100 微米 (μm) 以内,从而将 TGV 密度提高 10 倍。

所有这些最终使得通过基板核心路由信号变得更加灵活,并且在某种程度上使得使用更少的 RDL 层路由信号变得更加容易。

这就让实现更大的芯片变得容易,而且允许在相同尺寸的芯片上放置更多的芯片。

英特尔声称,玻璃封装将使他们能够在芯片上放置多 50% 的芯片,或者更确切地说,芯片内的芯片复杂区域可能会大 50%,从而实现比英特尔目前所能制造的更密集的芯片封装。

英特尔表示,玻璃基板可实现更高的互连密度(即更紧密的间距),从而使互连密度增加十倍成为可能,这对于下一代SiP的电力传输和信号路由至关重要。

特别是,英特尔正在谈论 <5/5um 线/间距和 <100um 玻璃通孔 (TGV) 间距,这使得基板上的芯片到芯片凸块间距 <36um,核心凸块间距 <80um。

此外,玻璃基板可将图案畸变减少 50%,从而提高光刻的焦深并确保半导体制造更加精密和准确。

来到电气性能方面,据英特尔透露,玻璃芯基板(更具体地说是 TGV)也能提供更好的表示,这是由于 TGV 中使用的电介质具有低损耗特性,而且数量大得多,因此玻璃芯基板将实现更清洁的信号路由和电力传输。对于前者,这意味着能够通过铜缆发送 448G 信号,而不必使用光纤互连。

与此同时,较低损耗的电力传输将减少在到达处理器芯片之前以热量形式损失的能量,从而进一步提高整体芯片效率。

不过,正如anandtech报道说,虽然玻璃芯基板比有机基板允许更紧密的信号间距,但它们并不能替代 EMIB、Foveros 或其他基于使用硅介质的更先进的封装技术。TGV 的 75μm 间距与 EMIB 的 45μm 间距仍然相去甚远,更不用说为 Foveros Direct 计划的 <10μm 间距了。

因此,所有这些封装技术仍将是玻璃芯基板的补充附加技术,最多可以在不需要 EMIB 全面密度改进的产品的边缘情况下取代 EMIB。

为了证明该技术的有效性,英特尔发布了一款全功能测试芯片,该芯片采用 75um TGV,长宽比为 20:1,核心厚度为 1 毫米。虽然测试芯片是客户端设备,但该技术最初将用于构建面向数据中心的处理器。但当技术变得更加成熟后,它将用于客户端计算应用程序。英特尔提到图形处理器是该技术的可能应用之一,由于 GPU 可以消耗任意数量的晶体管,因此它们很可能会受益于互连密度的增加和玻璃基板刚性的提高。

“玻璃基板最初将被引入需要更大外形封装(即数据中心、人工智能、图形)和更高速度功能的应用程序和工作负载的市场。”英特尔说。

编辑:黄飞

-

英特尔重新思考解决芯片短缺的常用基板2022-06-20 0

-

英特尔正在研发玻璃材质的芯片基板2023-06-30 1098

-

英特尔先进封装:彻底改变芯片封装技术2023-07-03 927

-

英特尔推出下一代先进封装用玻璃基板,业界提出质疑2023-09-19 1262

-

英特尔推出玻璃基板计划:重新定义芯片封装,推动摩尔定律进步2023-09-20 986

-

满足更高算力需求,英特尔率先推出用于下一代先进封装的玻璃基板2023-09-20 408

-

英特尔公布玻璃芯研发进展,玻璃基板或引领下一代先进封装2023-09-24 2754

-

下一代英特尔玻璃基板封装转型概述2023-10-08 1339

-

英特尔:玻璃基板将推动算力提升2023-12-06 442

-

玻璃基板对于下一代多芯片封装至关重要2023-12-07 901

-

英特尔加大玻璃基板技术布局力度2024-05-20 527

-

英特尔携手日企加码先进封装技术2024-06-11 413

-

英特尔引领未来封装革命:玻璃基板预计2026年实现量产2024-06-28 701

-

英特尔计划最快2026年量产玻璃基板2024-07-01 589

-

英特尔是如何实现玻璃基板的?2024-07-22 322

全部0条评论

快来发表一下你的评论吧 !