深入了解赛灵思System Generator中的时间参数

EDA/IC设计

描述

深入了解赛灵思System Generator中的时间参数

基于模型的设计(MBD)因其在缩小实时系统抽象的数学建模和物理实现之间差距方面的光明前景而备受关注。通过使用相同的源代码进行算法分析、架构探讨、行为模拟和硬/软件设计,MBD有望缩短系统设计周期。

无需通晓硬件描述语言(HDL),为DSP提供的Xilinx System Generator即可让控制工程师在熟悉的Simulink环境中设计系统,然后在FPGA中实施。为此,必须将受控系统(通常称之为设备)的数学模型参数值(如连续/离散时间传递函数或状态空间描述)与FPGA系统时钟频率和数字控制器的采样率关联起来。

FPGA中的数字控制器

之前,在实施FPGA时,控制器设计人员在首次验证控制策略和参数并进行控制器和设备模型的高级模拟(如使用Simulink)后,可能还会使用一种低级的HDL。HDL控制器设计与Simulink模拟之间的对应性将由HDL测试平台加以验证。为在闭环系统中验证控制器设计,该测试平台必须包括设备模型。对于缺乏HDL和FPGA技术专业背景的设计人员及大多数控制工程师而言,要实现上述这一切却并非易事。在这种情况下,如Xilinx System Generator之类的高级建模和设计环境正是理想之选。

System Generator中的PID控制器

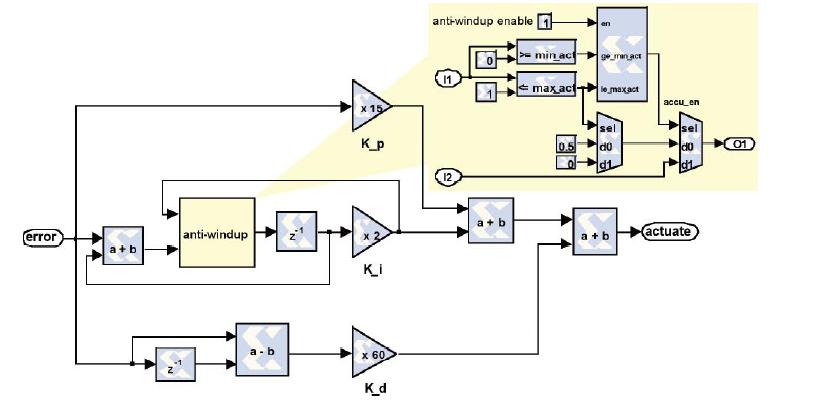

鉴于许多控制器仍基于传统的比例-积分-微分(PID)结构,借用一个PID控制器来演示本文的观点。同时,本文概述的方法也可较好地处理超前滞后补偿器、状态空间观测器或者自适应控制器等其他常用的控制组件。图1所示为采用源自赛灵思模块集的模块而设计的PID控制器。

图1 基于System Generator模块且支持抗饱和功能的PID控制器

这里没有使用赛灵思的累加器模块,而是采用基本的加法器和寄存器构建块来实现集成。这样做可以插入如图1所示的抗饱和逻辑,以便在控制器输出的积分部分达到执行器规定的饱和限值时,冻结累加器寄存器中的内容。抗饱和逻辑可使PID控制器成为非线性系统,并对系统的总体动态产生积极的影响。

图2所示的模块参数菜单可用来配置各种信号的控制参数和字宽。

图2 PID控制器的定制参数菜单

另外,设计人员还能在此启用或停用抗饱和函数。利用该菜单,无需修改低级HDL代码即可方便地进行实验。

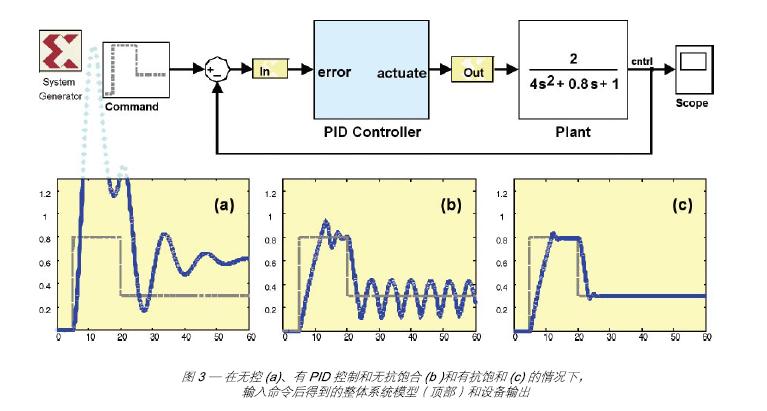

图3所示为整体系统模型,其不仅包含控制器,还有基于标准Simulink模块的设备和模拟测试平台。借助该模型,设计人员可采用连续或离散时间传递函数进行设备建模,而在HDL测试平台中则只能使用离散时间函数。值得一提的是,采用System Generator方法,就可以通过同一个高级模型完成从系统建模、模拟、验证直至实施的任何工作。

控制参数

第一个控制参数是模拟时间单位TSim。该参数无须在设计中明确地输入。该参数代表的是对 Simulink模拟中基础时间单位的隐含假设。因此,其仅对模拟有所影响。在Simulink以及System Generator环境中,模拟时间单位通常被假定为1s。例如,System Generator Wavescope模块的显示就使用这个惯例。不过正如在下面所见到的,TSim也可以满足需要的其它任何时间单位。

随后还需要在System Generator中以纳秒为单位设置FPGA时钟周期TCLK参数。该参数代表的是主系统时钟输入到FPGA的周期,而所有其它时钟和时钟启动均由此导出。因此,其设置只会影响硬件实施。例如,对于广受青睐的赛灵思Spartan-3E入门套件,FPGA时钟周期为20ns(50MHz)。

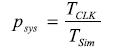

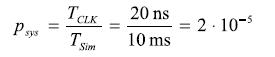

而Simulink系统周期Psys则代表着Simulink模拟和硬件实施之间的全局连接。设计人员必须设定这个参数,因为它在System Generator中影响Simulink模拟和硬件实施。在模拟过程中,该值决定了相对于模拟时间单位而言,对模型的System Generator模块调用、但却不必要地进行更新的频度。对于硬件实施,该参数规定了相对于控制器采样率的超频量。与System Generator的文档不同,将Simulink的系统周期定义为无单位量,即FPGA时钟周期与假定的模拟时间单位之比:

这样就可以假定前面提及的任意模拟时间单位。

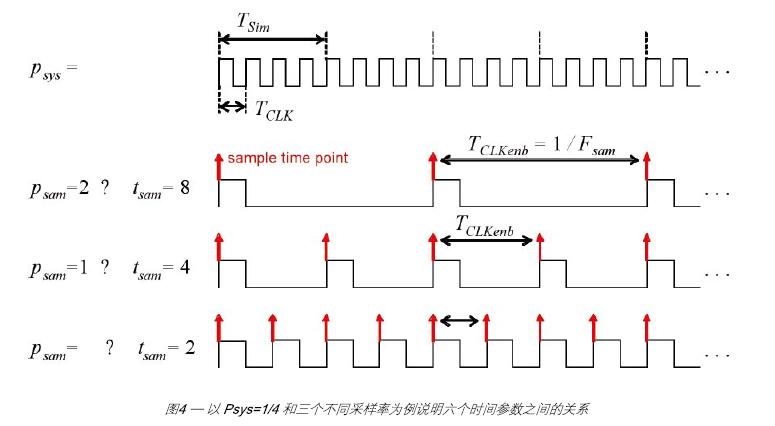

对于设计中System Generator部分的某个具体信号的采样周期Psam,既可进行明确设置(如在 Gateway-In单元中),也可从Up Sample或者Down Sample等采样率调整模块中获得。在进行明确设置时,需要输入以假定的时间单位为单位的具体数值。其设置对Simulink模拟和硬件实施都有影响。在模拟过程中,该数值决定了在模块真正可以改变状态之前必须调用该模块的次数。同样,在硬件实施中,该数值代表着时钟逻辑启用后的时钟周期的数量。由于在 System Generator设计中,所有的时钟启用信号都源自主FPGA的时钟输入,因此每个启用周期必须是FPGA时钟周期的整数倍。

分析参数

在第二类时间参数,即分析参数中,首先要考虑的是采样时间(ST)模块。该参数在系统实施中不使用硬件资源,仅用于Simulink模型中的分析目的。ST模块显示的tsam值指的是硬件实施中用于相关信号的时钟启用周期,其单位是FPGA时钟周期。

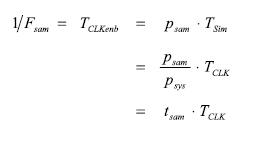

当设计人员在System Genertaor中的Icon Display属性框中选择下一项分析参数,即采样频率时,该模型中的每个Xilinx模块都会以MHz为单位显示采样频率Fsam,并用于该单元的实施。采样率与其它时间参数的关系如下:

其中TCLKenb是实施中启用的相关时钟的周期。

从上面的第二个等式可以清楚地看出,每个采样周期Psam都必须是Simulink系统周期Psys的整数倍,之所以如此,是因为仅有这些时钟启用信号是从FPGA系统时钟衍生出来的。第三个等式表明ST时钟显示的值是以FPGA时钟周期为单位的时钟启用周期。

选择时间参数的详细指南

上述控制系统示例详细说明了如何选择时间变量,该流程具体可分为以下五个步骤。

确定设备

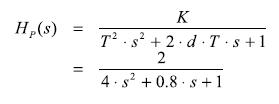

采用合适的传递函数对设备建模。在本例中,将设备当作PT2元进行建模,将增益系数K设定为2,时间常数T设定为20ms,衰减系数d设定为0.2。因此,如图3(a)所示,该设备为一个振荡元。

图3在无控、有PID控制和无抗饱合以及有抗饱和的情况下,输入命令后得到的整体系统模型(顶部)和设备输出

选择模拟时间单位

此时,可以选择基础模拟时间单位Tsim,这样设备的传递函数就有了便利的数值参数。在本例中,将Tsim设定为10ms。在上述参数设定完毕后,便得到如下设备传递函数:

设置Simulink系统周期

在拥有模拟时间单位后,将随之根据可用的硬件平台FPGA时钟周期TCLK设置Simulink系统周期Psys。在Spartan-3E入门套件中,系统时钟频率为50MHz,设定TCLK为20ns,得到:

确定采样频率

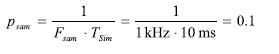

根据经验法则,数字控制器的采样率必须至少是设备截止频率的20倍。本示例设备的截止频率大约是30Hz,因此将采样频率设定为Fsam=1kHz。

设定采样周期

最后,在控制器前面的Gateway-In模块中设定采样周期参数Psam。在本例中,设置如下:

有了这些设置,就可以进行模型模拟,调整控制器参数并合成控制器逻辑。不过,有时FPGA时钟周期TCLK会显著小于基础时间单位Tsim,如在控制器是一个时钟频率比控制器本身要求高很多的更大规模设计的一个组成部分时。如此一来,由于在控制器真正处理下一个数据样本之前需要模拟大量无效的时钟周期,模拟时间会变得无比漫长。而这种情况下,可以在不影响设备一致性的同时,在模拟和实施中设置不同的Psys。之所以能这样做,是因为Psys值仅对设备的 System Generator部分有所影响。

更具体地说,可以在模拟控制系统时设置Psys=Psam。这样可确保只在必要时,即只有在模块真正改变状态的时候才会调用System Generator模块。在生成FPGA实施前,只需改回原来的Psys值即可。

结语

闭环控制系统的MBD要求设备传递函数的绝对时间测量指标与设计环境的时间参数保持一致。通过使用为DSP提供的Xilinx System Generator工具,本文为该问题提供了一个系统化的解决方法。

全部0条评论

快来发表一下你的评论吧 !