10nm芯片工艺设计 闸极成本将会降低

工艺/制造

描述

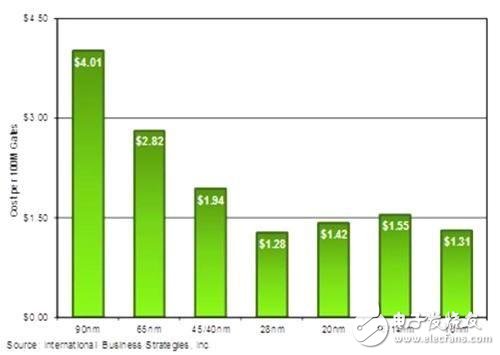

半导体供应链正面临越来越多的挑战,但10nm节点将有更大的机会能够从新技术工艺的微缩中获得更大的好处。根据国际商业策略(IBS)的分析预计,20nm和16/14nm工艺的闸极成本将会比上一代技术更高。而针对10nm闸极成本的分析则显现出不同的模式,如下图所示。

在历经16nm/14nm闸极成本持续增加后,可望在10nm时降低。虽然IBS并未预期工艺技术停止微缩,但预计试错成本(cost penalty)将出现在采用20nm bulk CMOS HKMG和16/14nm FinFET之际。对于闸极成本的这些项测已经证实是正确的,而当苹果(Apple)的20nm产品量产时,20nm芯片产能比起28nm时更低得多了。

台积电(TSMC)提供了另一个例子。该公司的28nm芯片月产能(WPM)达15万片,但其20nm芯片月产能大约将近三分之一——60,000WPM。 Globalfoundries在其纽约州马尔它(Malta)晶圆厂也拥有20nm产能,但该厂的主要着重于FinFET。至于三星电子 (Samsung Electronics)和联电(UMC),他们决定直接跳过20nm。随着16/14nm晶圆量产,同样地,16/14nm的晶圆产能又比28nm时更低。16/14nm的晶圆产量同样是由Apple驱动的,但利用16/14nm技术的时间长短则将由10nm工艺多快出现所决定。

相较于晶圆成本增加,10nm时的闸极成本将会降低,这是因为该工艺将会具有更高的闸极密度。为了可在10nm时取得更低的闸极成本,势必需要具备较高的系统与参数良率,但这并不难实现。10nm预计将会是一个高产能与长使用寿命的技术节点。台积电和三星都计划在2015年第4季投产10nm设计,所瞄准的客户显然就是Apple。如果能够在2016年或甚至在2017年中旨以前量产10nm,那么16/14nm将会是一个“短命”的技术节点。

然而,10nm所需的资本支出大约为20亿美元,可实现10,000 WPM的产能;如果要达到40,000 WPM产能,那么晶圆厂将耗资80亿美元。此外,实现10nm的设计至少需要1.5亿美元的最低成本,因此,如果芯片营收必须比设计成本更高10倍才能取得不错的投资报酬率,那么,10nm芯片就必须达到15亿美元的销售数字。在10nm节点以后,可能必须使用超紫外光微影(EUV)技术,而且必须在提升EUV吞吐量方面稳定进步。尽管450mm晶圆技术持续进展,但预计要到2020年以前才可能开始导入。

-

三星宣布:DRAM工艺可达10nm2015-12-14 0

-

【集成威廉希尔官方网站 】10nm技术节点大战2018-06-14 0

-

10nm、7nm等制程到底是指什么?宏旺半导体和你聊聊2019-12-10 0

-

传台积电10nm工艺良率不够,联发科或受影响2016-12-23 631

-

台积电10nm工艺存在较严重良率问题 多家厂商或受影响2016-12-23 892

-

2017年10nm手机“芯”谁能领先?2017-01-11 4029

-

小米6领衔的一大波手机将受影响,因为10nm工艺产能低2017-03-09 1173

-

台积电10nm工艺是什么2017-11-07 11795

-

台积电10nm工艺性能及量产情况2018-01-08 14757

-

揭秘Intel 10nm工艺,晶体管密度是三星10nm工艺的两倍2018-06-15 5410

-

Intel 10nm工艺难产 将会对AMD的业务有帮助2018-05-18 1060

-

英特尔官方否定10nm工艺难产一事,早在2017年就开发了10nm芯片?2018-07-16 937

-

Intel正式宣布第二代10nm工艺的处理器TigerLake 使用全新的CPU内核及GPU内核2019-05-09 1956

-

英特尔推出10nm SF工艺,号称比其他家7nm工艺还要强2020-09-27 3874

-

Intel的10nm工艺成功解决产能、性能等问题2021-01-14 3369

全部0条评论

快来发表一下你的评论吧 !