资料下载

×

多种哈希算法的可重构硬件架构设计

消耗积分:3 |

格式:rar |

大小:0.73 MB |

2017-12-05

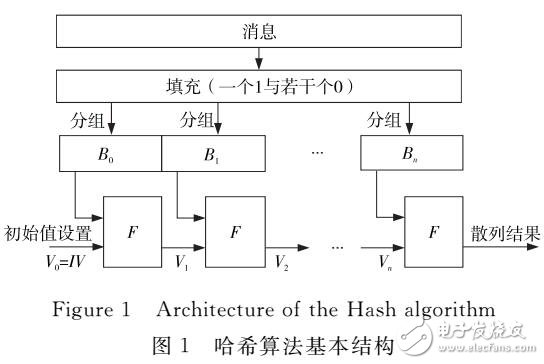

针对现有的哈希算法硬件架构仅实现少量几种算法的问题,设计了一种可实现SM3,MD5,SHA-1以及SHA-2系列共7种哈希算法的可重构IP,以满足同一系统对安全性可选择的需求。通过分析各哈希算法及其运算逻辑的相似性,该设计最大化地重用加法器和寄存器,极大地减少了总的实现面积。此外,该设计灵活可配,可以对内存直接存取。以Altera的Stratix II为FPGA目标器件,其最高频率可达100 MHz,总面积较现有设计减少26. 7%以上,且各算法单位面积吞吐率均优于现有设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章

下载排行榜

- 暂无相关数据