如何解决芯片在正常工作状态下经常出现的亚稳态问题?

描述

本文是一篇详细介绍ISSCC2020会议上一篇有关亚稳态解决方案的文章,该技术也使得FPGA在较高频率下的时序收敛成为了可能。亚稳态问题是芯片设计和FPGA设计中常见的问题,随着FPGA的发展,时序问题已经成为一个越来越难的挑战。单bit线网和逻辑通路扇出在巨大的芯片上扩散,而布线资源有限,这使得传统的时序收敛成为一场噩梦。在同步设计上实现时序收敛的传统技术一个接一个地碰壁,未能实现规模化。

Xilinx和Achronix在其新一代FPGA中解决了这一问题,在传统的逻辑和布线结构的基础上增加了片上网络(NoC)。NoC本质上改变了游戏规则,因为整个芯片不再需要在一个巨大的神奇汇流中实现时序收敛。现在,更小的同步块可以通过NoC传递数据,减轻了传统布线结构的负担,并将原来巨大的设计自动化工具问题分解成更小的、可管理的块。在进行NoC布线的两家供应商中,Xilinx和Achronix中,Achronix声称通过其二维跨芯片AXI实现了最快的NoC。NoC中的每一行或每一列都实现为两个工作在2 Ghz的256位单向AXI通道,同时在每个方向上提供512 Gbps数据流量。Speedster的NoC总共有197个端点,产生27 Tbps的聚合带宽,比FPGA的传统按位布线资源少了很多。

本文从一篇芯片设计顶会(ISSCC2020)文章中设计的一款解决低电压亚稳态问题的同步器作为着眼点,试图还原NoC架构引入FPGA芯片后对FPGA的时序收敛起到积极作用的全过程。报告视频非常精彩,深入浅出,环环相扣,娓娓道来。欢迎大家留言讨论。

昨天刚结束的ICAC2020线上会议,高峰期在线人数高达1.6万人,笔者有幸抽空听了半个下午,其中完整的听完了本文中所提到的亚稳态相关的一个会议。该报告是由上海交通大学的何卫锋博士做的,有关ICAC2020的详细信息请搜索微信“ICAC Workshop”详细了解。

报告相关文章的信息: Chuxiong Lin, Weifeng He, Yanan Sun, Zhigang Mao, Bingxi Pei, Mingoo Seok, “A Near-Threshold-Voltage Network-on-Chip with a Metastability Error Detection and Correction Technique for Supporting a Quad-Voltage/Frequency-Domain Ultra-Low-Power System-on-a-Chip,” IEEE International Solid-State Circuits Conference (ISSCC), 2020. 完整报告视频如下(25分钟):

随着物联网、机器人、无人机、可穿戴/植入设备等低功耗便携式设备越来越普及,超低功耗SoC芯片技术也面临着越来越大的挑战。为了降低这些SoC芯片的功耗,人们提出了如上图所示的各种技术。其中,近阈值低电压技术就是其中最受关注的一种。在超低电压下,可以很大程度的降低芯片的功耗,但随之带来了可靠性降低的代价。在上述SoC芯片中,往往具有多个电压频率域。由于超低电压下工艺等因素带来的任意两个时钟之间相位关系的不确定性,导致芯片在正常工作状态下经常会出现亚稳态问题。 什么是亚稳态?

当一个信号从Tx时钟域传递到Rx时钟域时,因为Tx_clk和Rx_clk时钟信号相位的不确定性,就有可能会造成数据信号D的上升沿会落在Rx_clk时钟上升沿的变化范围内,如果D信号的翻转(上升沿或下降沿)和Rx_clk的上升沿(采样沿)靠的足够近的时候,就会造成了采样出来的信号Q会出现非0非1的中间状态,如果信号Q这种非0非1的状态持续时间超过了Rx_clk的时钟周期,我们就称Q信号的这种非0非1的状态是亚稳态。

传统解决亚稳态的方法是采用上图中“打两拍”同步器的方法。这种方法可以有效的降低出现亚稳态的几率,但不能完全避免出现亚稳态的情况。随着电压的降低,亚稳态出现的几率越来越大。而传统的同步器无法解决上图中同步器的输入端出现亚稳态的情况,因此文章就提出了一种能够解决同步器输入端出现亚稳态情况的方案。 芯片中跨时钟域信号的解决方法就是加同步器,一个同步器不行,那就再加一个。 亚稳态窗口

以接收时钟沿为基准,以接收端时钟Tclk的频率作为将数据从亚稳态到稳定状态的一个分辨时间。当数据D的翻转在上图中黄色的亚稳态的窗口之内时,意味着同步器是无法在一个时钟周期内将D信号从亚稳态恢复为稳定状态。而对应的黄色区域的这个窗口,就称为是亚稳态窗口。 作者采用蒙特卡洛仿真了一下在65nm工艺下,电压从1.5V降低到0.4V的过程中,亚稳态问题出现的几率增大了11倍。

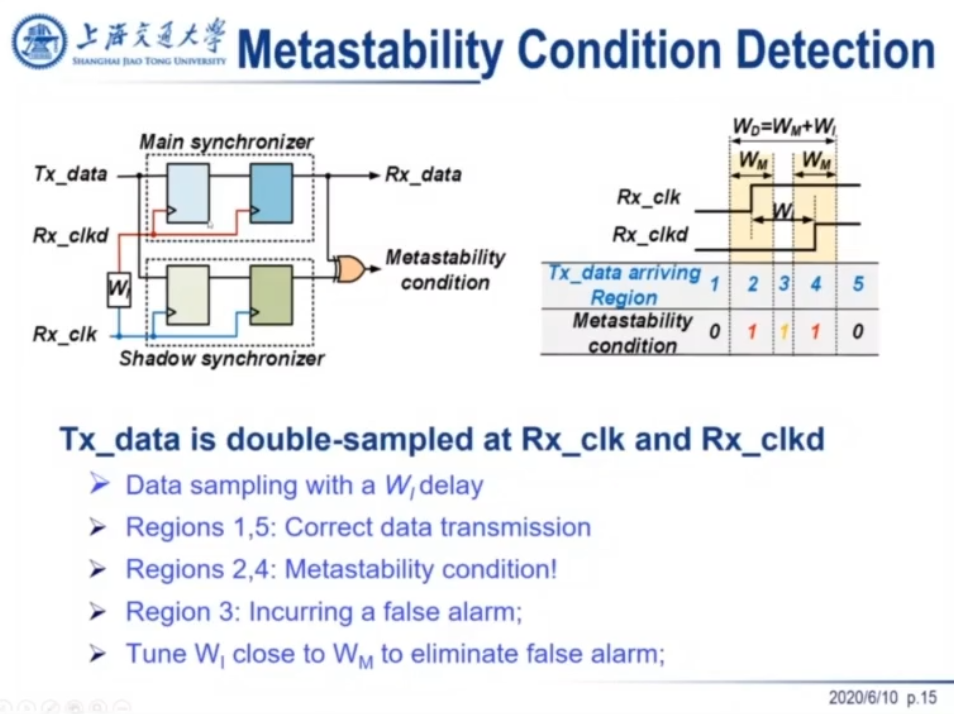

作者提出了上图中双采样的比较威廉希尔官方网站 ,可通过调整Rx_clk和Rx_clkd中间的相位差Wi,分成了五种情况来说明是否出现了亚稳态的情况。进而对如何控制亚稳态的出现进行评估和分析。 如果出现了亚稳态,可以要求发送端再重传一次信号,但无法从根本上解决亚稳态问题,亚稳态问题还是会过一段时间后再次出现。为了从根本上解决出现亚稳态的问题,定义了下图中两次亚稳态出现的时间间隔TTM。降低威廉希尔官方网站 中出现亚稳态出现的概率,就相当于是增大TTM的值。

为了增大TTM的值,可以考虑采样时钟上升沿与被采样数据翻转沿的相位偏差,根据这个偏差可以将威廉希尔官方网站 出现亚稳态的概率分类为Class-A和Class-B,还得到一个这两种状态下相位偏差的阈值。这样整个问题就转换为想办法当相位偏差处在Class-B的时候,想办法将其相位偏差转换到Class-A状态。

因此,解决办法就是在同步器威廉希尔官方网站 中添加移相器。始终保证采样时钟上升沿与被采样数据翻转沿的相位偏差处在Class-A的状态。作者设计了一个叫MEDAC的同步器单元,可以自动检测到是否即将出现亚稳态并实时对相位偏差进行调整。 工作原理如下:当威廉希尔官方网站 通过计数器TTM Timer发现该计数器的值小于了上图中的TTM阈值时,Phase selector模块就会驱动Phase shifter去调整Rx_clkd信号与Tx_data之间的相位偏差,使其相移偏差从Class-B状态转换到Class-A状态。从而降低了威廉希尔官方网站 出现亚稳态的风险。

把MEDAC同步器单元应用于异步FIFO中。

再把该异步FIFO应用于一款四个Router的NOC芯片中。

NoC芯片的结构和芯片图如下:

在测试了4G个数据包后,得到了很好的测试结果。在1V电压下,亚稳态出现的概率下降了几十倍,在0.4V电压下,亚稳态出现的概率下降几千倍。很好的解决了亚稳态问题。

原文标题:带有同步器的NoC结构是解决FPGA高速时序收敛的关键原因吗?

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

利用IDDR简化亚稳态方案2010-12-29 0

-

FPGA中亚稳态——让你无处可逃2012-04-25 0

-

FPGA触发器的亚稳态认识2012-12-04 0

-

亚稳态问题解析2013-11-01 0

-

9S12XEP100芯片如何使芯片在加密状态下读不到芯片ID?2017-04-26 0

-

简谈FPGA学习中亚稳态现象2018-08-01 0

-

adxl362使用在高温环境时,在静止状态下进入运动模式2019-01-17 0

-

FPGA的亚稳态现象是什么?2019-09-11 0

-

在FPGA复位威廉希尔官方网站 中产生亚稳态的原因2020-10-19 0

-

KEIL下载程序经常出现错误如何解决?2023-06-25 0

-

彩电经常出现故障2006-04-17 1193

-

如何解决触发器亚稳态问题?2018-09-22 9141

-

什么是亚稳态?如何克服亚稳态?2023-05-18 4809

-

亚稳态的分析与处理2023-06-21 4020

-

FPGA设计中的亚稳态解析2023-09-19 1870

全部0条评论

快来发表一下你的评论吧 !