PCIe中三种基本的I/O架构

描述

导言:这篇为PCIe要提及的时钟类型作个小铺垫,可以大致作一个了解,想深入了解可以参考更加细致的文献。

三种基本的I/O架构

1• 通用时钟(Common Clock)

2• 前向时钟(Forward Clock)

3• 嵌入时钟(Embedded Clock)

•这些I/O架构用于需要不同级别I/O带宽的各种应用

•处理器可能具有这些I/O类型中的一种或全部

•通常,相同的威廉希尔官方网站 可用于仿真不同的I/O方案以重复使用设计

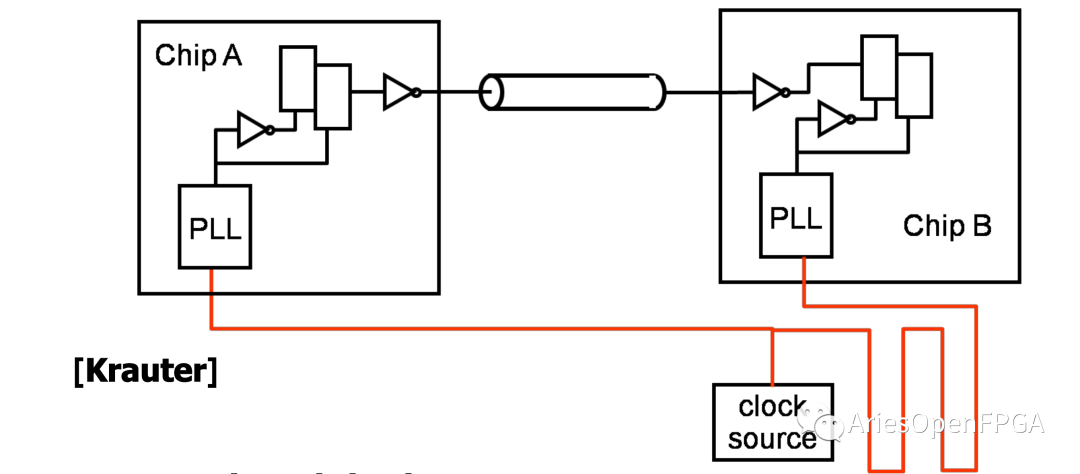

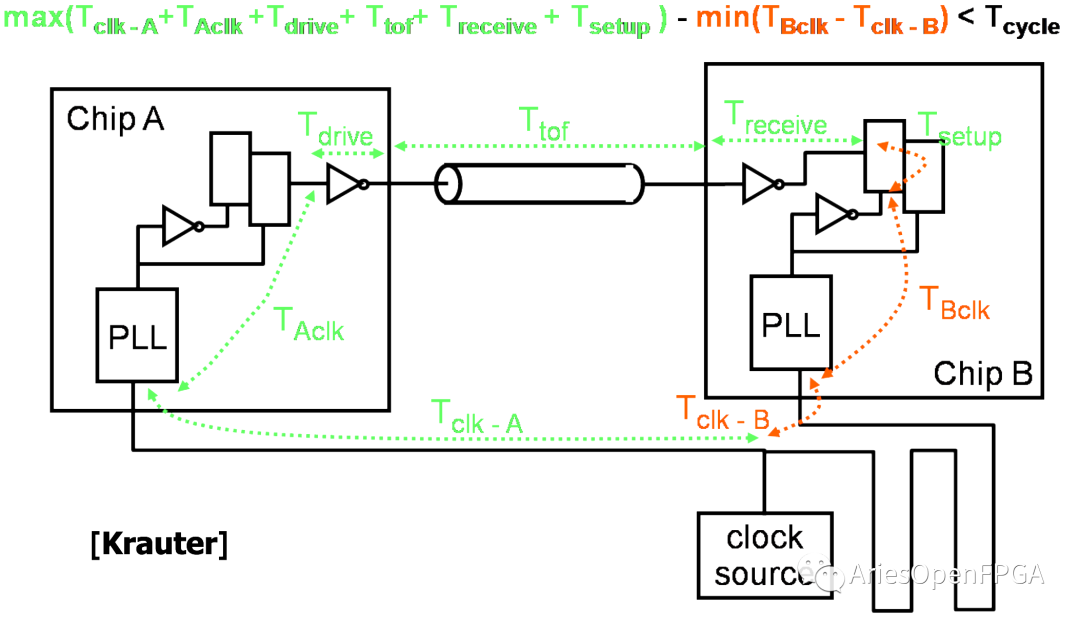

通用时钟的I/O架构

•在原始计算机系统中常见

•同步系统(Synchronous system)

•通用总线时钟控制芯片到芯片的传输

•需要等长的走线路径,以最大程度地减少时钟偏斜

•数据速率通常限制在0〜100Mb(数据可能比较老)

通用时钟I/O循环时间

通用时钟I/O限制

•难以控制时钟偏斜和传播延迟

•需要严格控制绝对延迟以满足给定的周期时间

•对芯片上威廉希尔官方网站 和威廉希尔官方网站 板布线路径中的延迟变化很敏感

•由于片上延迟和片外延迟之间的相关性低,难以补偿延迟变化

•虽然通常用于片上通信,但应用的速度受限

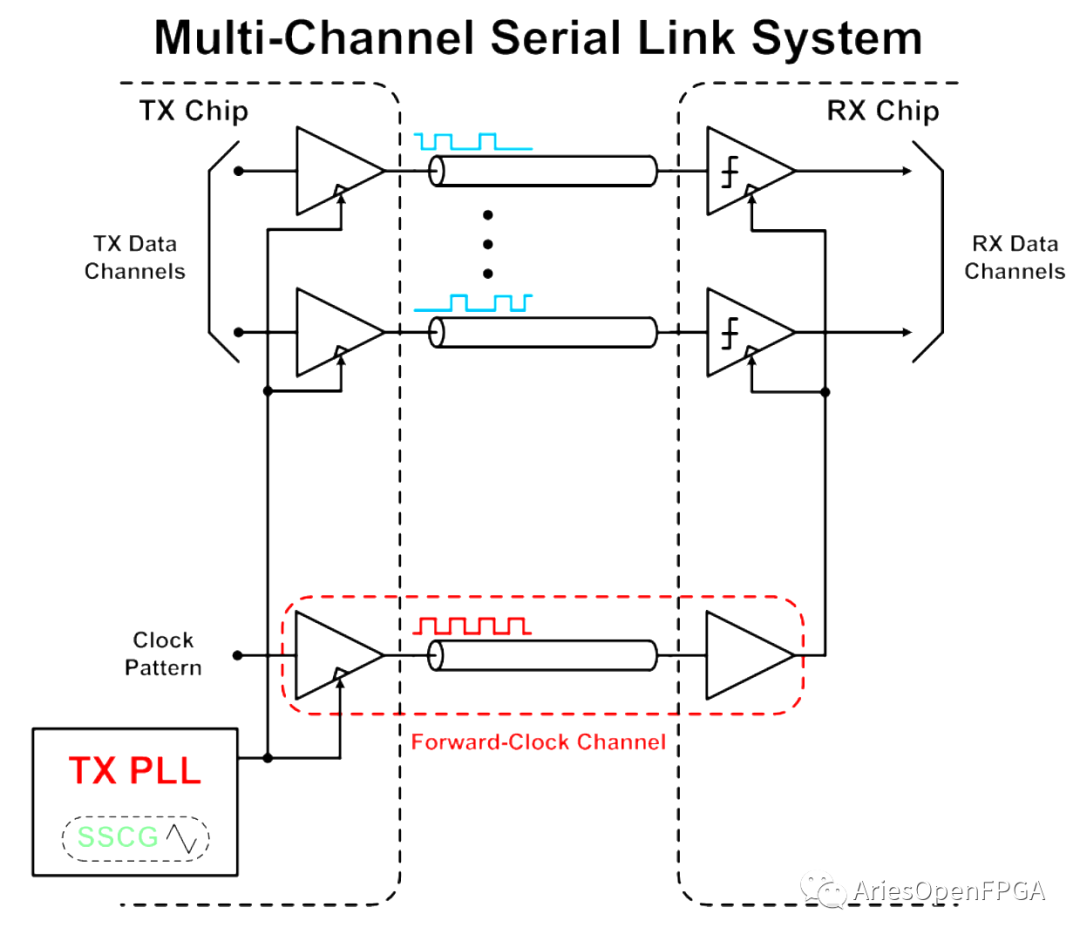

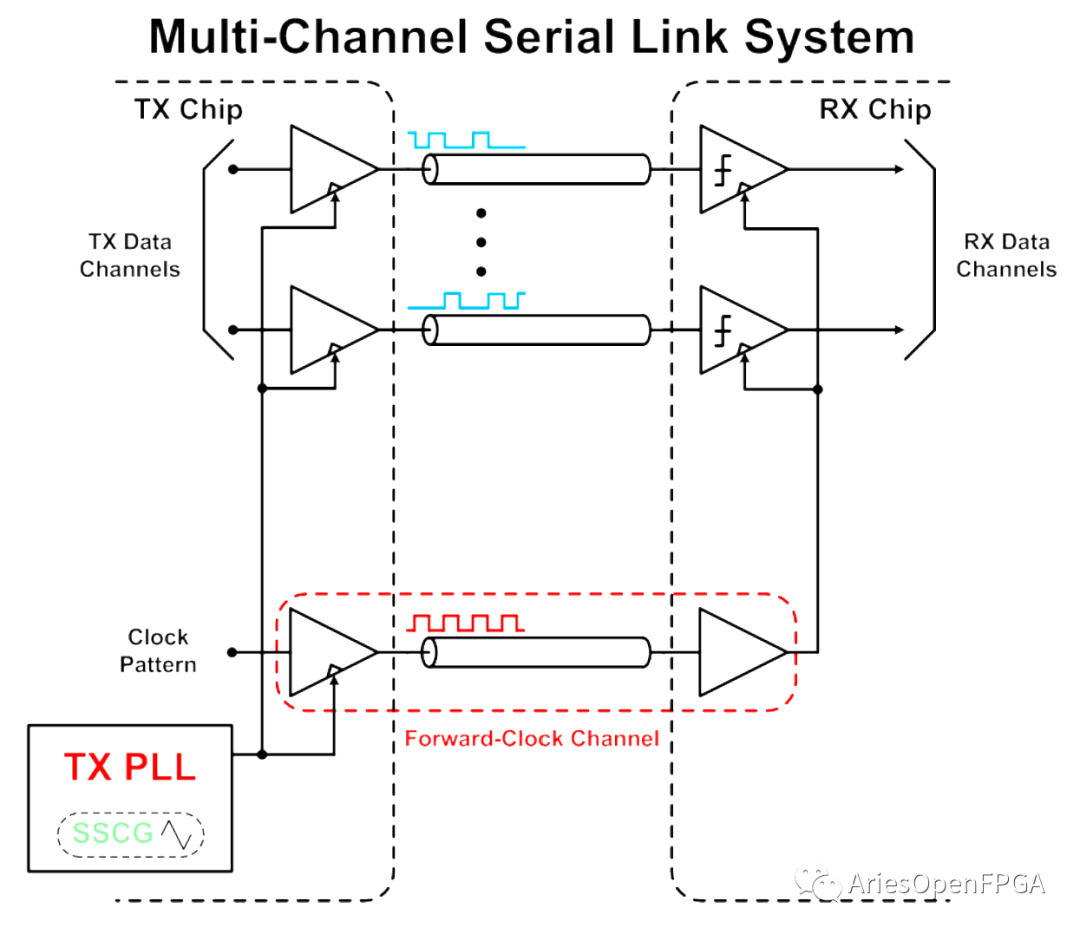

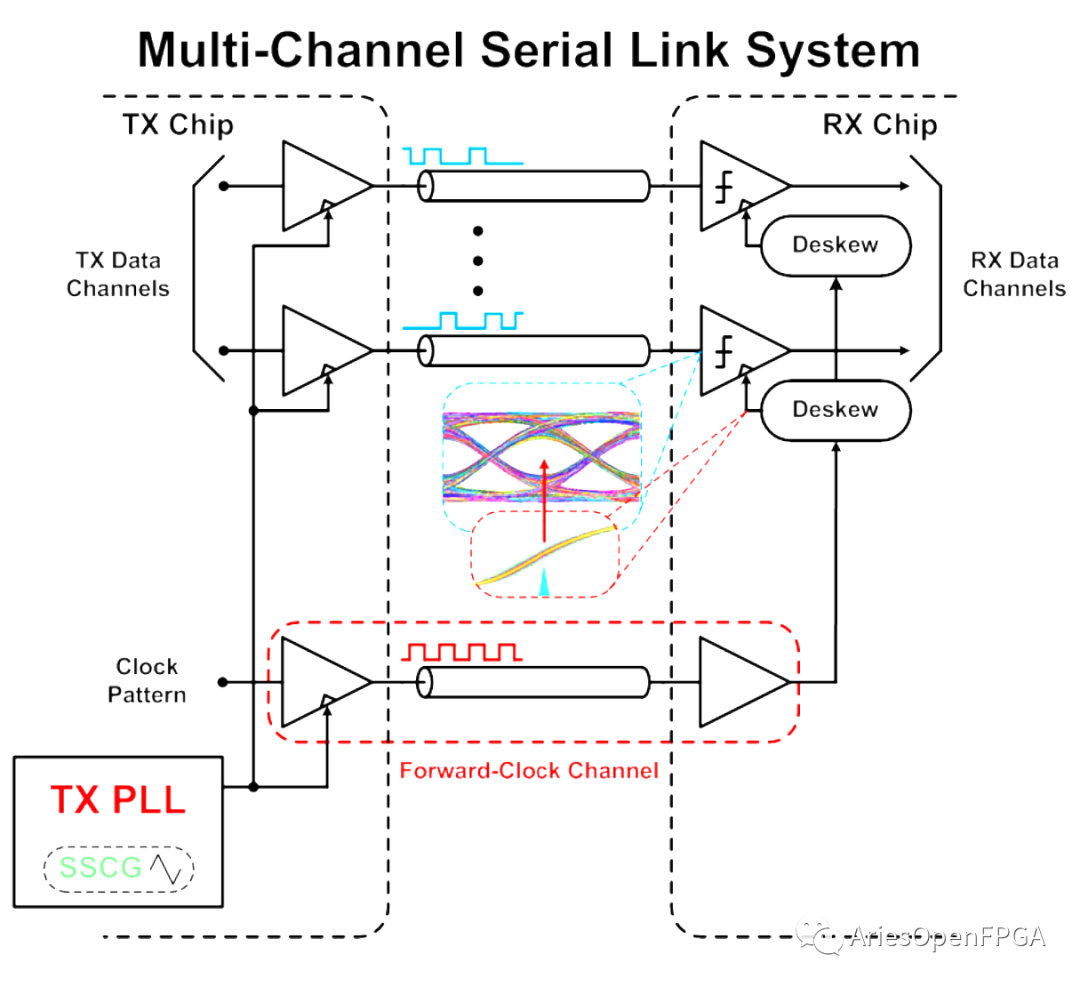

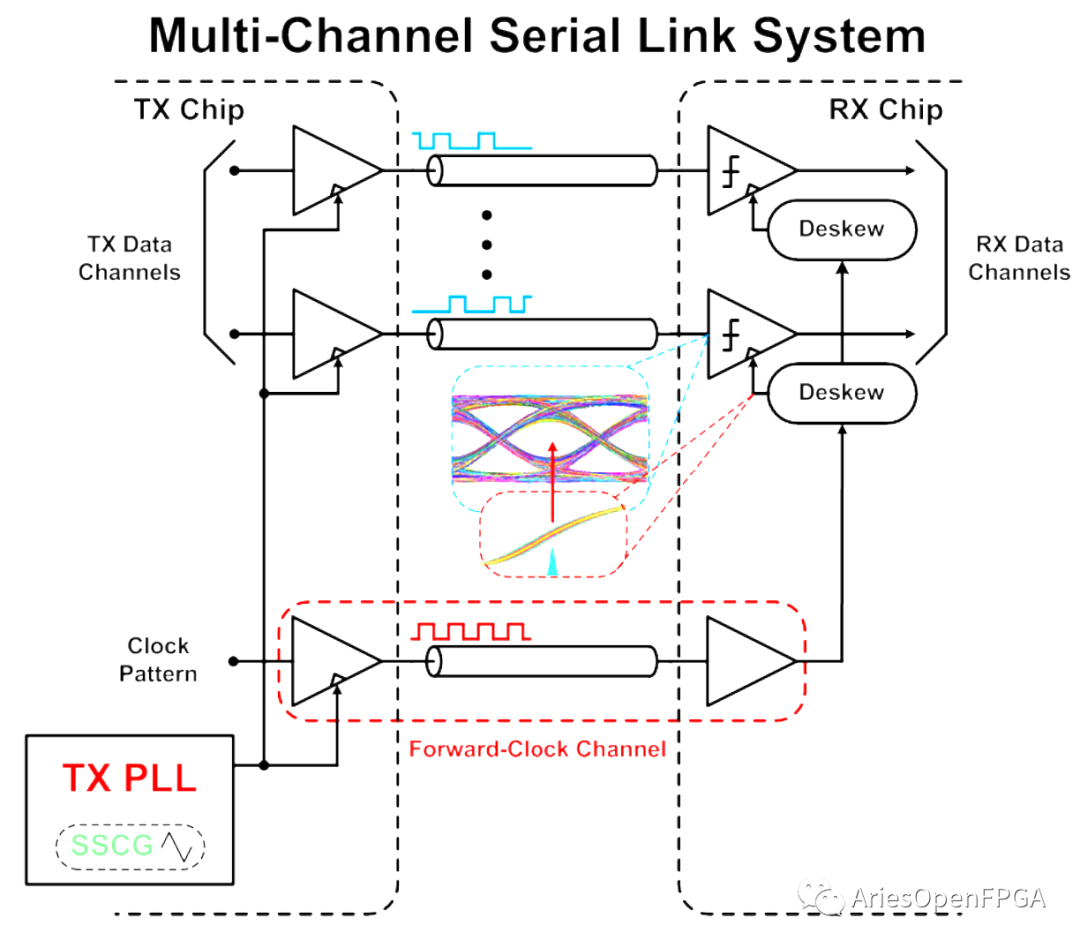

前向时钟I/O架构

•通常作为高速传输中,TX芯片到RX芯片的前向参考时钟

•同步系统(Mesochronous system)

•用于处理器内存接口和多处理器通信

•英特尔QPI

•Hypertransport(HT总线)

•需要一个额外的时钟通道

•“相干”时钟可实现从低频到高频的抖动跟踪

•需要好的时钟接收放大器,因为前向时钟会被通道衰减

前向时钟I/O限制

•时钟偏斜会限制前向时钟I/O性能

•驱动能力和负荷失配

•互连长度不匹配

•低通通道导致抖动放大

•前向时钟的占空比变化

前向时钟I/O偏斜校正

•每通道偏移校正可显着提高数据速率

•采样时钟调整为输入数据眼的中心时钟

•实施

•延迟锁定环路和相位内插器

•注入锁定振荡器

•相位采集可以是

•基于BER的附加输入相位采样器

•基于相位检测器,并带有额外的输入相位采样器,定期打开电源

前向时钟I/O威廉希尔官方网站

•TX PLL

•TX时钟分配

•复制TX时钟驱动器

•通道

•前向时钟放大器

•RX时钟分配

•去偏斜威廉希尔官方网站

•DLL/PI

•注入锁定振荡器

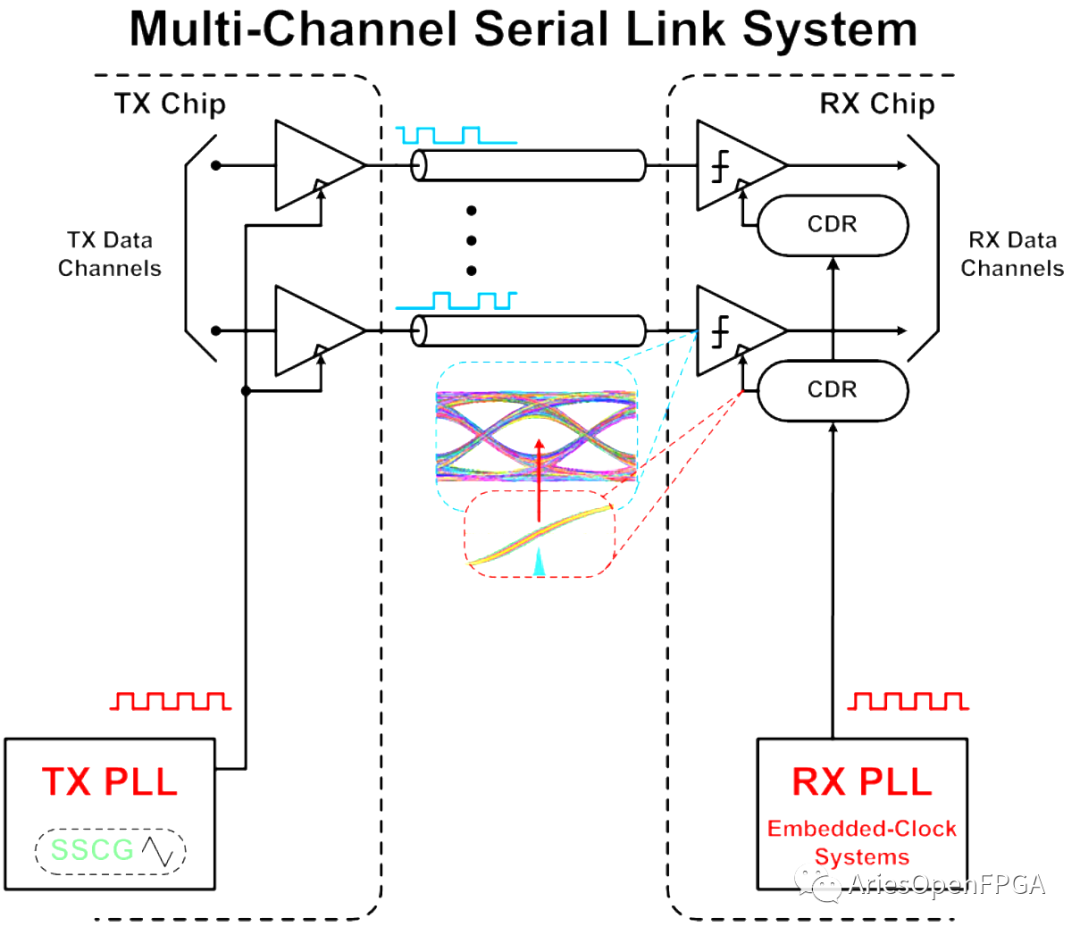

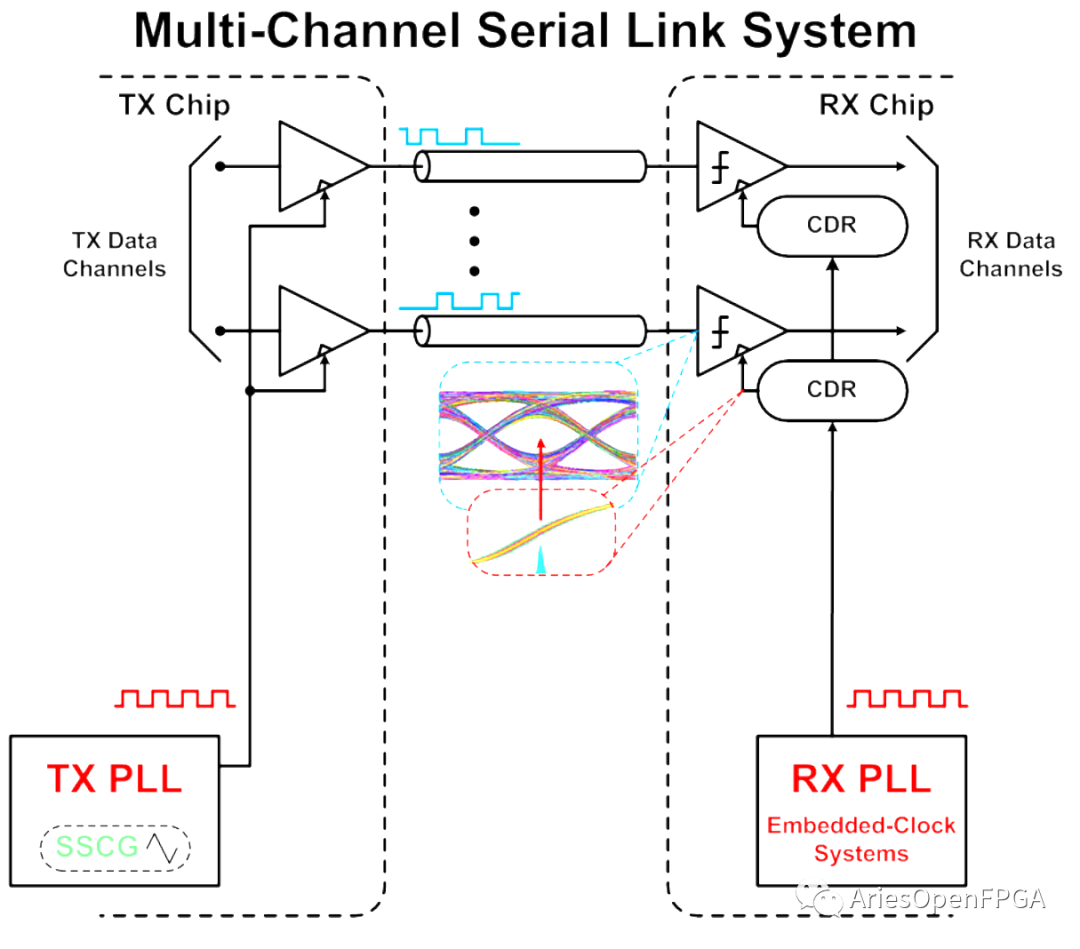

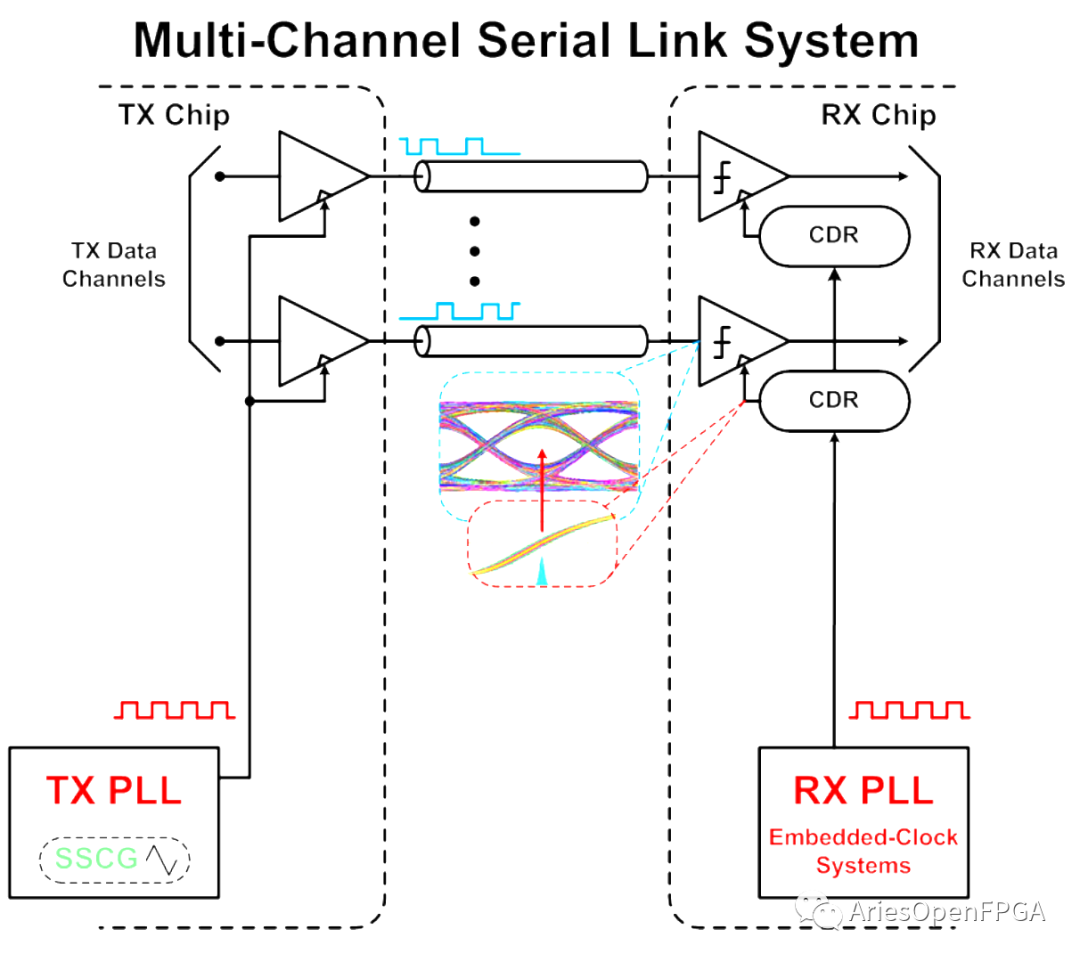

嵌入式时钟I/O架构

•可用于同步或准同步系统(mesochronousor plesiochronous systems)

•从输入数据流中提取时钟频率和最佳相位

•持续运行的相位检测

•CDR实施(应用)(CDR:clock and data recovery)

•基于每个通道的PLL

•双环带全局PLL或

•本地DLL/PI

•本地相位旋转器PLL

嵌入式时钟I/O限制

•抖动跟踪受CDR带宽限制(clock and data recovery)

•技术扩展允许具有更高带宽的CDR,从而可以实现更高的频率抖动跟踪

•一般而言,实现前向时钟需要更多的硬件(注:原文是,Generally more hardwarethan forward clockimplementations,我联系上下文自己翻译的,这里贴出来作为参考)

•额外的输入相位采样器

嵌入式时钟I/O威廉希尔官方网站

•TX PLL

•TX时钟分配

•CRD

•基于每个通道的PLL

•双环带全局PLL和

•本地DLL / PI

•本地相位旋转器PLL

•全局PLL需要将RX时钟分配给各个通道

原文标题:•I/O时钟架构

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

ARM架构核心板三种Form Factor之比较2014-09-28 0

-

三种主流芯片架构2018-08-14 0

-

单片机三种常用的软件架构2022-01-07 0

-

keil C51中三种Model的选择对编译有哪些影响2019-08-02 1065

-

嵌入式软件开发中三种程序架构2022-02-11 2338

-

磁盘阵列三种架构的用途及区别解析2021-01-27 3791

-

一文带你了解嵌入式领域三种处理器通用的架构2021-03-05 5525

-

浅析单片机三种应用程序的架构2021-04-07 4438

-

Webrtc音视频会议之Mesh/MCU/SFU三种架构2021-10-26 844

-

深入介绍嵌入式开发中三种不同的程序架构2022-05-24 1622

-

比较三种基本电源架构的权衡2022-08-10 2415

-

FPGA中三种常用复位威廉希尔官方网站2023-05-14 2579

-

基于FPGA的PCIE I/O控制卡通信方案2023-09-01 3402

-

光伏发电系统中三种DC-DC转换威廉希尔官方网站 的研究2023-11-06 272

-

区域架构和 MCU I/O 扩展2024-09-09 101

全部0条评论

快来发表一下你的评论吧 !