关于利用IBERT核对GTX收发器板级测试的原理与过程详解

电子说

描述

一、概述

IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。

IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT可以获取误码率,观察眼图,调节串行收发器的参数,从而有助于判断可能存在的问题,便于验证硬件的稳定性和信号完整性。

二、测试原理

GTX接收和发送方向均由PMA和PCS两部分组成,PCS提供丰富的物理编码层特性,如8b10b编码、时钟校准等功能,PMA部分为模拟威廉希尔官方网站 ,提供高性能的串行接口特性,如预加重、均衡等功能。GTX同时还提供动态配置接口,用于动态的修改GTX的配置。

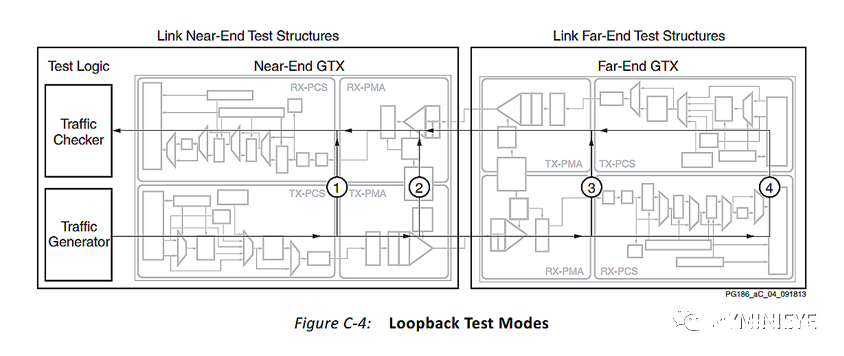

IBERT 工具的环回模式有近端PCS环回测试(路径①),数据流仅通过近端GTX的PCS部分,可用于验证近端GTX中PCS收发双向的设置;近端PMA环回测试(路径②,数据流通过近端GTX的PCS、PMA,可用于验证近端GTX收发双向的设置;远端PMA环回测试(路径③),数据流通过近端GTX的PCS和PMA,远端的GTX的PMA部分,通过两个GTX之间的物理连线,验证两个GTX之间物理联系的可靠性,以及验证两个GTX的PMA部分设置的正确性;远端PCS环回测试(路径④)验证近端收发器和远端收发器的通信状况;以及None无环回模式即通过外部连接发送和接收。

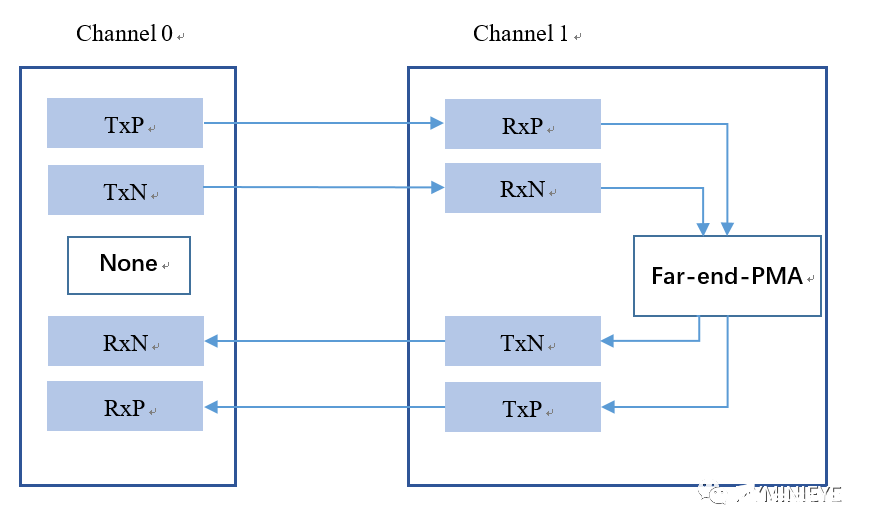

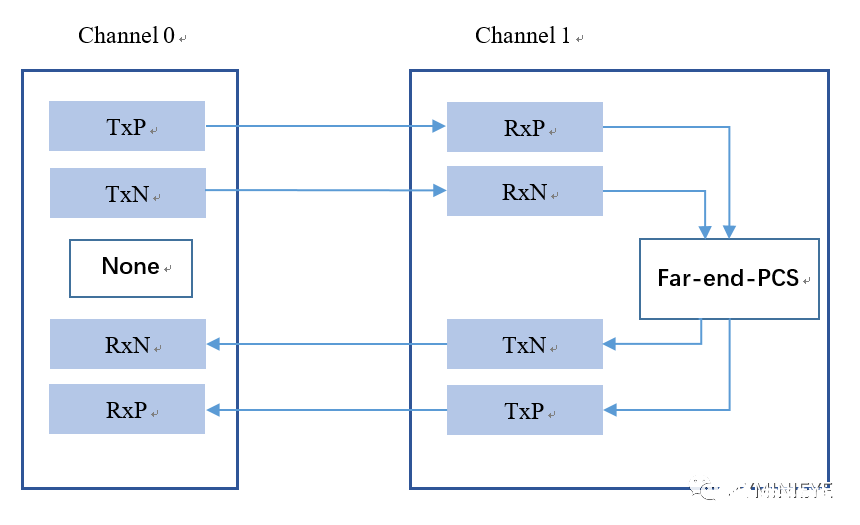

远端PCS或PMA环回测试时板卡下载IBERT核生成的bit文件,通过两个通道上的Tx和Rx接口互相连接,其中一个通道上的模式设置为Far_End_PMA或Far_End_PCS模式,另一个通道设置为默认的None模式并监测误码率。

Vivado中IBERT默认模式为None模式,收发器通过外部连线由外部环回进行自收自发而实现。可将同一组收发器的TX和RX进行短接,在RX接收端接收TX发送的数据后,通过比对发送和接收的数据,从而得出接收端误码的统计值。

三、测试过程

1、器件支持速率说明

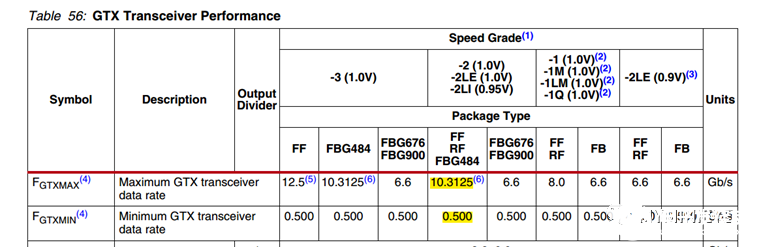

GTP , GTX , GTH都是串行收发器,区别在速率不一样,在不同的器件中叫的名字不同而已,由于在vivado创建工程时选择对应的器件型号,使用IBERT时会自动根据器件型号检查所选的线速是否在器件支持的线速范围以内。

在示例中使用器件型号为xc7z030ffg676-2,在数据手册中根据7系列-2的速度等级和FF封装可查到该器件GTX的数据率范围为0.5~10.3125G,因此在测试的过程测试速率应在此范围内。(参考文档DS182)

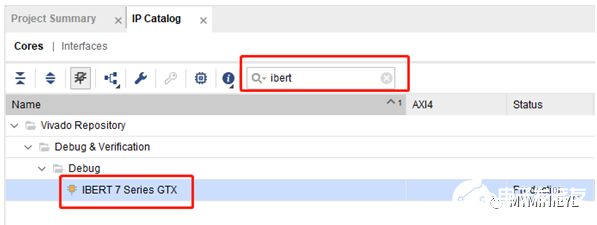

2、IBERT IP核配置

(1)首先打开vivado,新建工程后从IP Catalog找到IBERT并双击打开;

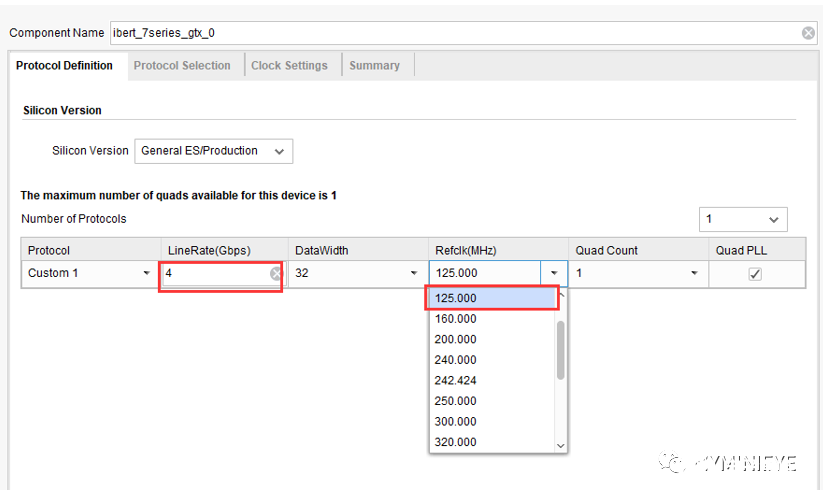

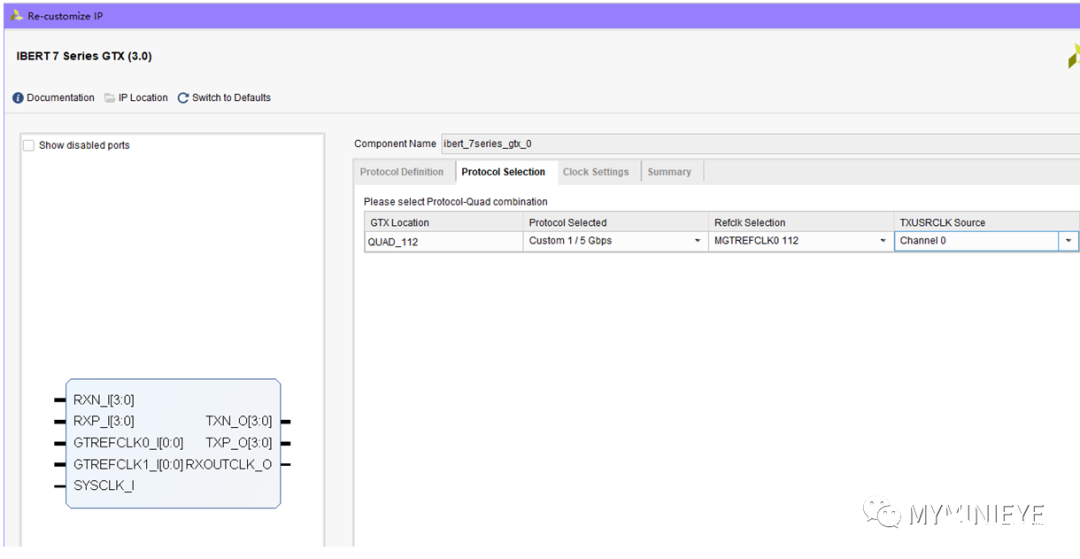

(2)IBERT测试协议选择Custom1,GTX参考时钟选择频率为125MHz,在配置的过程中,Refclk可选的频率是由LineRate决定,由于在板卡上Refclk已固定为125MHz,因此测试所选择的线速应支持125MHz的参考时钟。(以4G线速为例)

(3)在开发板中,差分时钟与MGTREFCLK0112连接,因此参考时钟选择MGTREFCLK0112。

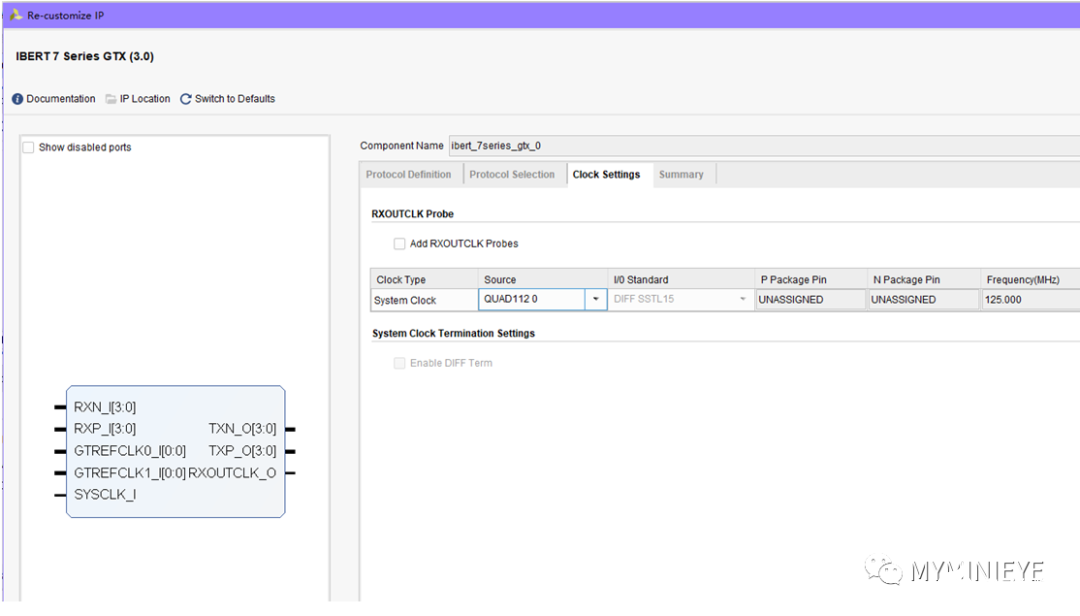

(4)将GTX输入的125MHz的时钟同时作为IBERT内部逻辑的工作时钟,这样就可以不使用额外的外部时钟。

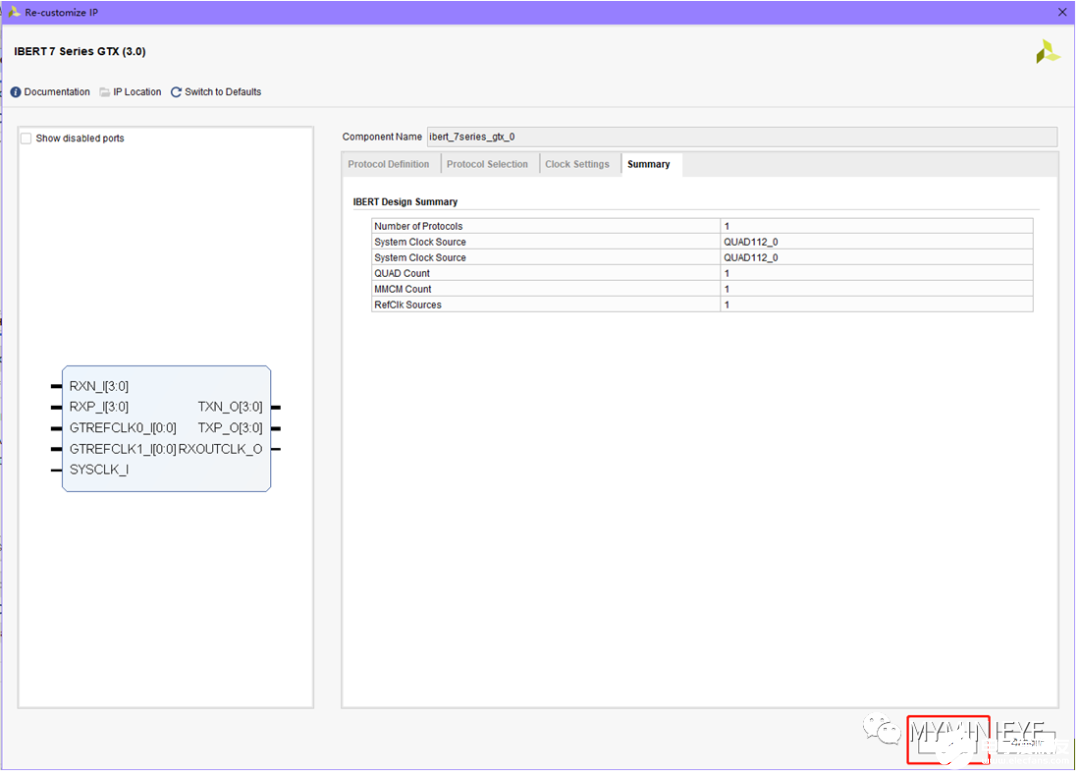

(5)配置结束后点击OK

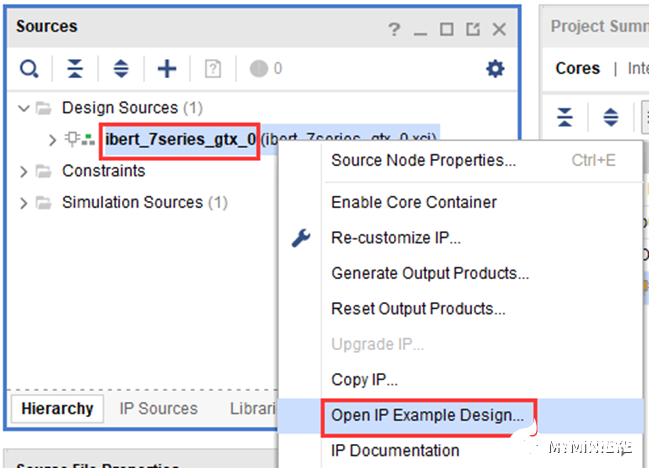

(6)完成配置后,右击打开exampledesign工程

(7)打开exampledesign工程后,经过Synthese、Implementation,生成bit文件即可进行烧录。

3、测试

(1)近端PCS或PMA环回测试(Near-End PCS/PMA loopback)

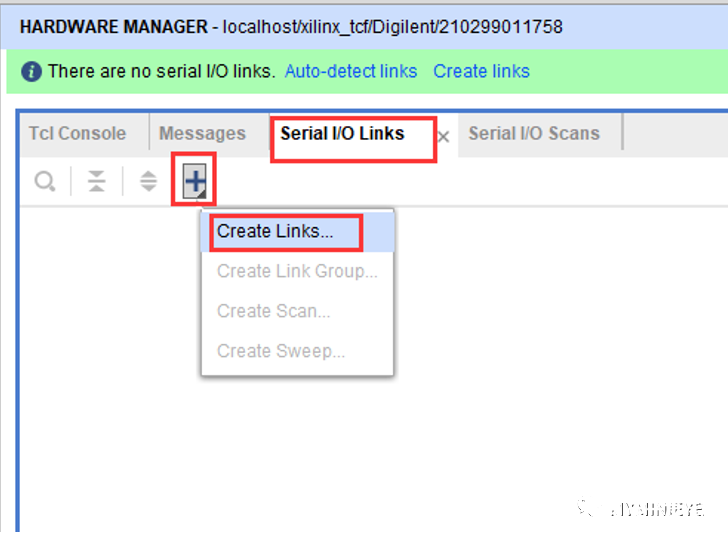

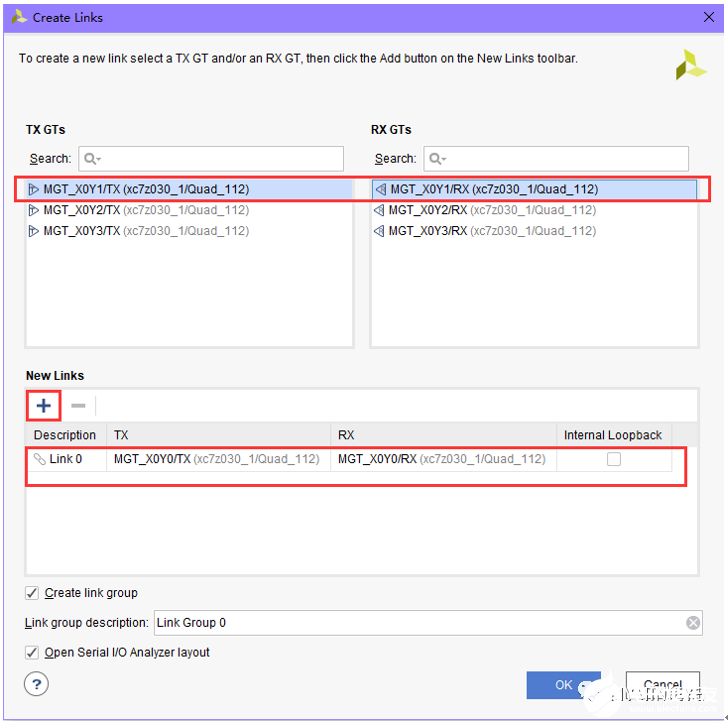

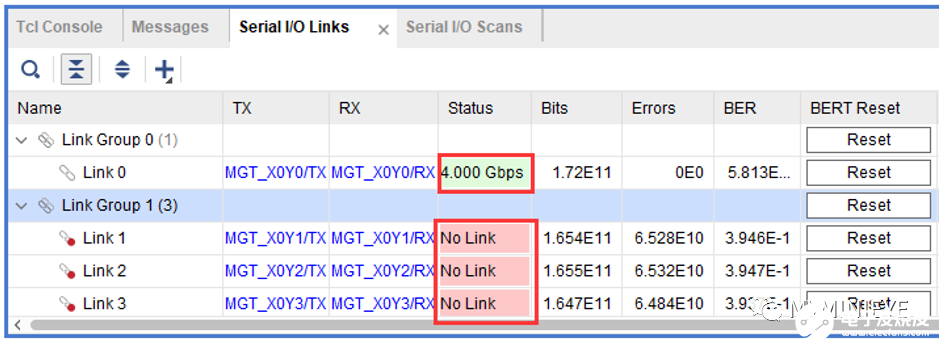

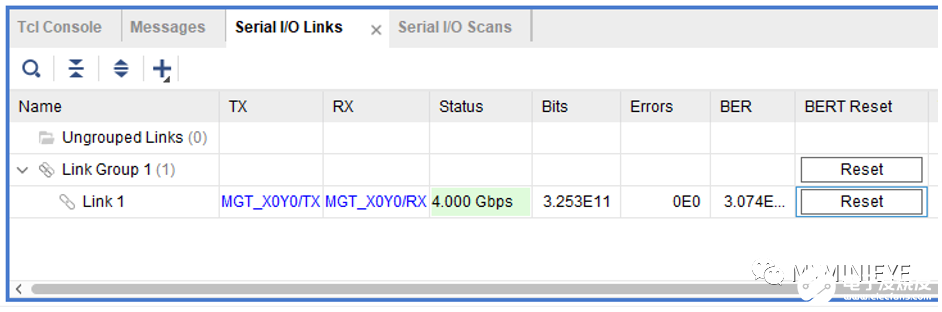

无需外部连线,烧录成功后,在Serial I/O Links窗口创建连接,将同1个GTX中同一个通道的TX和RX建立link。(也可以选择auto-detectlinks)

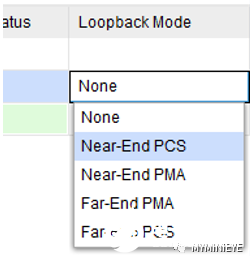

建立link后,若链路中连续五个数据传输成功,则认为链路连通,否则为未连通。在serial I/O link最右端的loopback mode选择近端PCS(或PMA)环回模式,在改变模式时可能会出现误码,需要点击reset重新监测。

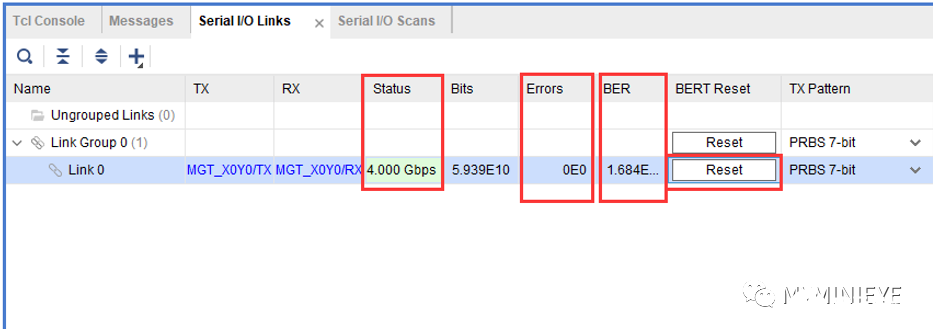

经过一段时间测试, Errors的数值一直为0,表明测试过程中没有出现误码,说明板级层面的GTX硬件工作稳定。

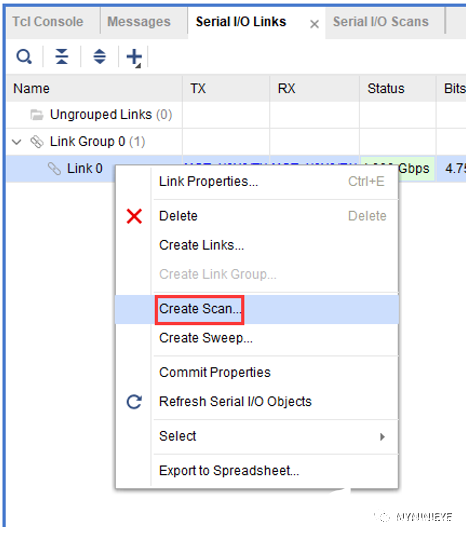

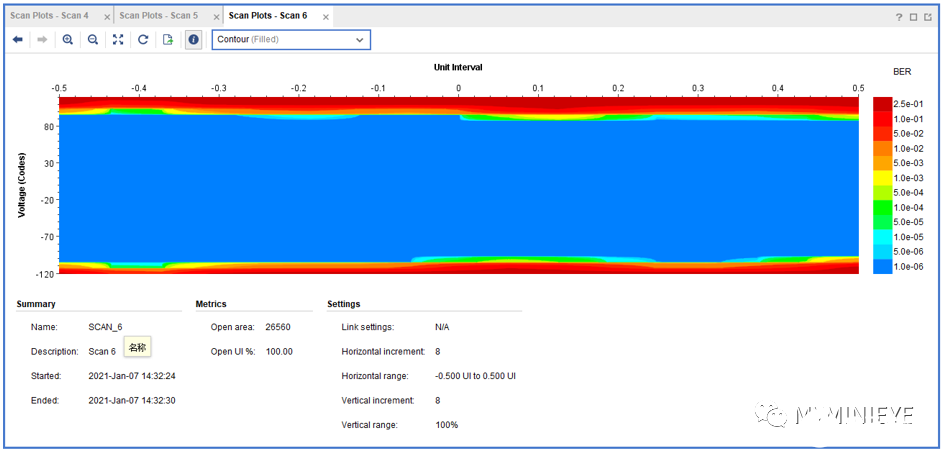

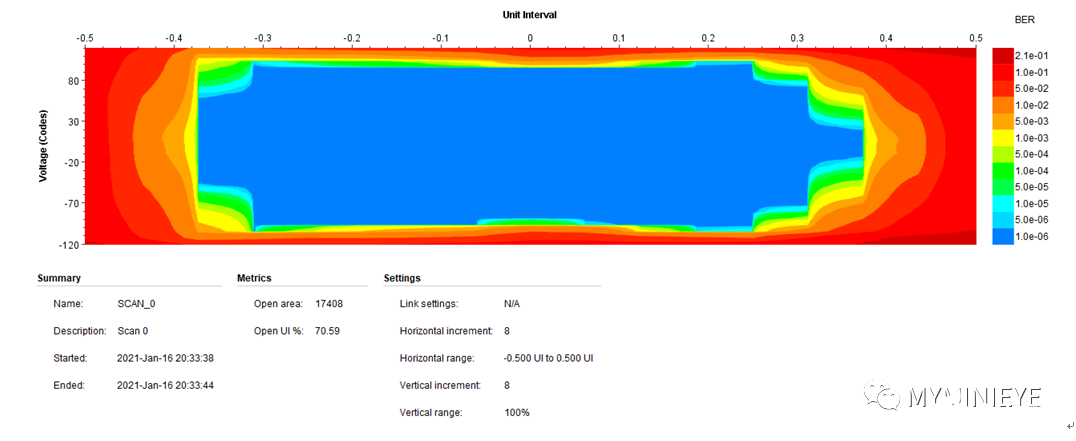

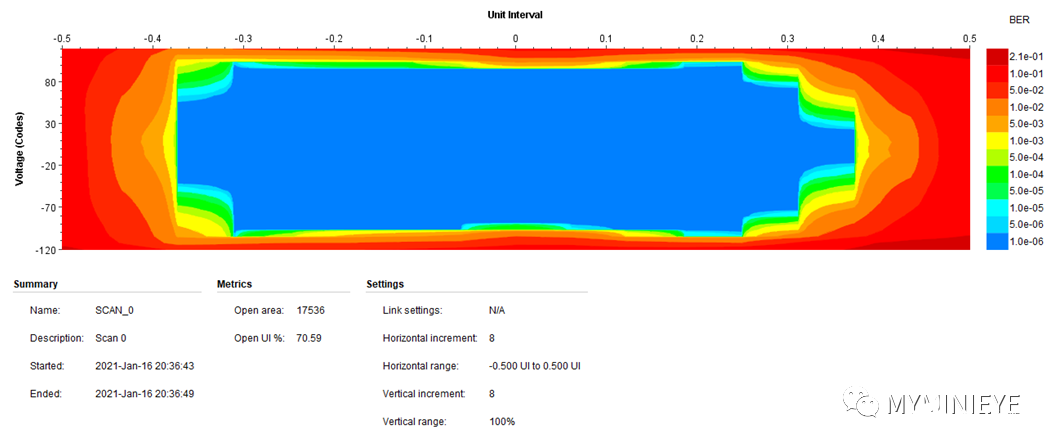

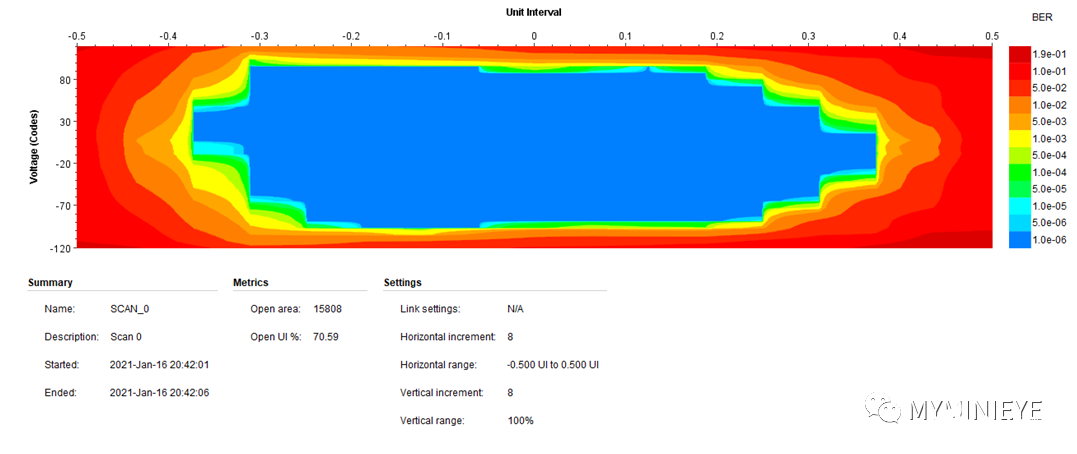

眼图可以更直观的观察GTX的信号完整性,右键所连接的link,选择create scan,便可以生成眼图。

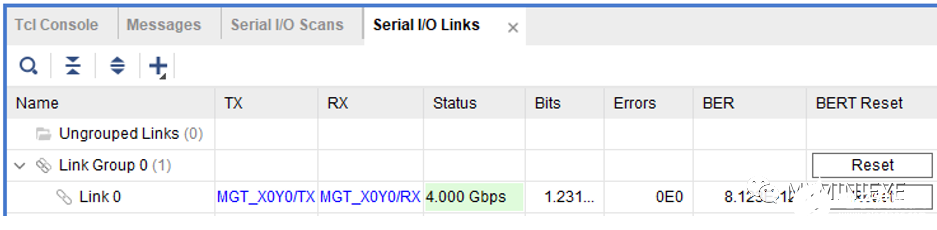

在Serial I/O link窗口中,errors为误码个数,BER为误码率,在reset之后,errors和BER会恢复为0重新统计,通常在改变其他的参数后可能会出现少量的误码,此时需要reset后重新统计误码。TX Pre-Cursor和TX Post-Cursor为预加重和后加重,TX Diff Swing为摆幅,RX Pattern和TX Pattern为输入、输出数据类型,提供不同位宽的伪随机码、慢时钟(101010……)和快时钟(11111111110000000000……),需要注意的是输入和输出的数据类型应设置为同一种类型,Loopback Mode为环回模式,默认为None无环回模式,Near-End PCS为近端PCS环回模式,Near-End PMA为近端PMA环回模式,Far-End PCS为远端PCS环回模式,Far-End PMA为远端PMA环回模式。若信号传输质量不够理想,可以通过在serial I/O link的参数设置进行调整,再重新扫描眼图查看是否有改善。

为了测试GTX四个通道的误码率,创建多个links,对四个通道都进行近端环回测试

(2)远端PMA环回测试(Far-End PMA loopback)

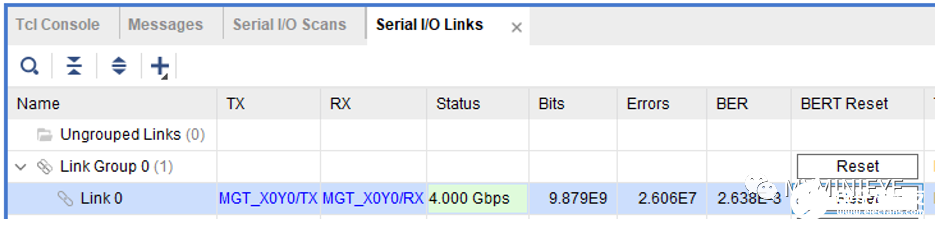

在一个板卡上烧录ibert生成的bit文件,将其中两个通道的Tx和Rx接口互连,一个通道设置为Far-EndPMA模式,另一个通道设置为None模式并监测误码情况和眼图。

创建对应连接的link并查看误码率和眼图

(3)远端PCS环回测试(Far-End PCS loopback)

在一个板卡上烧录ibert生成的bit文件,将其中两个通道的Tx和Rx接口互连,一个通道设置为Far-End PCS模式,另一个通道设置为None模式并监测误码情况和眼图。

创建对应连接的link并查看误码率和眼图

(4)None模式的测试方式

板卡下载IBERT核生成的bit文件,然后将同一通道的Tx与Rx接口连接起来,环回模式设置为None,实现自发自收。

四、总结

通过环回和开环方式的误码率测试,可判断出存在的问题以及测试出板卡实际支持的速率。IBERT可在运行过程中设置高速串行收发通道的各项参数,并提供了多种环回模式及多种测试激励源,并可通过自动扫描测试,确定收发的最佳参数。可以满足硬件测试时对高速串行收发通道信号测试的大部分需求,在故障定位等场合均可使用。

编辑:lyn

-

#fpga 利用IBERT IP核实现GTX收发器硬件误码率测试实例明德扬科技 2023-09-05

-

是否有关于为GTY收发器发布IBERT的讨论?2018-09-28 0

-

Vertex 7 GTX收发器中没有丢失同步是什么2020-06-16 0

-

在Virtex-5/6 GTP / GTX收发器中如何实现JTAG2020-06-18 0

-

7系列设备中的GTX收发器如何获得最佳功耗?2020-07-19 0

-

如何将GTX收发器的RX,TX引脚连接在一起?2020-07-22 0

-

请问7系列FPGA收发器向导v2.3 GTX名称不正确的原因?2020-07-28 0

-

请问如何提高GTX收发器的RX能力?2020-08-12 0

-

为什么GTX收发器的速度比基本的IOB快?2020-08-13 0

-

利用 IBERT 进行 GTX 信号眼图测试 精选资料分享2021-07-20 0

-

利用IBERT核对GTX收发器板级测试2023-06-21 0

-

用于Kintex-7 FPGA GTX的Chipscope Pro集成误码率测试资料说明2019-02-26 897

-

GTX/GTH收发器时钟架构应用介绍2021-03-29 6772

-

利用IBERT IP核实现GTX收发器硬件误码率测试实例2022-08-14 2073

-

基于IBERT的GTX数据传输测试2023-08-31 2565

全部0条评论

快来发表一下你的评论吧 !