在SpinalHDL中如何优雅地实现寄存器总线读写

描述

对于FPGA系统设计里,寄存器控制通道的设计是系统控制中必不可少的部分。今日且看SpinalHDL中如何优雅地实现寄存器总线读写。

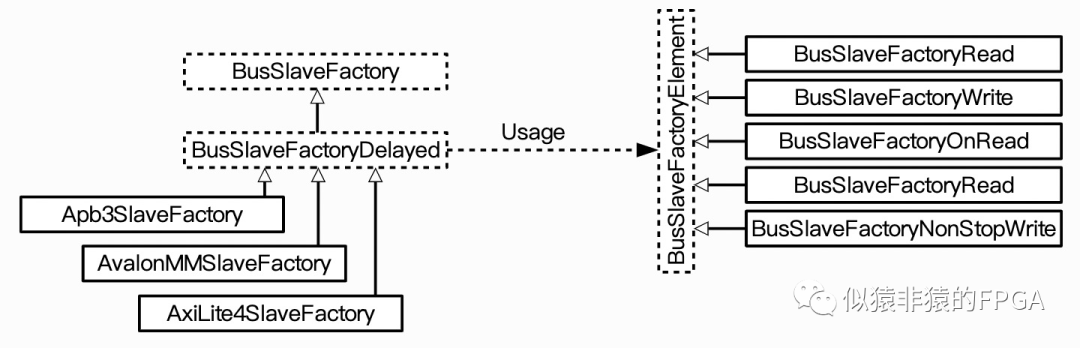

Bus Slave Factory

在SpinalHDL里,其Libraries里提供了关于总线相关的库。包含AMBA3、AMBA4、AVALON等总线类型,并提供了bus slave factory工具:

通过bus slave factory,我们可以方便地实现寄存器读写,其提供了一系列寄存器读写方法。这里列举几个常用的方法(完整的方法列表可参照SpinalHDL-Doc):

read(that,address,bitOffset)

注册寄存器读操作到指定地址,比特偏移为bitOffset 。

write(that,address,bitOffset)

注册寄存器写操作到指定地址,比特偏移为bitOffset。

readAndWrite(that,address,bitOffset)

注册寄存器读写操作到指定地址,比特偏移为bitOffset 。

readMultiWord(that,address)

注册大位宽寄存器(超过总线数据位宽)读操作到指定地址,其中address地址存放对应低比特,高比特地址向上累加。

writeMultiWord(that,address)

注册大位宽寄存器(超过总线数据位宽)写操作到指定地址,其中address地址存放对应低比特,高比特地址向上累加。

除此之外,bus slave factory还提供了printDataModel函数用于打印寄存器列表。而且在生成RTL时,其会自动检测寄存器地址是否存在冲突。

AXI4-Lite总线实现

这里以AXI4-Lite总线举例,通过AXI4-Lite总线读写三组寄存器:

en:单比特信号,可读可写。

plus:单比特信号,可读写,写1自动清零。

cnt:64比特信号,可读。

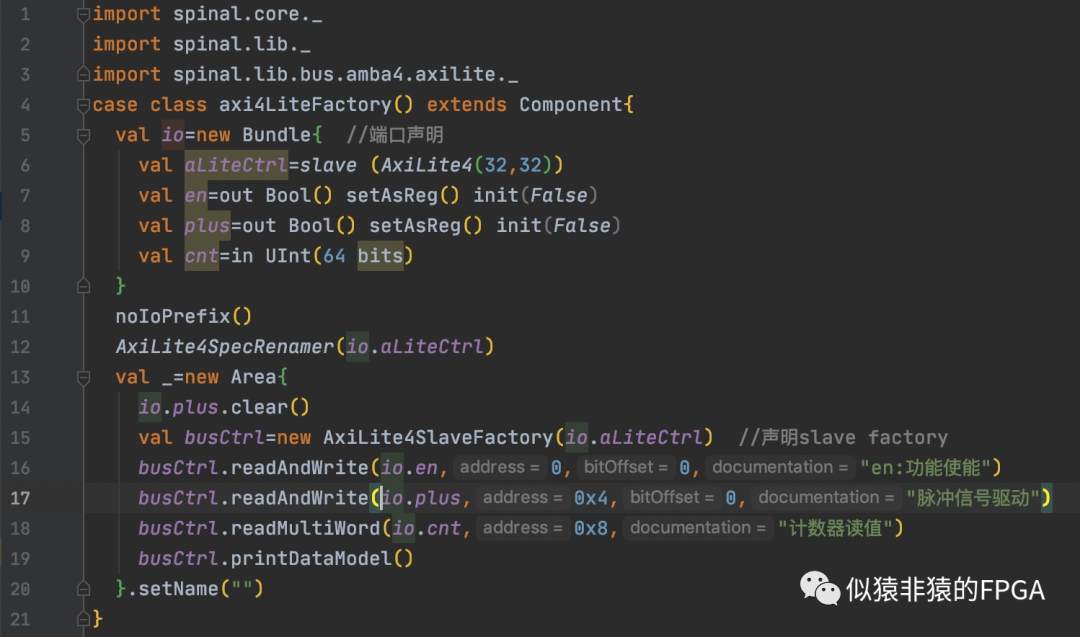

这里给出完整的代码结构:

这里代码5~10行代码声明模块端口,第12行代码规范AXI4-Lite端口名称。代码第15~18行通过slave factory实现AXI4-Lite寄存器读写。代码第19行打印输出寄存器列表。

由于plus写1清零,因此代码14行用于实现清零操作。

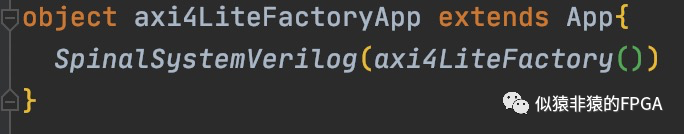

通过下面的语法生成RTL代码:

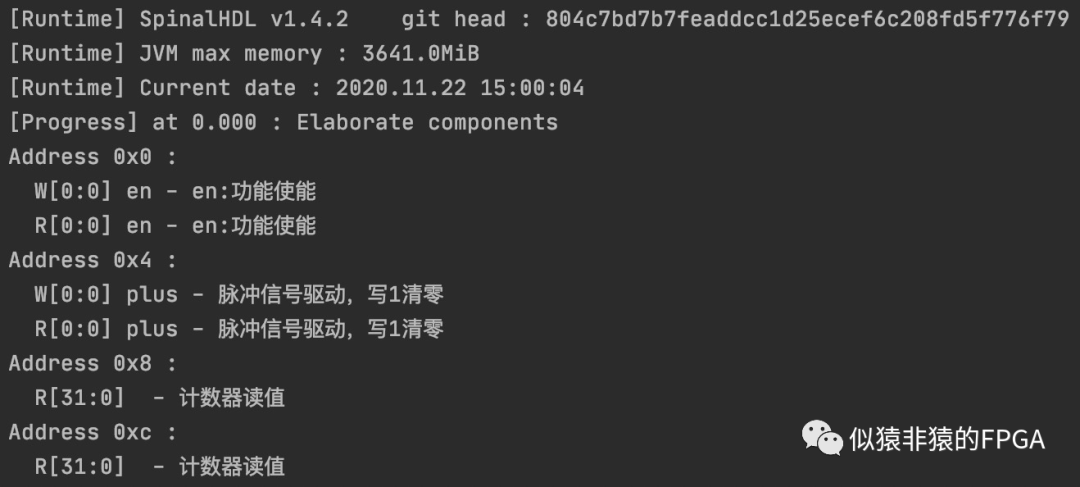

在生成RTL代码的同时,会打印寄存器列表:

仿真结果

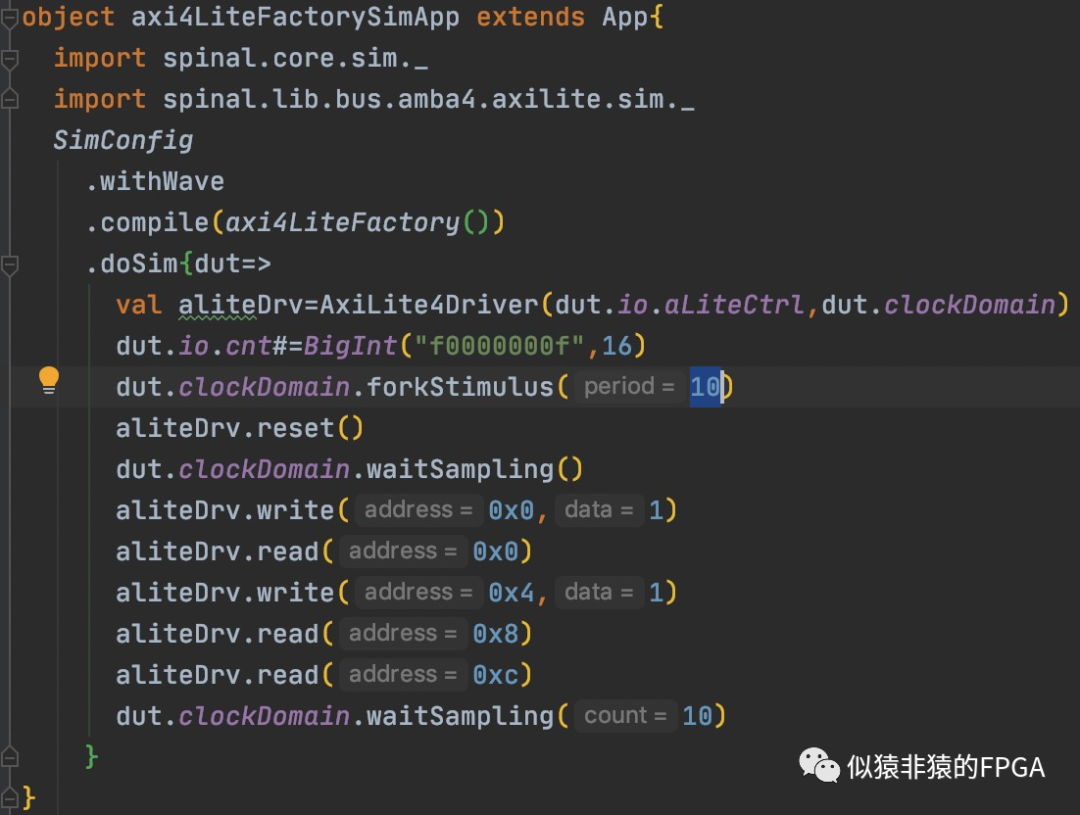

SpinalHDL里提供了AXI4-Lite总线的基础仿真库,这里直接调用其仿真库,完整的仿真代码如下:

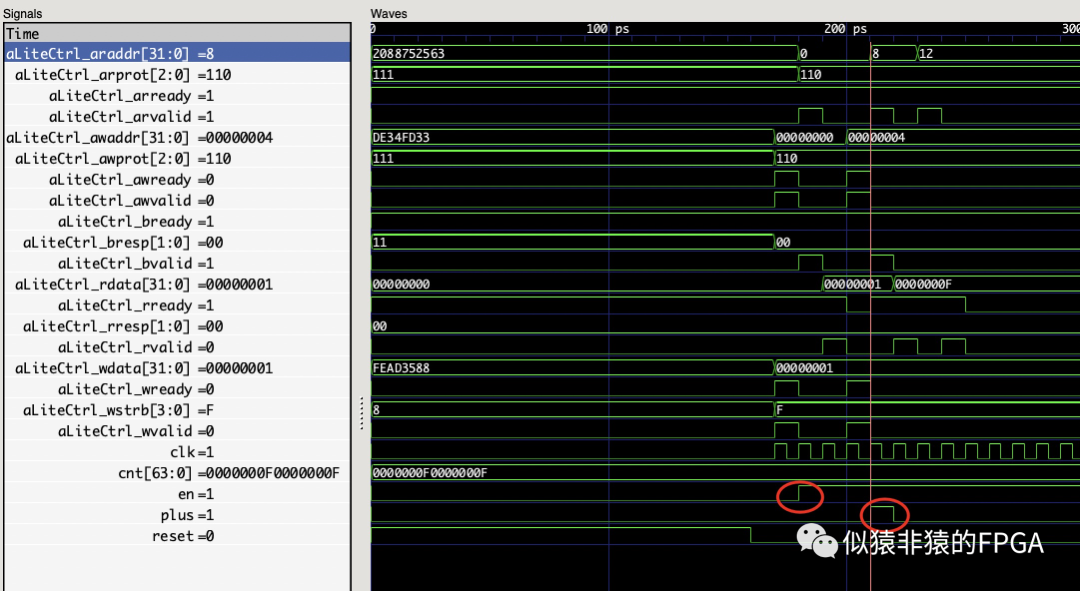

通过gtkWave观察波形:

可以看到,功能符合我们的设计,写寄存器0x4信号plus拉高1个时钟周期后自动清零。 这里简单几行代码实现了AXI4-Lite总线控制寄存器读写,对于我们在真正的项目实现里,能够极大简化我们的工作量和bug产生。尽管现在各个大厂或许有专门的总线控制寄存器读写代码生成工具,但SpinalHDL这种形式从本质上解决了Verilog描述的重复性工作。

写在最后

虽然SpinalHDL这种slave factory工具能够让我们在工程中快捷的实现想要的功能,但对于初学者来说,理解掌握AXI4-Lite这些标准的总线协议时序还是非常有必要的(Verilog or SpinalHDL实现都行喽)~

编辑:lyn

-

在SpinalHDL里实现优雅的添加待跟踪波形信号2022-06-22 0

-

看看在SpinalHDL的仿真中我们可以使用的后门读写操作2022-07-04 0

-

SpinalHDL将功能封装抽象成库函数供Stream总线接口快速调用2022-07-21 0

-

PC104对OV7670寄存器的读写2012-04-20 1532

-

寄存器与移位寄存器2016-05-20 1142

-

单片机实现寄存器寻址的方法解析2019-09-17 3373

-

如何在VHDL中实现一个简单的寄存器2022-07-29 4654

-

SpinalHDL中如何优雅地实现寄存器总线读写2022-08-05 1008

-

SpinalHDL的仿真中可以使用的后门读写操作2022-09-02 1069

-

解析CPU中的寄存器2022-09-19 4137

-

在SpinalHDL中如何快速地实现总线连接2022-11-28 862

-

RAL寄存器模型操作图鉴2023-05-17 938

-

RAL寄存器模型操作指南2023-07-12 1088

-

怎样通过改变寄存器中的内容实现对CPU的控制呢?2023-09-20 1353

-

如何根据自己设计中的寄存器配置总线定义来生成一套寄存器配置模版2024-03-04 1148

全部0条评论

快来发表一下你的评论吧 !