基于TMS320C6000系列DSP芯片实现高效信道化接收机的设计

电子说

描述

作者:张文旭,司锡才,孙强毅

在电子信息领域中,对于接收机的要求是处理的频带尽可能宽、动态范围尽可能大,以便得到更宽的频率搜索范围,获取更多的信息量,并且具有检测同时到达信号的能力[1]。随着电子元器件的不断发展,ADC的采样速率越来越高,这为接收机实现宽频带覆盖提供了硬件支持,而软件无线电中基于多相滤波结构的信道化接收又为实现全概率接收提供了理论依据[2]。

本文介绍一种基于多相滤波结构的高效信道化接收机,该接收机采用了美国国家半导体公司(National Semiconductor)的高速采样器件ADC08D1000与ALTERA公司的StratixII系列FPGA,可实现瞬时带宽480MHz的双通道信道化接收和瞬时带宽为960MHz的单通道信道化接收。另外,考虑到该信道化接收后续信号处理问题,采用了TI公司的TMS320C6000系列 DSP芯片完成后续信号处理算法。

1 高效信道化接收机结构模型

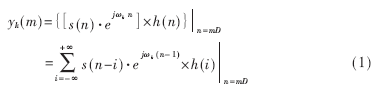

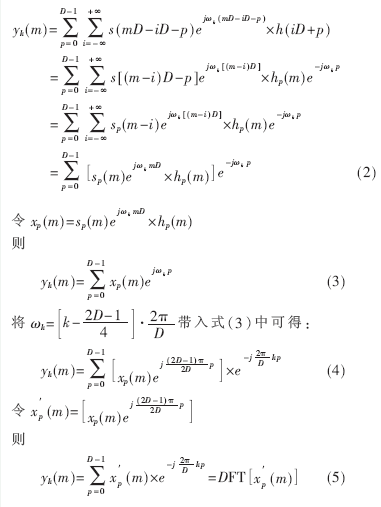

本文设计的信道化接收机结构模型采用多相滤波结构模型。假设输入信号为s(n),采用低通滤波器冲激响应为h(n),信道数为K,抽取比为D。采用临界抽取条件,即K=D情况下,可以由低通结构推导出多相滤波结构,即第K路信道的输出为[3]:

定义:信号D倍抽取后多相结构表达式为sp(m)=s(mD-p),滤波器的多相分量表达式为hp(m)=h(mD+p),用i=iD+p带入式(1)中,可得:

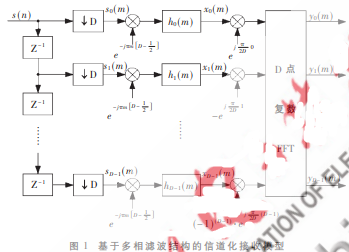

从上述推导和转换过程即可得到基于多相滤波结构的信道化接收模型,如图1所示。

从低通滤波结构到多相滤波结构的转换,可以看出该高效结构中抽取置于混频之前,可以将高速A/D 转换后的数据首先进行D倍抽取,然后再混频、滤波,使得混频器、滤波器工作速率降了D倍,且后续DFT处理可采用FFT实现,提高了系统的数据处理速度,充分发挥了该结构的高效性。

2 信道化接收机系统实现

2.1 系统硬件设计

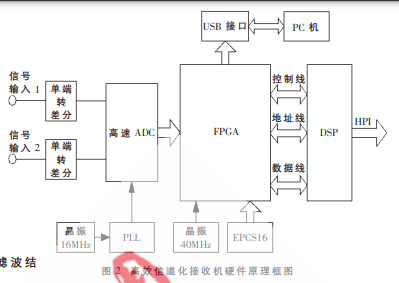

本文设计的高效信道化接收机的硬件原理框图如图2所示。由于该设计采用的高速A/D(ADC08D1000)内部集成了双通道模数转换功能,采样速率为 1GHz,所以当芯片工作于交叉采样模式时,只需将信号接于信号输入1端,信号输入2端悬空,即可实现采样速率为2GHz的采样。因此该接收机可实现瞬时带宽为480MHz的双通道数字信道化接收和瞬时带宽为960MHz的单通道数字信道化接收。

由于本设计高速A/D输出数据率在480MHz,因此高速A/D与FPGA接口采用差分信号走线,并且FPGA内部对数据率采取降速处理以便后续处理,解决了高速采样和后续信号处理之间的瓶颈问题。经过FPGA内部做信道化处理后的信号送入DSP中,可以实现后续相应的信号处理算法。另外,可通过USB接口芯片将所需数据传给PC机,完成数据的存储、处理与显示等。

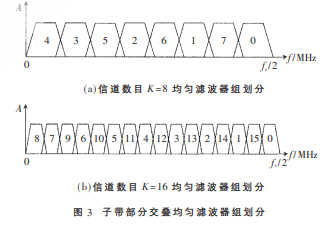

2.2 均匀滤波器组划分

基于多相滤波结构的信道化接收机模型,本系统设计中对于?棕k的选择按照其实信号多相结构选取为 系统实现的瞬时带宽为480MHz和960MHz两种,其各自的信道数目分别为K=8和K=6,各自均匀滤波器组划分情况如图3所示。图3(a)为瞬时带宽为480MHz,信道数目为K=8时的均匀滤波器组划分;图3(b)为瞬时带宽为960MHz,信道数目为K=16时的均匀滤波器组划分[5]。两种情况下均匀滤波器组划分均采用了子带部分交叠的划分形式,过渡带为5MHz。

系统实现的瞬时带宽为480MHz和960MHz两种,其各自的信道数目分别为K=8和K=6,各自均匀滤波器组划分情况如图3所示。图3(a)为瞬时带宽为480MHz,信道数目为K=8时的均匀滤波器组划分;图3(b)为瞬时带宽为960MHz,信道数目为K=16时的均匀滤波器组划分[5]。两种情况下均匀滤波器组划分均采用了子带部分交叠的划分形式,过渡带为5MHz。

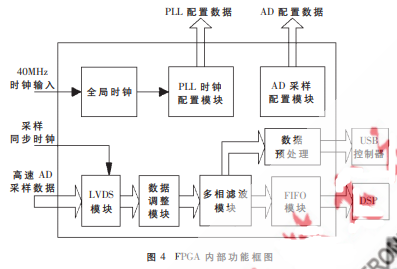

2.3 FPGA内部功能实现

该信道化接收系统FPGA内部功能主要包括系统全局时钟模块、PLL时钟配置模块、A/D采样配置模块、LVDS模块、数据调整模块以及FIFO模块。高速A/D采样得到的480MHz数据经过FPGA内部自带的LVDS模块,将2×16bit数据按照1:4分成2×64bit数据,相当于抽取比D=8,即输出数据率fout=fs/D=960MHz/8=120MHz,按照临界抽取条件,信道数目K=D=8,瞬时带宽为480MHz时,子带宽度B0=60MHz。实现单通道瞬时带宽960MHz的信道化结构时,信道数目和抽取比为K=D=16,子带宽度依然为B0=60MHz。经过LVDS输出的数据率为120MHz,送入数据调整模块后进行多相滤波结构的信道化处理,其处理结果通过高速FIFO与DSP完成数据传输。具体FPGA内部功能框图如图4所示。

3 实验测试结果

在完成了基于多相滤波结构的信道化接收机设计与调试的基础上,对该接收系统进行了实际测试。

3.1 对高速A/D数据采集的测试

输入信号频率为500MHz,信号形式分别为连续波和脉冲波,A/D采样速率为2GHz,利用FPGA自带的SignalTapⅡ嵌入式逻辑分析观察LVDS模块调整后的多路信号波形。测试结果如图5所示。

3.2 多相结构信道化测向情况测试

根据FPGA内部多相滤波结构的实现,其后续采用了CORDIC算法来实现瞬时幅度、瞬时相位的提取。实验中选择输入信号为100MHz的连续波信号,瞬时带宽为480MHz,采样速率为960MHz,利用DSP读取高速FIFO中的数据,借助CCS开发环境,将得到的数据以波形显示,如图6所示。其中 dsp_reg2为3表示信道3截获了信号,与图3(a)信道划分情况相符;而图形显示的是CORDIC算法输出的瞬时相位曲线。

3.3 截获信号频率测试情况

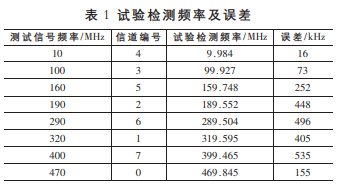

输入8个不同频率的余弦信号,检测系统截获信号的信道编号是否正确以及记录截获信号的频率。对照表1可知,系统输出的信道编号是正确的。由于信道化系统的采样时钟可能存在偏差和抖动,从而导致相位差测频算法测频出现偏差,即理论上各个信道中心频率与实际有一定的偏差,故试验检测频率与测试信号频率有一些偏差,但是已达性能指标要求。

本文介绍了一种基于多相滤波结构的高效信道化接收机的设计与实现。借助采样速率1GHz、集成双通道的高速A/D,该信道化接收机可以实现双通道瞬时带宽 480MHz和单通道瞬时带宽960MHz的宽频带覆盖。利用LVDS模块实现了高速数据的降速,并在FPGA内部实现了多相滤波结构的数字信道化接收,采用CORDIC算法实现了瞬时幅度和瞬时相位的提取,并通过实际测试验证了高速数据采集、均匀信道化接收和瞬时相位提取的正确性。该高效结构的信道化接收在FPGA内部实现,具有结构化设计灵活、方便的特点,且利用DSP可以实现后续的相关信号处理算法,适合工程应用。

责任编辑:gt

-

TMS320C6000系列DSP主机引导方式的实现2017-10-20 1068

-

急求TMS320C6000系列DSP的书2013-11-09 0

-

TMS320C6000系列DSP的CPU与外设2016-05-15 0

-

请问TMS320C6000系列dsp的未使用管脚如何处理?2019-01-14 0

-

TMS320C6000 系列DSP 的C 代码优化方法2009-05-15 525

-

TMs320C6000系列DSPs原理与应用2016-05-09 959

-

基于TMS320C6000系列DSP的Flash编程方法2017-10-19 914

-

基于TMS320C6000的优化策略分享2017-10-25 1144

-

TMS320C6000系列DSP优化介绍2018-04-17 1164

-

TMS320C6000芯片结构图和基本特性2018-09-07 17434

-

dsp tms320c6000基本作用的认识2018-09-07 9837

-

TMS320C6000 EMIF到TMS320C6000主机端口接口2024-10-26 87

-

TMS320C6000 DSP的复位威廉希尔官方网站2024-10-28 109

-

TMS320C6000 DSP关断逻辑和模式参考指南2024-12-17 42

-

TMS320C6000 DSP EMAC/MDIO模块参考指南2024-12-21 56

全部0条评论

快来发表一下你的评论吧 !