高压功率MOSFET寄生电容的形成

电子说

描述

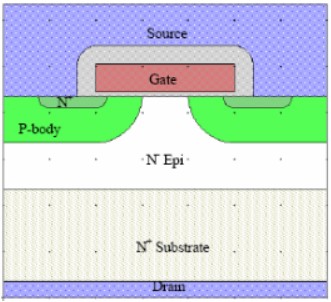

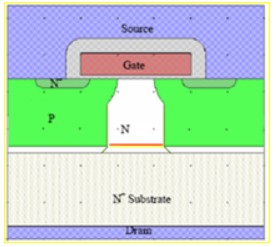

1 超结结构的高压功率MOSFET

功率MOSFET的输出电容Coss会随着外加电压VDS的变化而变化,表现出非线性的特性,超结结构的高压功率MOSFET采用横向电场的电荷平衡技术,如图1所示。相对于传统的平面结构,超结结构将P型体区下沉,这样在其内部形成P柱,和N区非常宽的接触面产生宽的耗尽层,也就是空间电荷区,空间电荷区形成的电场,也就是横向电场,保证器件的耐压;同时,原来N区漂移层就可以提高掺杂浓度,降低导通电阻。和标准MOSFET相比,横向电场电荷平衡技术可以极大的减小硅片尺寸,得到更低的RDSON和更低的电容。

(a) 平面结构

(b) 超结结构

图1 平面结构和超结结构的高压功率MOSFET

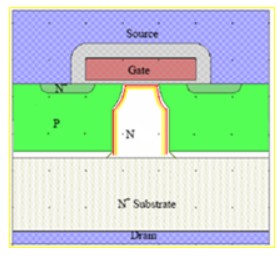

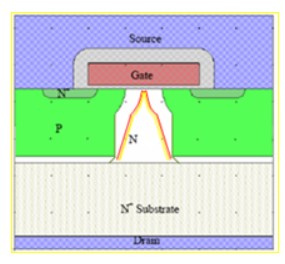

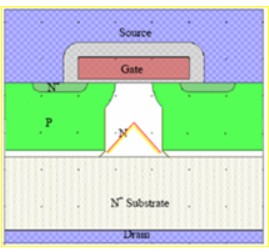

2 超结结构的高压功率MOSFET寄生电容形成

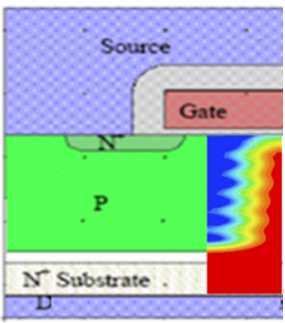

超结结构的功率MOSFET在VDS电压上升、横向电场建立产生耗尽层(空间电荷区)过程中,N型漂移层两侧的空间电荷区边界会向中心移动,如图2所示,随着VDS电压的升高,两侧空间电荷区边界会接触碰到一起,然后向再下继续移动。在这个过程中,直接影响输出电容Coss和反向传输电容Crss的主要参数有:漏极和源极、栅极和漏极相对的面积、形状、厚度,以及相应的空间电荷区相对的距离。

(a) VDS电压非常低

(b) VDS增加到电容突变电压

(c) VDS处于电容突变电压区

(d) VDS达到最大值

图2 空间电荷区建立过程

VDS电压低时,P柱结构周边的空间电荷区厚度相对较小,而且空间电荷区沿着P柱的截面发生转折,相对的有效面积很大,如图2(a)所示,因此输出电容Coss和反向传输电容Crss的电容值非常大;VDS电压提高,空间电荷区沿着P柱的截面发生下移,当VDS电压提高到某一个区间,两侧的空间电荷区相互接触时,同时整体下移,电容的有效面积急剧降低, 同时空间电荷区厚度也急剧增加,因此Coss和Crss电容在这个VDS电压区间也随之发生相应的突变,产生非常强烈的非线性特性,如图2(b) 和(c)所示;VDS电压提高到更高的值,整个N区全部耗尽变为空间电荷区空间,此时电容的有效面积降低到非常、非常小的最低时,如图2(d)所示,输出电容Coss也降低到非常、非常小的最低值。

在低电压时,相对于柱结构和单元尺寸,空间电荷区厚度相对较小,P柱结构周边,空间电荷区发生转折,导致输出电容的有效面积变大。这2种因素导致在低压时,Coss的值较大。VDS电压升高时,如VDS=20 V,VDS=100 V,从图3空间电荷区电场分布仿真图可以看到,

空间电荷区的形状开始变化,首先沿着补偿的结构经过波浪形的,然后进入更低有效面积的水平电容,因此高压的输出电容降低到2个数量级以下。

Crss和Coss相似,电容曲线的突变正好发生在上面二种状态过渡的转变的过程。

(a) 20 V空间电荷区电场分布

(b) 100 V空间电荷区电场分布

图3 空间电荷区电场分布

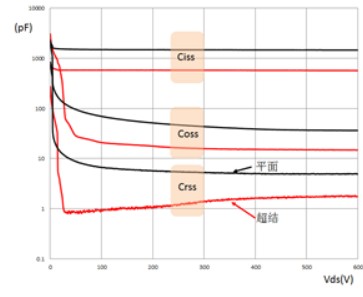

图4展示了平面和超结结构高压功率MOSFET的电容曲线,从图中的曲线可以的看到,当偏置电压VDS从0变化到高压时,输入电容Ciss没有很大的变化, Coss 和 Crss 在低压的时候非常大,在高压时变得非常小。在20~40 V的区间,产生急剧、非常大的变化。

图4 平面和超结结构高压功率MOSFET的电容

3 工艺对超结结构的高压功率MOSFET寄生电容影响

新一代超结技术进一步降低内部每个晶胞单元尺寸,对于同样的导通电阻,降低内部晶胞单元尺寸可以降低硅片的尺寸,从而进一步硅片的尺寸以及相关的寄生电容,器件就可以工作在更高频率,采用更小的封装尺寸,降低系统的成本。

内部的晶胞单元尺寸采用更小的尺寸,在更小的硅片面积实现以前的技术相同的或者更低的导通电阻,就必须要求漂移层N区电流路径的掺杂浓度更高,内部会产生更高的横向电场也就是更强烈的电荷平衡特性,保证内部空间电荷区获得所要求的击穿电压;同时,内部结构中每个柱状结构的高度对宽度的比值增加,上述的这些因素导致新一代技术的超结结构的高压功率MOSFET的Coss和Crss的电容曲线的突变电压区将降低到更低的电压,寄生电容的非线性特性更为剧烈。

不同的工艺,转折点的电压不一样,转折点的电压越低,电容的非线性特性越强烈,对功率MOSFET的开关特性以及对系统的EMI影响也越强烈。采用以前技术的超结结构的输出电容Coss非线性特性的VDS电压区间为40-60V,新一代的超结结构的输出电容Coss非线性特性的VDS电压区间为20~30 V。电容Crss和电容Coss的下降发生在更低的电压区间,这种效应在开关过程形成更快的开关速度,可以明显的降低开关损耗。Crss小,减小开关过程中电流和电压的交越时间。

另外,因为功率MOSFET在关断过程中,储存在输出电容Coss能量将会在每一个开关周期开通的过程中消耗在沟道中,新一代超结结构的功率MOSFET在高压时输出电容Coss降低得更低,Coss下降突变发生在更低的电压区,储存在输出电容Coss的能量Eoss等于输出电容对VDS电压在工作电压范围内的积分计算得到,因此,Eoss能量降低到更低的值,进一步的降低硬开关工作过程中的开关损耗,特别是在轻载的时候,Eoss产生的开关损耗的作用更加明显,可以极大提高系统轻载的效率。

然而,Coss和Crss这种效应在开关过程中,VDS电压经过这个电压区间,将会产生非常大的du/dt和di/dt,容易在驱动的栅极和漏极产生电压振荡,形成过高的VGS、VDS过电压尖峰,同时对系统EMI产生影响。

4 结论

1)超结结构的功率MOSFET内部P柱形成耗尽层及横向电场过程中,耗尽层空间电荷区的形状改变,导致影响输出电容的极板面积和距离发生剧烈的改变,输出电容具有强烈的非线性特性。

2)新一代超结技术采用更小晶胞单元尺寸,导致输出电容转折点电压进一步降低,对应的开关损耗减低,同时输出电容非线性特性进一步加剧。

3)输出电容非线性特性产生非常大的du/dt和di/dt,对系统EMI产生影响。

责任编辑:tzh

-

理解功率MOSFET的寄生电容2016-12-23 0

-

MOSFET寄生电容对LLC串联谐振威廉希尔官方网站 ZVS的影响2018-07-13 0

-

PCB布线设计时寄生电容的计算方法2009-09-30 27839

-

寄生电容,寄生电容是什么意思2010-03-23 2860

-

寄生电容产生的原因_寄生电容产生的危害2019-04-30 30282

-

什么是寄生电容_寄生电容的危害2020-09-17 31644

-

MOSFET寄生电容参数如何影响开关速度2021-01-08 17809

-

什么是寄生电容,什么是寄生电感2022-07-27 17615

-

MOSFET的寄生电容及其温度特性2023-02-09 3635

-

寄生电容对MOS管快速关断的影响2023-09-17 3276

-

SiC MOSFET 和Si MOSFET寄生电容在高频电源中的损耗对比2023-12-05 787

-

PCB寄生电容的影响 PCB寄生电容计算 PCB寄生电容怎么消除2024-01-18 3000

-

igbt功率管寄生电容怎么测量大小2024-08-07 843

-

普通探头和差分探头寄生电容对测试波形的影响2024-09-06 367

全部0条评论

快来发表一下你的评论吧 !