采用DSP和FPGA和上下变频器实现单载波调制解调系统的设计

描述

软件无线电(Software Radios)是一种新的无线电通信的体系结构。具体来说,软件无线电是以可编程的DSP或CPU为中心,将模块化、标准化的硬件单元用总线方式连接起来,构成通用的硬件平台,并通过软件加载来实现各种无线通信功能的开放式体系结构。

随着通信的发展,高速传输技术引起广泛的研究和注意。到目前为止,无线传输的速率受限于硬件条件。要实现高速传输,就必须结合各种芯片的特点,使硬件平台具有简单、通用的特点,因此需要开发一个通用平台。

DSP在控制和信号处理方面有优势,基带信号的调制、解调及FFT/IFFT等运算可以由DSP实现,但是在实时处理方面受到现有DSP处理速度和能力的制约。对于信号突发检测这种运算量大的处理,尤其是在高速传输时,通常要使用FPGA。FPGA特有的流水线设计结构可以使前后级在时间上并发,达到高效、高速。为了减小DSP在信号处理上的压力,同时满足高速要求,采用专用数字变频芯片来实现数字上下变频。

为了和软件无线电的思想统一,在系统设计时考虑兼容单载波调制解调方式,采用DSP、FPGA、上下变频器的方案,不使用专用调制解调芯片。

1 OFDM原理和基带信号模

正交频分复用[1]OFDM(Orthogonal Frequency Division Multiplex)是一种多载波调制方式,通过减小和消除码间串扰的影响来克服信道的频率选择性衰落。它的基本原理是将信号分割为N个子信号,然后用N个子信号分别调制N个相互正交的子载波。由于子载波的频谱相互重叠,因而可以得到较高的频谱效率。近几年OFDM在无线通信领域得到了广泛的应用。

当调制信号通过无线信道到达接收端时,由于信道多径效应带来的码间串扰的作用,子载波之间不再保持良好的正交状态,因而发送前需要在码元间插入保护间隔。如果保护间隔大于最大时延扩展,则所有时延小于保护间隔的多径信号将不会延伸到下一个码元期间,从而有效地消除了码间串扰。当采用单载波调制时,为减小ISI的影响,需要采用多级均衡器,这会遇到收敛和复杂性高等问题。

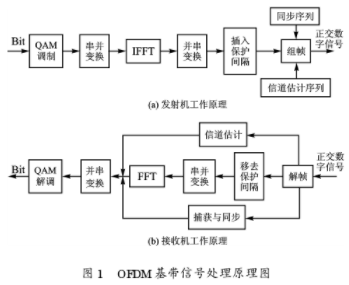

图1是OFDM基带信号处理原理图。其中,图1(a)是发射机工作原理,图1(b)是接收机工作原理。

在发射端,首先对比特流进行QAM或QPSK调制,然后依次经过串并变换和IFFT变换,再将并行数据转化为串行数据,加上保护间隔(又称“循环前缀”),形成OFDM码元。在组帧时,须加入同步序列和信道估计序列,以便接收端进行突发检测、同步和信道估计,最后输出正交的基带信号。

当接收机检测到信号到达时,首先进行同步和信道估计。当完成时间同步、小数倍频偏估计和纠正后,经过FFT变换,进行整数倍频偏估计和纠正,此时得到的数据是QAM或QPSK的已调数据。对该数据进行相应的解调,就可得到比特流。

这里仅讨论软件功能模块,具体算法不在此涉及。

2 硬件结构

OFDM调制解调与常规调制解调相比,所需的运算量大,尤其是当系统选用的子载波个数多时,仅在发射端的IFFT变换和接收端的FFT变换所需的时间就很长。通常使用FPGA和高速的DSP解决该问题。由于在接收端还要完成信号突发检测、同步和频偏校正等数字信号处理,所以接收端对实时性要求更高。在该系统中,使用FPGA完成信号的突发检测和定时,DSP完成FFT/IFFT变换和QAM/QPSK调制解调

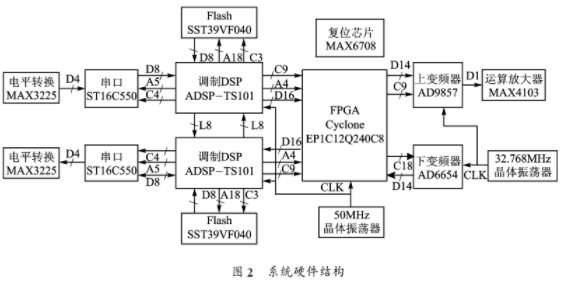

本系统主要由4部分组成: DSP、FPGA、正交数字上变频器(Quadrature Digital Upconverter)、正交数字下变频器(Quadrature Digital Downconverter)。系统硬件结构如图2所示。图中,D表示数据总线,A表示地址总线,C表示控制总线, L表示链路口数据线, 字母后面的数字表示总线的位数。50 MHz晶振为两片DSP及FPGA提供时钟信号,32.768 MHz高稳定度晶振为AD9857和AD6654提供高质量的时钟信号。复位芯片MAX6708控制DSP、FPGA、AD9857、AD6654和ST16C550的复位。

DSP完成QAM或QPSK的调制解调和FFT/IFFT变换。系统所使用的DSP[2]是ADI公司的Tiger sharc TS101。该DSP具有以下特性: 最高工作频率为300 MHz,3.3 ns指令周期;6 MB片内SRAM;2个计算模块,每个模块都有1个ALU、1个乘法器、1个移位寄存器和1个寄存器组;2个整型ALU,用来提供寻址和指针操作;14个DMA控制器;1149.1 IEEE JTAG口。对于OFDM基带处理,该DSP最大的特点是: 进行256点的复数FFT变换,仅需3.67 μs。

正交数字上变频器采用ADI公司的AD9857。AD9857[34]最高工作频率为200 MHz,输出中频频率范围为0“80 MHz;内部集成半带滤波器、CIC(Cascaded Integrator Comb)滤波器, 反SINC滤波器和高速的14位数/模转换器,其核心是一个相位连续的直接数字频率合成器DDS (Direct Digital Synthesizer)。在该方案中,AD9857工作在正交调制模式,其32位频率控制字使输出频率的最高精确度为:SYSCLK(系统时钟)除以232。

正交数字下变频器采用ADI公司的AD6654。AD6654[5]内部集成了一个14位、92.16 Msps的模/数转换器和4/6通道的数字下变频器。每个通道可独立配置。数字下变频内部集成了频率变换器、可编程级联梳状滤波器(CIC)、2个滤波器组和数字自动增益控制。其中: 频率变换是通过32位数控振荡器实现的;CIC实现1”32倍的抽取;2个滤波器组包括FIR滤波器和2倍抽取的半带滤波器。输入的中频模拟信号经过ADC和频率变换后,使用滤波器组进行滤波和抽取,最后并行输出正交基带数字信号。输入中频信号频率最高可到200 MHz,此时,使用欠采样技术。

3 参数设计及调制

信号波形作者采用PCB八层板设计,实现了该系统的硬件平台,并在此平台基础上实现了高速OFDM传输和常规单载波调制解调,形成了一个通用宽带高速调制解调平台。设计的目的是要在该平台上实现现有的全部物理层的算法,特别是实现实时OFDM传输系统。对OFDM系统提出的指标要求如表1所列。

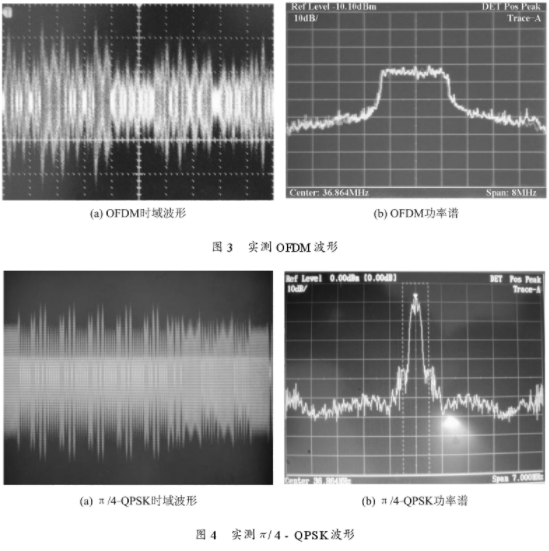

图3给出了32路子载波OFDM在上述参数设计下的已调信号波形(见图3(a))及其功率谱(见图3(b))。图中子载波调制方式为QPSK,码元频率为中频频率36.864 MHz,带宽是2.048 MHz。图4给出了一种单载波调制制式(以π/4QPSK为例)的时域波形(见图4(a))及其功率谱(见图4(b))。另外,数字调制方式的码元频率可达2 MHz(即对于四相调制,比特速率可达4 Mbps;对于32QAM调制,比特速率可达10 Mbps),且子载波调制方式、比特(或码元)速率、输出中频均可调。

图4 实测π/4-QPSK波形

4 结论

本文所提出的方案有以下特点:

① 基于双DSP的结构,可工作在双工方式,同时完成信号的发射和接收;工作在TDMA方式下或半双工时,DSP可通过Link口进行高速通信,有利于并行处理,以提高传输速率。DSP利于基带信号的实时处理,可以实现高速调制解调。

② 变频器具有频率分辨率高、频率变化速度快、相位连续、易于数字控制等特点。采用DSP和变频器的方案,不仅可以实现模拟调制解调,而且可以实现各种数字调制解调,兼容传统调制解调和新型调制解调方式。

③ 在DSP和变频器之间使用FPGA,实现突发信号的同步捕获,可以分担DSP的部分任务,从而提高系统的实时性。

责任编辑:gt

-

基于FPGA的AM调制解调,调制采用ROM+任意载波频率,解调采用FIR奔跑的小鑫 2022-09-26

-

如何实现多天线多载波的数字上下变频的FPGA?2019-08-09 0

-

多天线多载波的数字上下变频的FPGA实现方法有哪些?2019-09-25 0

-

使用一个FPGA便可实现的64通道下变频器2010-01-18 1264

-

基于FPGA的数字下变频器的设计与实现2017-11-22 6210

-

多天线多载波的数字上下变频的FPGA实现2017-11-25 459

-

基于专用数字下变频芯片GC5016的宽/窄带数据下变频系统设计及数据分析与解调2017-12-05 3390

-

介绍多天线多载波数字上下变频的FPGA实现方法2019-03-13 2091

-

ADI ADMV1014 24-44GHz宽带微波下变频器解决方案2019-04-05 2375

-

基于ADMV101424的宽带微波下变频器设计2019-04-13 1862

-

使用FPGA实现数字下变频器DDC的设计资料合集免费下载2020-08-10 827

-

基于FPGA的数字下变频器(DDC)的设计2021-09-16 1158

-

ADMV1014是一款采用硅锗(SiGe)设计的宽带、微波下变频器2022-11-14 652

-

上下变频器的原理和作用2024-08-25 1835

-

上下变频器如何测试2024-10-03 420

全部0条评论

快来发表一下你的评论吧 !