使用清洗溶液实现蚀刻后残留物的完全去除

使用清洗溶液实现蚀刻后残留物的完全去除

电子说

描述

引言

我们华林科纳半导体开发了一种新的湿法清洗配方方法,其锡蚀刻速率在室温下超过30/min,在50°c下超过100/min。该化学品与铜和低k材料兼容,适用于铜双镶嵌互连28 nm和更小的技术节点应用。该化学品提供了在单晶片工具应用的清洗过程中原位控制锡拉回或者甚至完全去除锡掩模的途径。这些化学品不含NH4OH或TMAH,因此非常方便用户使用。

介绍

等离子干法蚀刻工艺通常用于制造铜(Cu) /低k双镶嵌器件的垂直侧壁沟槽和各向异性互连通孔。随着技术节点发展到45纳米和更小,半导体器件尺寸的减小使得实现过孔和沟槽的关键轮廓控制更具挑战性。IC公司正在研究使用金属硬掩模来提高对低k材料的蚀刻选择性,从而获得更好的轮廓控制。为了获得高产量和低电阻的互连,在下一个工艺步骤之前,必须去除侧壁上的聚合物和在蚀刻过程中产生的通孔底部的颗粒/聚合物残留物。如果清洗溶液还能够蚀刻TiN硬掩模以形成拉回/圆角形态,这将是有益的。这将防止低k值的弯曲或硬掩模的底切,使得能够可靠地沉积阻挡金属、铜籽晶层和铜填充。将这一概念更进一步,通过消除对阻挡层CMP的需要,完全去除金属硬掩模可以为下游工艺,特别是CMP提供许多好处。为了实现这两个目标,清洗溶液必须与低k和Cu相容,同时能够去除所有蚀刻副产物和残留物。

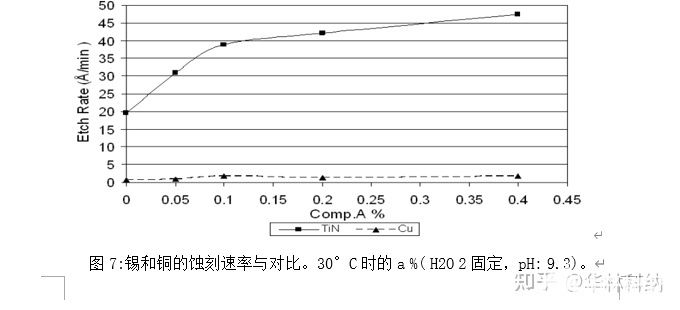

已经探索了许多去除这些蚀刻残留物的方法。使用氢氧化铵-过氧化氢-水混合物和四甲基氢氧化铵(TMAH) -过氧化氢-水混合物进行锡蚀刻的研究已经进行。还报道了锡对铜的蚀刻速率选择性小于10。需要高于10的选择性来实现锡拉回/圆角方案,同时保持与Cu的兼容性。在本文中,我们报告了最近开发的一种新的湿法清洗配方方法。通过在我们的配方中加入新的铜腐蚀抑制剂和新的锡蚀刻增强化学品(本文中称为“化合物A”),我们能够实现(高的锡/铜蚀刻速率选择性,完全除去蚀刻残余物,与低k和铜的相容性,调节性能以提供锡拉回/圆角或完全除去锡的能力,以及适用于单晶片工具应用。

结果和讨论

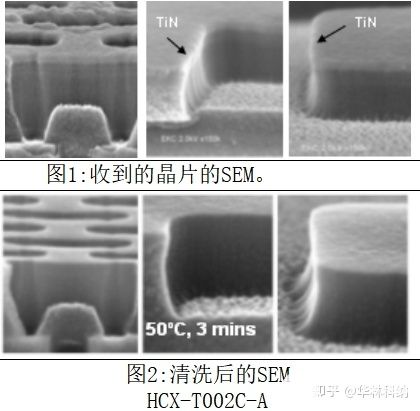

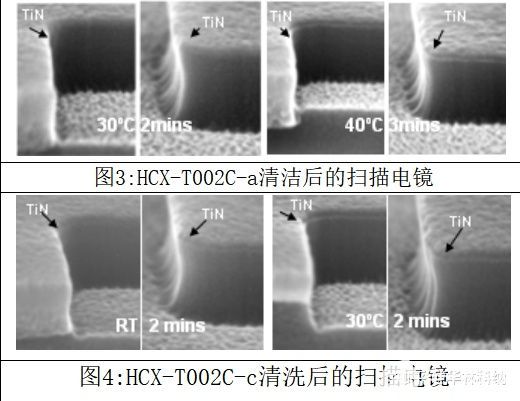

图1示出了在使用锡蚀刻掩模进行干法蚀刻后具有残留物的晶片。图2显示了在50℃下用HCX-T002C- A处理2分钟后,蚀刻残留物和锡蚀刻掩模的完全去除。如表1所示,锡蚀刻速率随着工艺温度的升高而增加。图中显示了HCX-T002C-A分别在30和40℃下2分钟的锡回拉

3. 随着锡蚀刻速率的增加(通过将工艺温度从30℃增加到40℃),锡掩模的拉回变得更加明显。对于HCX-T002C-C,在图4中可以看到相同的锡拉回形态;锡拉回在30°C时比在室温时更显著。表1强调了HCX-T002C对低k和TEOS电介质的低影响。

引言

已经成功开发了一系列配方,这些配方在铜和低介电常数上具有高选择性地去除锡,并在Fab中进行了全面测试。化合物A已经显示出与H2O2一起提高锡蚀刻速率。通过引入新型铜腐蚀抑制剂,可以防止H2O2对铜的氧化和随后的腐蚀。对于给定的配方组分子集,已经证明可以通过pH和/或工艺条件进一步控制和调节锡和铜之间的蚀刻速率选择性,同时仍然能够保持与铜和低k的完全相容性。使用这些清洗溶液还实现了蚀刻后残留物的完全去除。其中一种配方已经通过了一家大型IC制造厂的28纳米节点制造认证。重要的是,这些配方还提供了一种在清洗过程中控制拉回甚至完全原位去除锡掩模的途径。这进而在随后的金属沉积过程中提供了潜在的好处,并且消除了对阻挡层CMP和随后的后CMP清洗步骤的需要,从而提高了总的器件制造产量。

审核编辑:汤梓红

-

【已解决】FPGA的TQFP封装焊接后引脚间留有白色松香残留物...2013-03-20 0

-

U1252A交流电压残留物2018-11-15 0

-

使用湿化学物质去除光刻胶和残留物2022-03-24 1247

-

金属蚀刻残留物对对等离子体成分和均匀性的影响2022-05-05 1004

-

多晶硅蚀刻残留物的的形成机理2022-05-06 1364

-

22nm互连的光刻蚀刻后残留去除的挑战和新方法2022-05-31 3631

-

刻蚀后残留物的去除方法2022-06-09 3110

-

BEOL应用中去除蚀刻后残留物的不同湿法清洗方法2022-06-14 1832

-

适用于清洁蚀刻后残留物的定制化学成分(1)2022-06-23 1322

-

蚀刻后残留物和光刻胶的去除方法2022-07-04 9305

-

使用稀释的HCN水溶液的碳化硅清洗方法2022-09-08 2158

-

PCBA残留物的影响及清洗,助焊剂残留物怎么样清除2023-09-22 3316

-

焊后锡膏残留物带来的危害有哪些?2023-07-25 1479

-

锡膏焊接后残留物如何清洗?2024-09-20 903

-

芯片湿法刻蚀残留物去除方法2024-12-26 98

全部0条评论

快来发表一下你的评论吧 !