FPGA中实现对数运算的方法

描述

FPGA中实现对数运算主要有三种方法:

(1)在外部直接算好对数值,按照数值范围做个表,存在ram里,到时候查表。为了减少表深度,提高资源利用率,可以考虑去掉部分低位数值,损失一定的精度。

(2)使用cordic算法求解对数。

(3)log10(x)=ln(x) * log10(e) , log10(e)是常数可以手动先计算好,用IP Core的话多个乘法器。

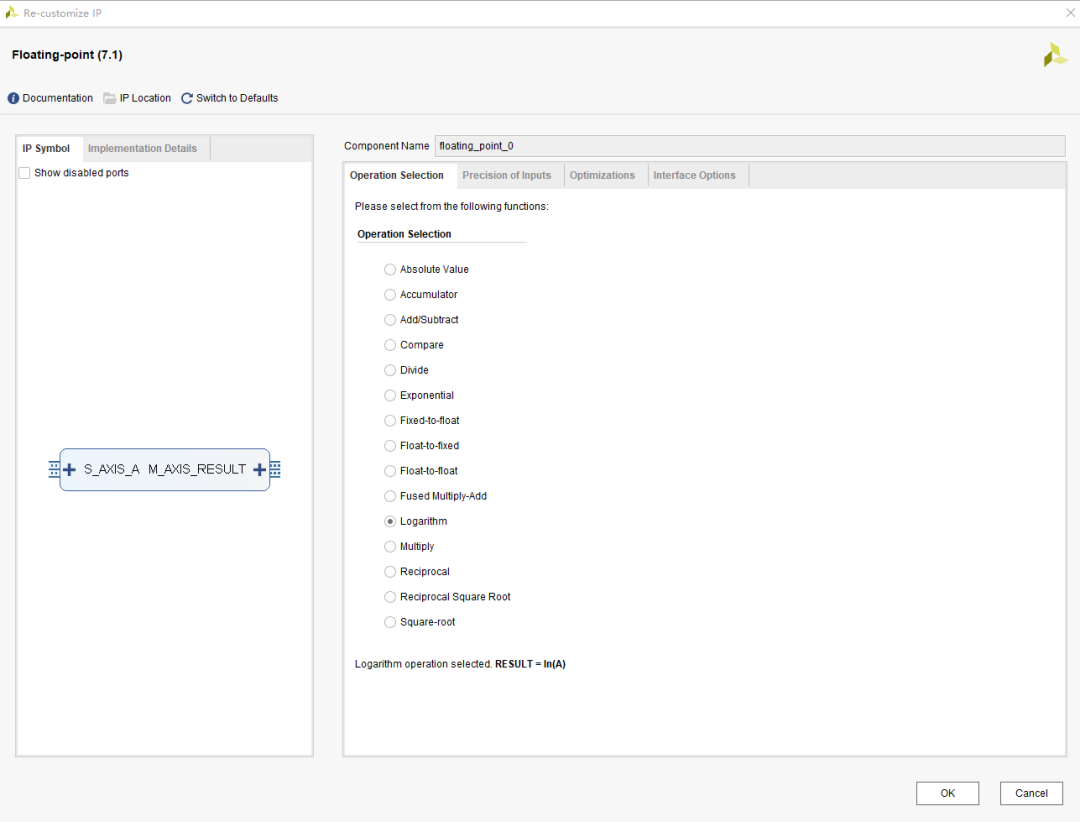

下面介绍使用IP核floating-point来计算对数,该IP计算对数时,计算的是Ln(A)(A是输入),如下图所示:

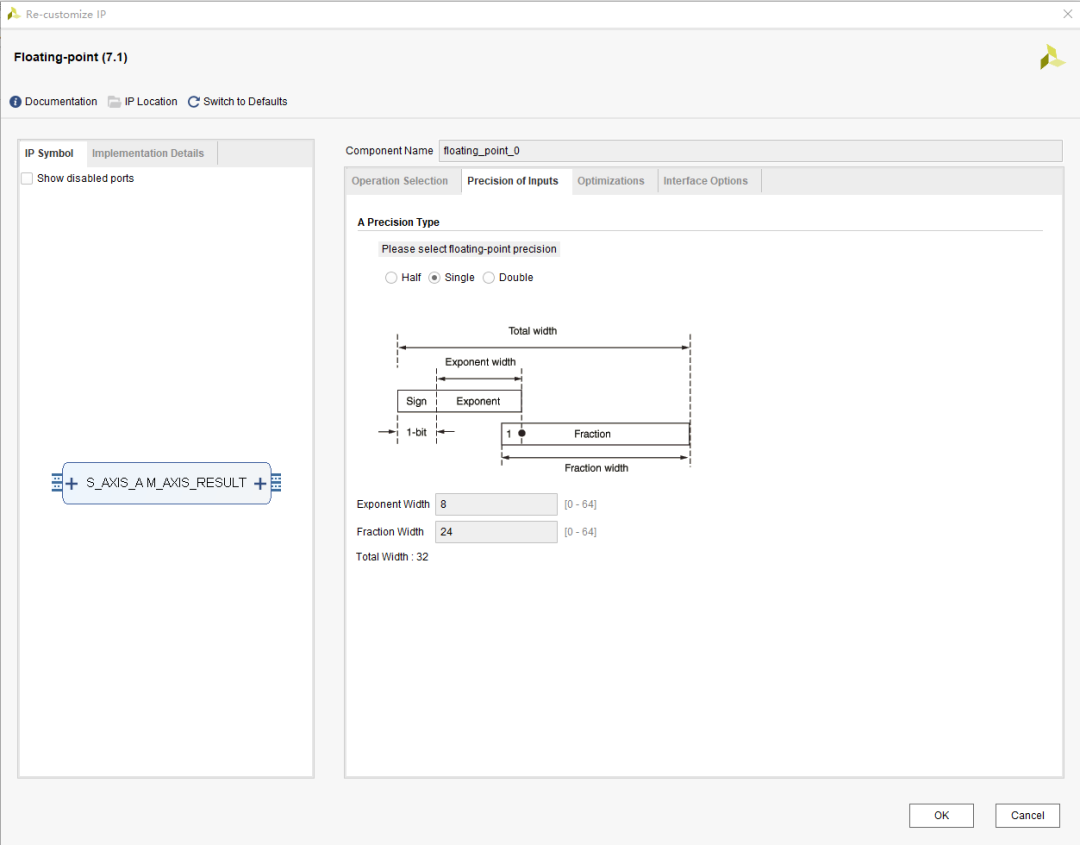

输入是浮点数,所以如果我们在FPGA内使用的定点数,则需要先将定点数转化为浮点数:

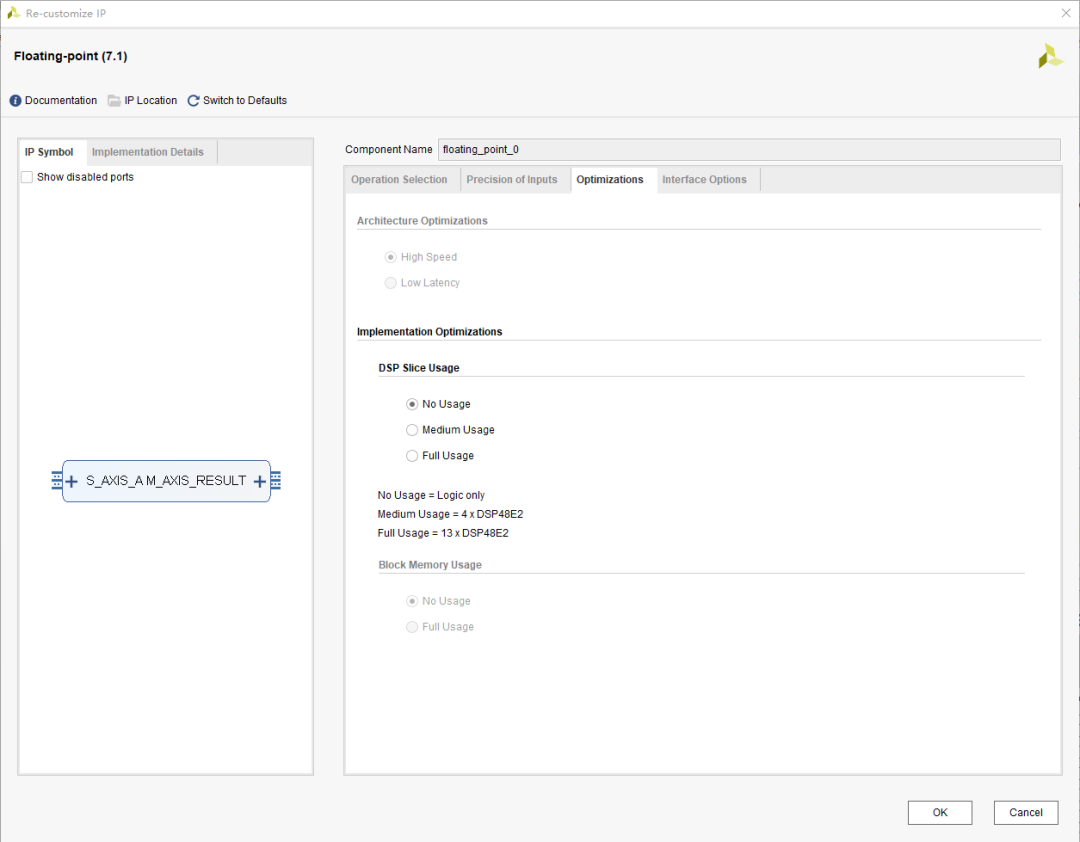

实现对数运算时,可以使用DSP核心,也可以不用,IP配置中提供了三个等级:

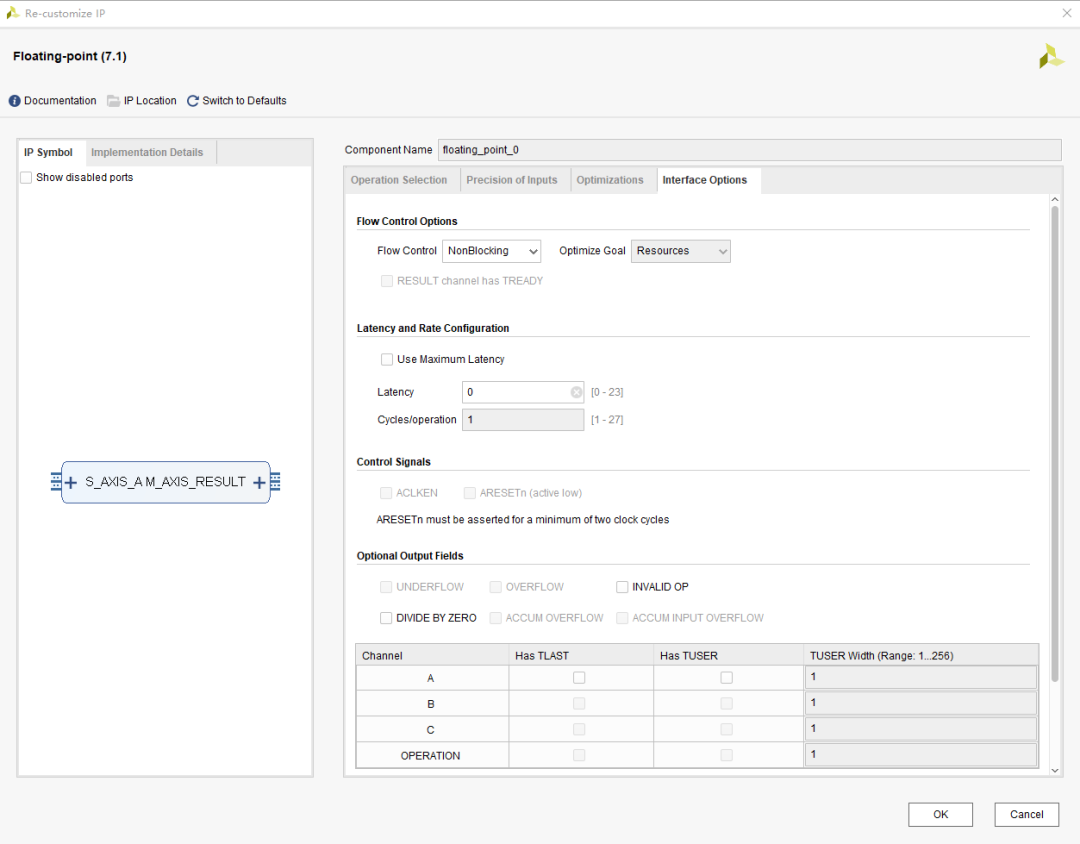

对于Flow Control可以选择带缓存的Blocking模式,也可以选择没有缓存的NonBlocking模式,延时也可以选择从0到23:

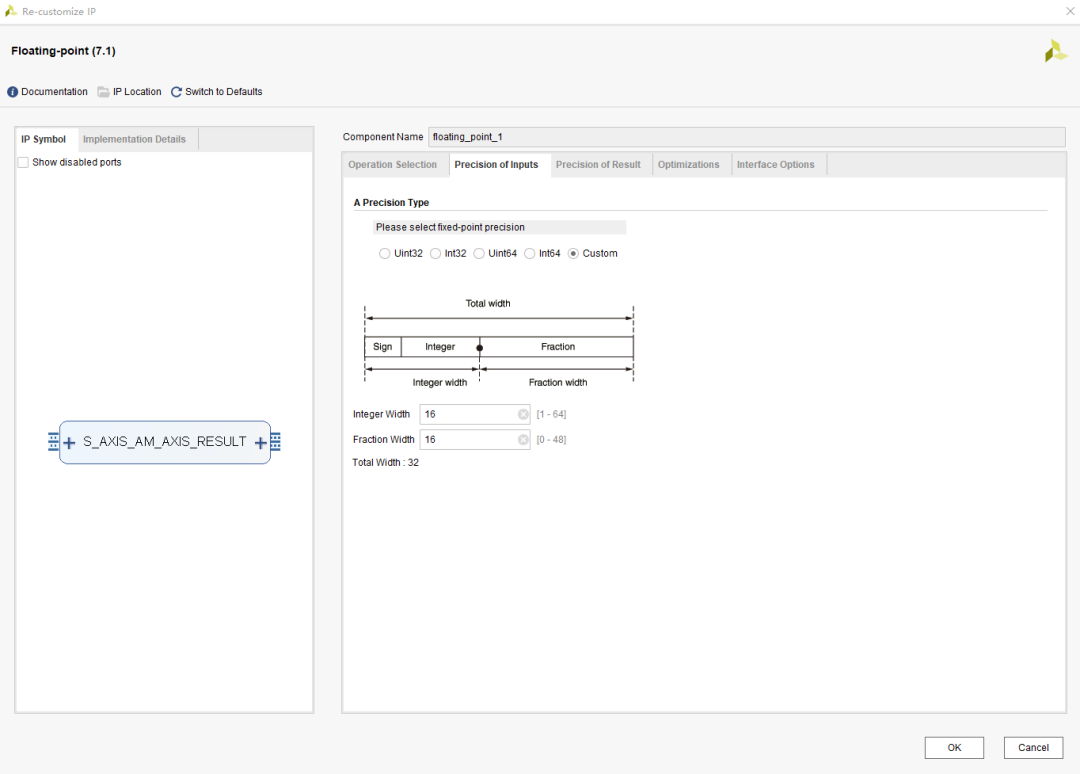

上面也提到,计算LOG的输入是浮点数,如果需要,可以继续使用floating-point来实现定点数转浮点数,对于转换IP的输入可以自主设定如下图所示,这里设为int16+fra16,输出为单精度浮点数,可以直接给计算LOG的IP核:

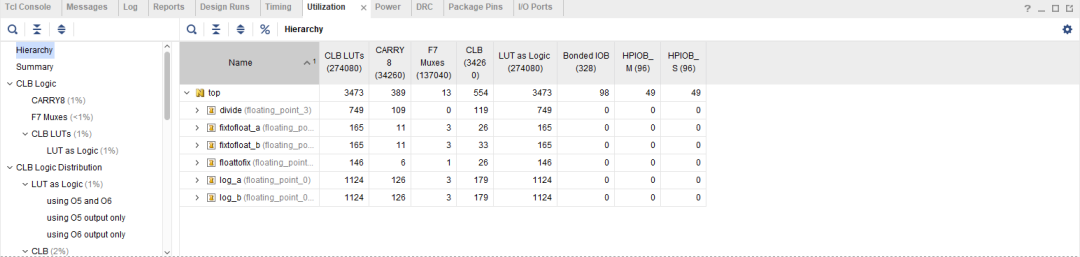

我们要计算以任意数为底的对数时,可以通过来计算,由此完成一次计算,需要两个定点转浮点的IP(fixtofloat),两个LOG的IP(log不使用DSP),以及一个除法IP(divide),最后再将浮点数转为定点数输出,综合实现后的资源占用情况为:

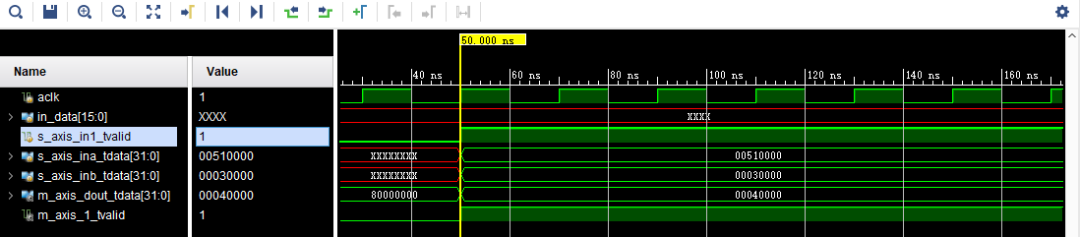

一次简单的RTL仿真为:

原文标题:FPGA中实现对数运算

文章出处:【微信公众号:FPGA设计william hill官网 】欢迎添加关注!文章转载请注明出处。

-

基于verilog HDL的高速对数运算模块设计2016-03-10 0

-

对数函数的FPGA怎么实现2019-03-08 0

-

为什么研究浮点加法运算,对FPGA实现方法很有必要?2019-07-05 0

-

乘除法和开方运算的FPGA串行实现2010-07-28 796

-

对数和指数运算威廉希尔官方网站2008-01-17 16982

-

基本对数运算威廉希尔官方网站2010-04-23 2612

-

乘法器对数运算威廉希尔官方网站 应用2010-04-24 2559

-

除法器对数运算威廉希尔官方网站 的应用2010-04-24 2710

-

基于FPGA的开方运算实现2015-10-30 671

-

如何使用FPGA实现开方运算2020-08-06 1799

-

如何才能在FPGA上实现对数函数2020-08-07 1477

-

FPGA中浮点运算定标实现方法2021-08-12 4846

-

如何实现FPGA中的除法运算2022-04-27 7423

-

fpga实现加法和减法运算的方法是什么2023-08-05 1466

-

FPGA中浮点四则运算的实现过程2024-11-16 441

全部0条评论

快来发表一下你的评论吧 !