放心交给AI解决的芯片设计痛点

电子说

1.3w人已加入

描述

电子发烧友网报道(文/周凯扬)尽管制造工艺的推进速度已经放缓,芯片设计的复杂程度依然丝毫不减,对于芯片设计者来说,在这样一个AI驱动的时代下,如果不能将AI为自己所用,无疑会让自己乃至整个设计项目的效率停滞不前。虽说大家都已经察觉到AI开始渗透进EDA工具中,那么现阶段的AI,究竟能解决哪些设计上的挑战呢?

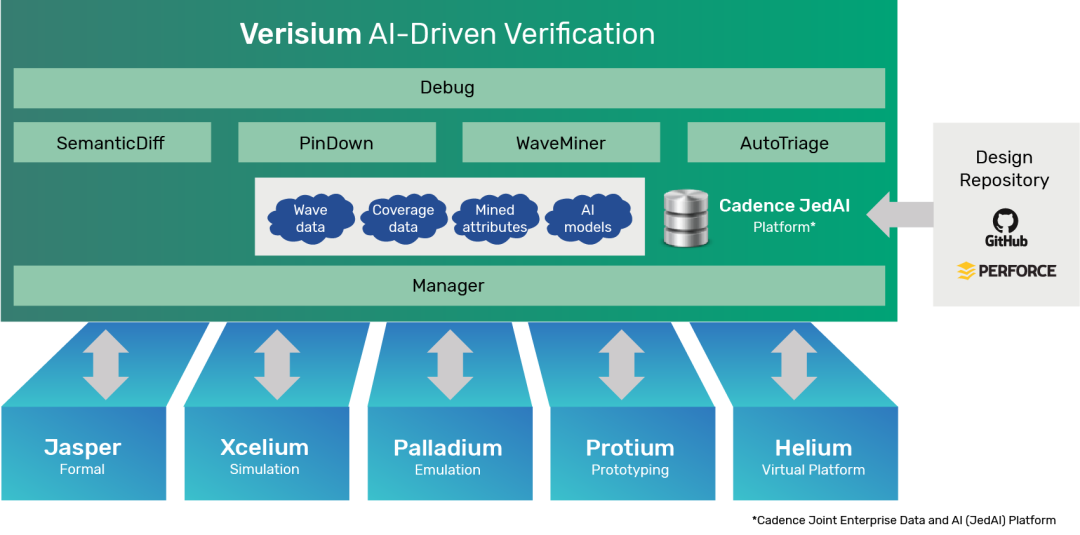

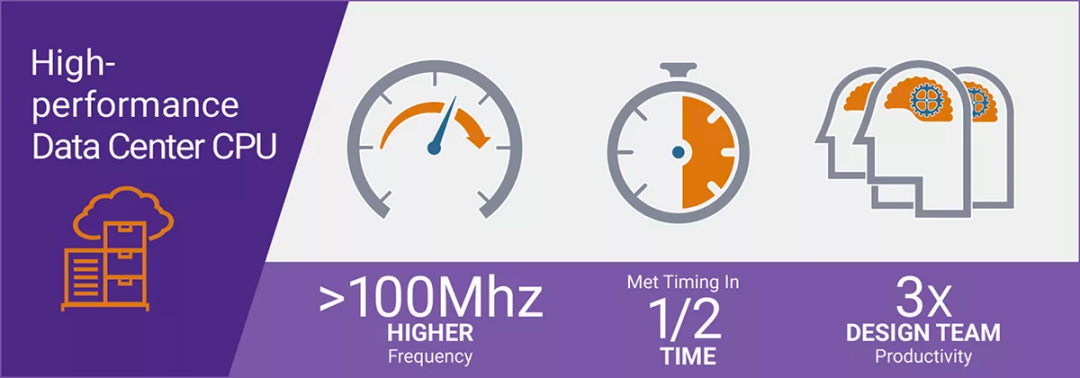

验证

验证是芯片设计中最大的挑战之一,我们已经见识过了价格高昂的专用验证硬件,以及验证上云的潮流,这些都足以说明验证是芯片设计中一个多么耗费资源的过程,这里指代的也不仅仅是硬件计算资源,还有时间资源。验证所耗时间甚至可能高过其他流程,这些年诸多芯片开发团队中的验证工程师人数也在逐渐增长,增速甚至已经超过了设计工程师,然而业内却很少有人去优化验证这个流程。

模拟设计自动化

相对数字IC设计来说,模拟IC的设计显然在自动化程度上还是差了不少的。在数字威廉希尔官方网站 的设计过程中,整个流程的自由度是在逐级降低的。模拟威廉希尔官方网站 设计虽然也是如此,但其下降幅度还是不比数字威廉希尔官方网站 设计的,尤其是在布局布线和验证上,所以自动化一直没有提上日程,现阶段大部分模拟威廉希尔官方网站 设计主要还是取决于设计者本身的直觉、技能和经验。有了AI的帮助后,EDA工具在大量数据的训练下给出了先进的机器学习算法,使得模拟威廉希尔官方网站 的布局布线有了更高效的自动化流程,尤其是在约束提取和生成,布局优化上,模拟威廉希尔官方网站 的优化和生成及仿真验证也可以在AI驱动下获得提速。如此一来,每个模拟威廉希尔官方网站 设计的迭代数量会进一步减少,芯片的上市周期也随之缩短。系统集成

近几年流行起来的UCIe、Chiplet、3D封装等,其实都是一个系统集成的概念。以此引入的设计与制造优化方案也受到了持续关注,比如DTCO等。如何集成更多的晶体管、更多的内存以及逻辑+内存集成,还有最后软件联合硬件的热管理等,都是系统集成需要考虑的问题。

写在最后

其实一旦芯片设计进入AI辅助的时代,也对设计工程师们提出了相应的更高要求,因为不少低级设计问题已经被AI预测、优化和生成给解决了。设计工程师们需要在更高层级的设计上实现创新,比如系统/软件联合优化等等,这样自己才不会被“优化”掉。设计工程师们的专业技能,未来也会更加趋向于数据科学家需要掌握的技能,而数据科学家们也说不定会因此获得抢设计工程师饭碗的机会。

更多热点文章阅读

- 董明珠:格力为特斯拉供应底盘装备,白电企业对“造车”达成共识?

- 俄罗斯生产首颗纯国产通信卫星!俄卫星实力有多强?

- 欧盟统一充电接口!苹果:确定改用USB-C!

- Marvell大幅裁撤中国研发团队,但另一市场正加大在华投资

- 警惕!德州仪器:芯片需求疲软,正从消费电子蔓延至工业领域!

原文标题:放心交给AI解决的芯片设计痛点

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 电子发烧友网

-

硅光芯片的优势/市场定位及行业痛点2020-11-04 0

-

解决芯片工程师的两大痛点2018-11-07 3206

-

爱立信发布全新“原生AI”设计 拟借助AI解决运营商痛点问题2020-03-26 448

-

AI+视频监控+存在什么痛点2020-03-27 1686

-

Gravitylink推出钛灵AI市场,深入解决行业痛点,加速AI落地应用2020-06-11 1096

-

智慧穿戴,从芯启航 | 邀您见证超低功耗AI芯片的诞生!2020-07-21 8780

-

直面AI痛点 博观智能重磅发布博观全景AI “1+2”战略2020-12-04 1968

-

放心交给AI解决的芯片设计痛点2022-11-08 1392

-

传感器技术与日俱进,低功耗AI芯片成为背后功臣2023-02-23 4697

-

放心出门,安全交给华为智能门锁2023-04-07 809

全部0条评论

快来发表一下你的评论吧 !