摩尔定律在工艺复杂度和经济高成本双重压力下步履蹒跚,伴随疫情的全球形势变化又给整个半导体行业供应链带来巨大的压力。在技术和环境的双重限制下,3D-IC从发明之初锦上添花的技术晋身显学,被无数企业视作在现有环境下提高系统集成度和全系统性能的必不可少的解决方案。

不知不觉间,行业文章和会议开始言必称chiplet —— 就像曾经的言必称AI一样。这种热度对于3D-IC的从业人员,无论是3D-IC制造、EDA、还是3D-IC设计,都是好事。但在我们相信3D-IC之路是Do Right Things的同时,如何Do Things Right也愈发重要。

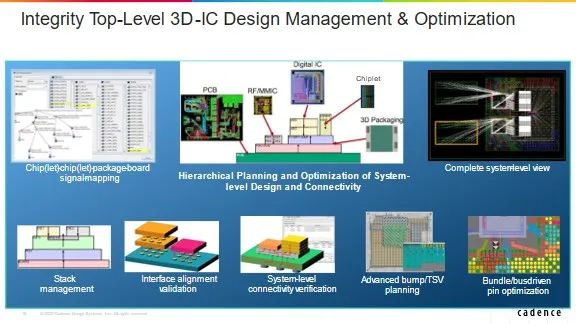

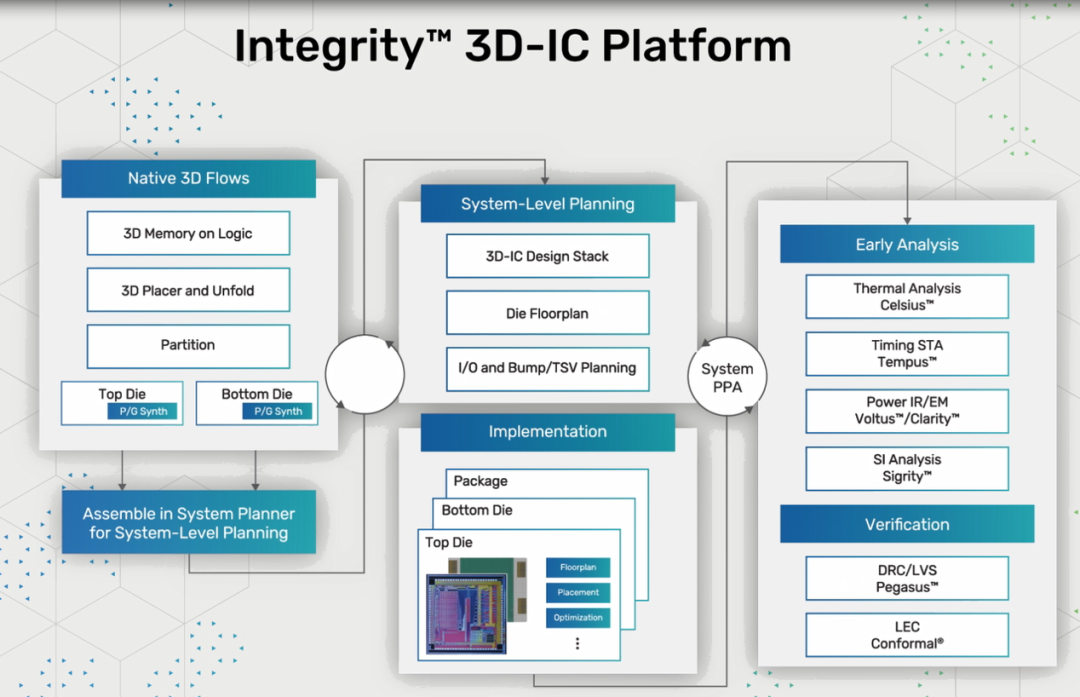

Cadence在3D-IC道路上已经探索了很多年,全新Integrity 3D-IC平台的研发基于十几年的探索、先进客户的使用经验、和先进制程流片封装经验,在2019年正式启动,如今已经拥有包括3D-IC系统顶层规划、堆叠设计、中介层绕线、自底向上、自顶向下、MoL近存运算、LoL逻辑切分等子流程在内的全套设计方法学和工具,以及包括电、热、时序、功耗、设计规则检查等在内的全套系统性能分析和设计签核工具,辅以强大便捷的流程管理器和3D可视化界面,使能系统设计芯片设计者最大限度的发挥想象力高质量的实现各种复杂3D-IC设计。

在刚刚结束的TSMC开放创新平台大会上,Cadence更是成为唯一一家获得TSMC 3DFabric全流程(系统规划、实现及系统级签核)认证的合作伙伴。

3D-IC设计不同于传统意义上的2D设计,2D芯片经过几十年的发展已经在设计、制造、封装角度形成了固定的流程。而3D-IC设计中系统设计会在很大程度上被最终的流片厂封装厂甚至TSV/Bump提供商的具体制造方案影响。这也是为什么传统3D-IC设计是由封装团队而不是设计团队或者完成3D系统设计或者制定出对每个晶粒的约束条件,并且由设计团队参考封装约束条件实现芯片的物理设计。但伴随着3D-IC从一种可选的技术方案走向集成度或系统性能驱动的必选方案,如何提高原封装驱动的设计流程的自动化以及如何从系统角度得到全系统性能、功耗、面积、散热的最优化设计已经变成的越来越重要。并且在此基础上还要考虑不同3D制造、封装方案对系统设计的影响。再考虑到设计不同阶段和不同步骤的设计意图交互和数据交互以及ECO需求,这一切都不是原有基于不同设计团队的不同点工具所能轻松解决的。

在过去的几个月里,我们为大家推出了一系列的文章,涵盖了通过Integrity 3D-IC平台的从系统规划、中介层布线自底向下实现、早期三维布图综合及层次化设计Memory-on-Logic堆叠实现三维寄生参数提取和静态时序分析等步骤和流程在内的全流程解决方案:

3D-IC设计之如何实现高效的系统级规划

3D-IC设计之中介层自动布线

3D-IC设计之自底向上实现流程与高效数据管理

3D-IC设计之早期三维布图综合以及层次化设计

3D-IC设计之Memory-on-Logic堆叠实现流程

3D-IC设计之寄生抽取和静态时序分析

3D-IC设计之系统级版图原理图一致性检查

该方案可以在最大限度上提高设计在不同3D-IC制造方案的可迁移性,从而最大程度减少芯片设计团队对于3D-IC先进封装技术的学习成本,封装设计团队对芯片威廉希尔官方网站 的学习成本,系统多物理验证和签核团队对芯片设计和封装设计的学习成本,从而使团队中的每个角色专注于自己所熟悉的领域,更快的实现3D-IC产品全系统的设计收敛和签核,通过传统工艺实现更高系统集成度,或在先进工艺节点或异构集成系统上进一步提高数据带宽、吞吐率和传统的性能、功耗、面积等综合系统指标。

Integrity 3D-IC平台的推出只是开始,我们期待越来越多的设计者借助Integrity 3D-IC将两维设计平面拓展到三维设计空间,来实现5G/6G通讯、人工智能、数据中心、高性能移动处理器、汽车电子等越来越先进的创新需求,为人类的生产生活开创更加美好的未来!

如您需了解Cadence 3D-IC Integrity 平台的更多内容,请点击“阅读原文” 注册申请我们的Integrity 3D-IC资料包。

Integrity 3D-IC资料包:

-Cadence Integrity 3D-IC 平台 产品手册

-Cadence Integrity 3D-IC 平台PPT资料包

注册成功且通过Cadence审核的用户可获得完整版PPT资料。审核通过后Cadence会将PPT发送至您的邮箱,提供您的公司邮箱地址通过审核的几率更大哦!

Cadence Integrity 3D-IC 平台提供了一个高效的解决方案,用于部署 3D 设计和分析流程,以实现强大的硅堆叠设计。该平台是 Cadence 数字和签核产品组合的一部分,支持 Cadence 公司的智能系统设计战略(Intelligent System Design) ,旨在实现系统驱动的卓越 SoC 芯片设计。

审核编辑 :李倩

-

IC设计

+关注

关注

38文章

1297浏览量

104046

原文标题:3D-IC未来已来

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

3.5D封装来了(下)

揭秘3D集成晶圆键合:半导体行业的未来之钥

3D打印技术应用的未来

剖析 Chiplet 时代的布局规划演进

Samsung 和Cadence在3D-IC热管理方面展开突破性合作

西门子推出Innovator3D IC,用于 3D IC 设计、验证和制造的多物理场集成环境

西门子推出Calibre 3DThermal软件,持续布局3D IC热分析

借助云计算加速3D-IC可靠性的机械应力模拟

用6个NMOS + 3个驱动IC来搭桥,低边NMOS的G极驱动电压如果大于D极,是否会有问题?

未来已来,多传感器融合感知是自动驾驶破局的关键

3D-IC 以及传热模型的重要性

Cadence携手Intel代工厂研发先进封装流程,助力HPC、AI及移动设备

TSMC-SoIC,InFO,CoWoS之间的关系?

3D-IC未来已来

3D-IC未来已来

评论