Vivado工程升级及板级信号调试方案

描述

本次操作包括:工程的版本迁移,板级测试时信号的抓取。

如何使用新版本的vivado去打开旧版本的vivado工程

如何使用新版本的vivado去打开旧版本的vivado工程。

对于旧版本的vivado工程或者是ise工程,更新到新版本的vivado环境下有两种方法:

1、直接用新版本vivado打开原有工程文件,进行IP核更新; 2、拷贝原有工程设计文件、约束文件、IP核文件夹至新建新版本vivado空白工程文件下,进行更新。

1、在旧版本vivado基础上直接升级

我们先来介绍一下如何直接使用新版本打开旧版本工程并且进行升级。

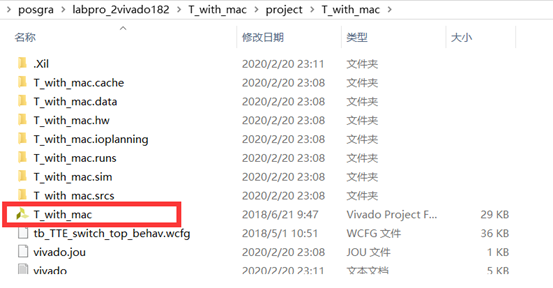

直接使用新版本vivado打开vivado的工程文件。

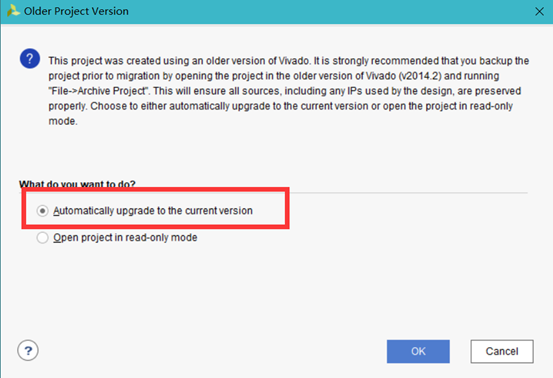

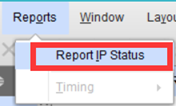

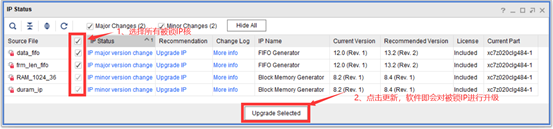

对于新版本vivado一般在打开旧版本工程时都会自动进行更新默认自动更新就好。 打开工程之后,需要对旧版本工程的IP核进行升级操作。点击Reports->Report IP Status查看IP核被锁状态进行升级。

选中所有IP核进行升级。

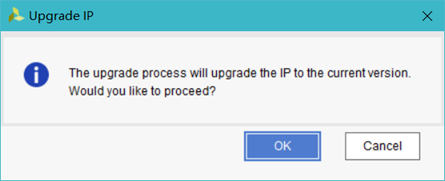

点击确定。

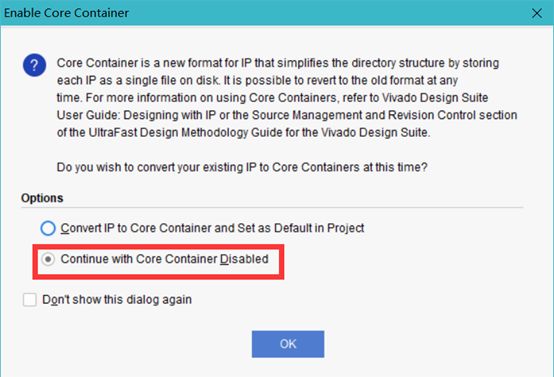

保持默认不使用核容器,(Core Container没有用过,我都是默认不使用)。

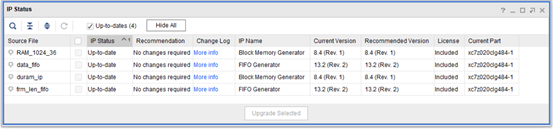

升级完成之后的界面如图所示。

如何使用新版本的vivado去打开旧版本的vivado工程

debug步骤:

在需要debug的输入输出端口列表前加 (* mark_debug = “true” *)。

在编译通过后,进行综合生成网表等文件,点setup debug进行添加。

保存,xdc中应该有约束了,原理图里也有ila_core 模块,直接进行实现即布局布线。

在线调试:生成比特后下载,run trigger。

注意:在有多个debug端口时,会引入1个以上ila_core,每一个ila_core 的时钟域都是独立的,且在每一个ila_core中各个端口的时钟域是一样的。

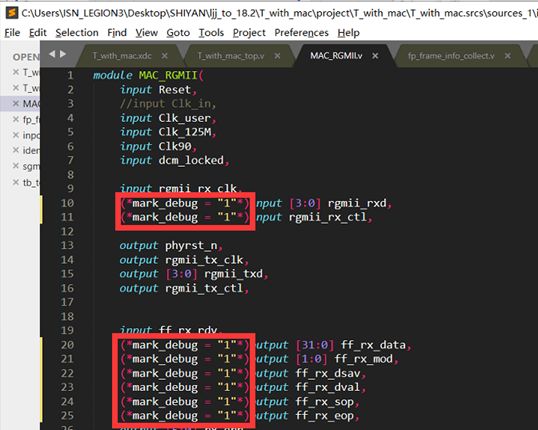

1、设置信号抓取标记

将需要测试的端口前标记上(*mark_debug = “1”*)或者(*mark_debug = “true”*)

注意:这里最好将需要测试的端口信号打一拍再进行测试,因为输入输出端口的驱动单元类型往往是不一样的,比如两个红框之间的rgmii_txd信号它的驱动单元类型就是ODDR,这将影响布线到此处的逻辑分析仪ila的探针的连接,具体的我也不清楚应该是驱动能力不匹配之类的,反正最好实现的时候会报错。如果不打拍则在后续设置setup debug的时候就要注意去除不符合驱动类型的信号。

2、建立debug文件

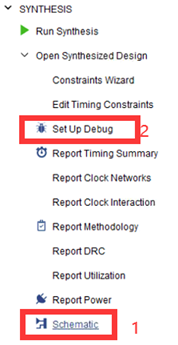

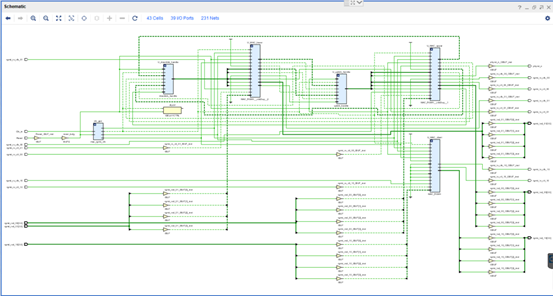

添加完debug标记后,进行编译、综合,没有问题则可以查看当前原理图(其实也可以不用看,这里只是为了对比ila模块)然后点击Set Up Debug对刚刚添加的信号进行设置。

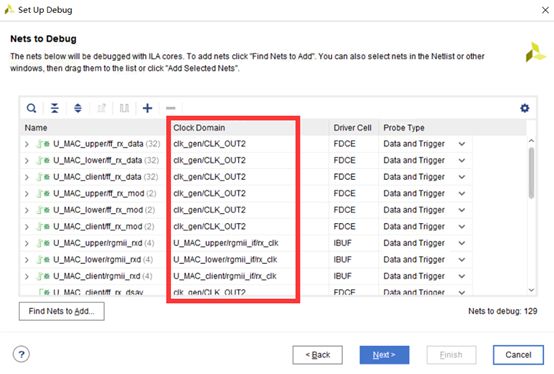

设置的信号有几个需要注意的地方:

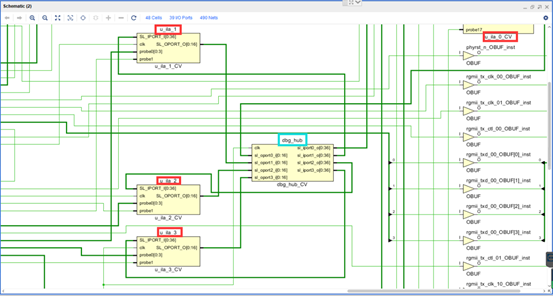

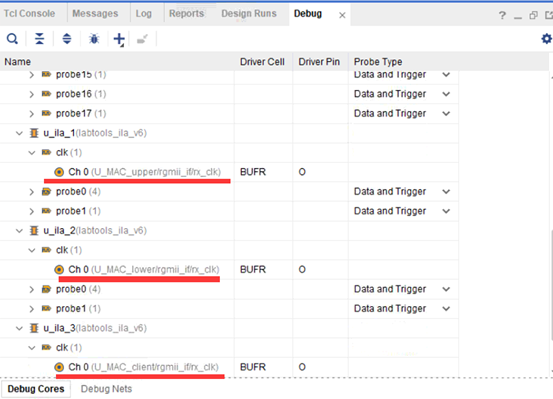

1、关于时钟域的选择,如图红框部分,这些时钟需要选择free clock,所谓free clock(按照我自己的理解,也可能不准确)就是系统一上电就能运行的时钟,并且不会因为复位以外的条件停振,比如有些时钟为了节省功耗,仅在需要进行数据交换时振动,在其他时刻保持低电平,但是这种时钟就不是free clock。

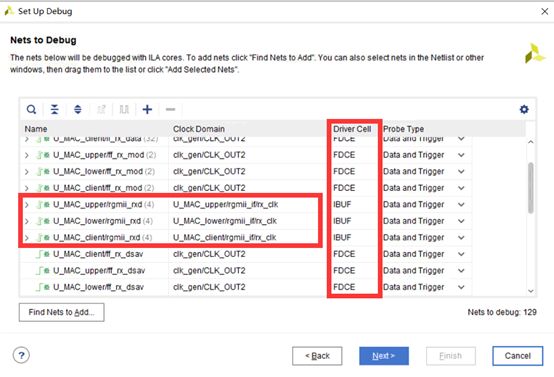

2、注意选择具有符合标准驱动单元的信号,这里右侧红框中都是可以的,但是对于DDR型的驱动信号就会出错。

3、同一个时钟域的信号都在同一个ila模块下,即有几个时钟域就会有几个ila模块。

这里需要注意:

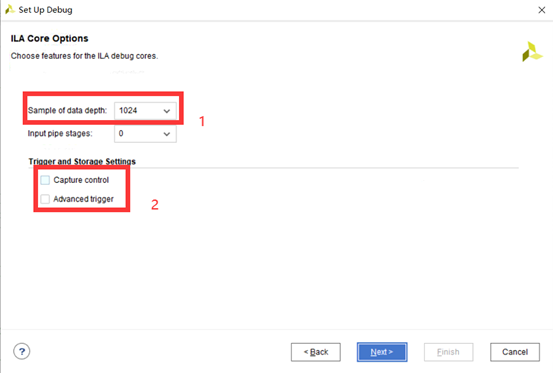

1、是选择采样深度,会占用一定的FPGA资源,所以如果设计系统简单就可以选择多一点,可以看到较长时钟周期内存储的信号变化。

2、选择上后,可以进行高级设置操作(选了也没用上==)。

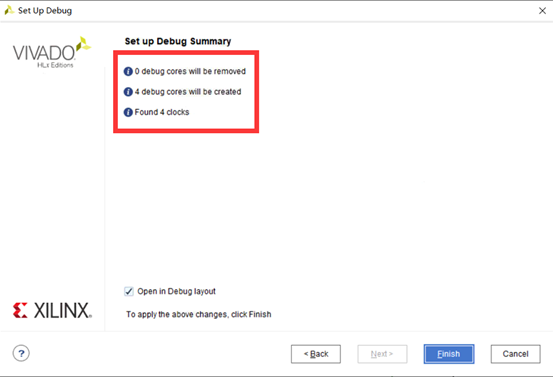

可以看到这里的summary是4个时钟域和之前选择一致。

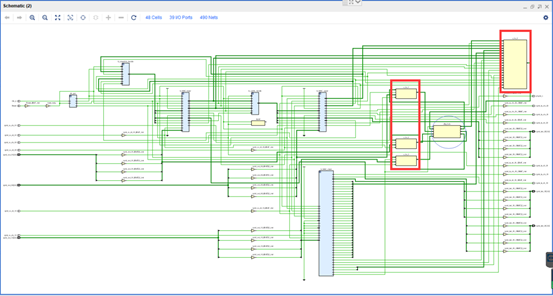

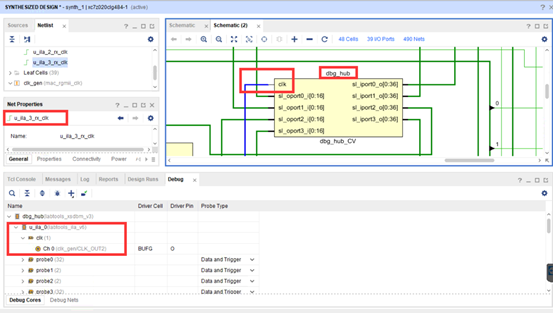

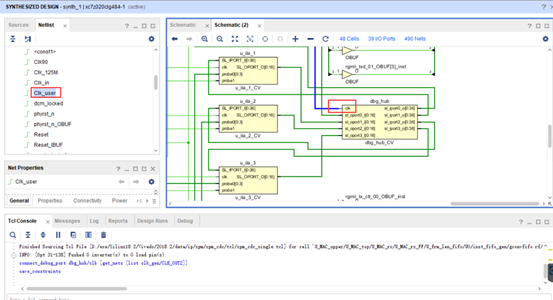

这是两张原理图,后者的红框框部分是添加的4个ila模块,中间蓝色圆框部分是debug hub,即连接FPGA和jtag的部分。

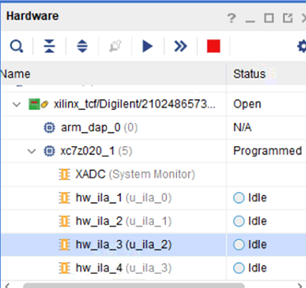

在底部Debug窗口可以看到各个ila模块的时钟选择。

对于debug hub时钟域的选择查看可以通过tcl命令也可以点击原理图连线的方式,在左侧会有连接显示,这里看到是连接到了ila3模块上,这样不太好,因为如果ila3的时钟没选择对就会导致整个debug hub在后面下载比特时无法被检测到,就算其他ila的时钟对了也白瞎。因为计算机是通过jtag返回数据的,而jtag又靠着debug hub 连接fpga的ila。

3、完善XDC文件,实现威廉希尔官方网站

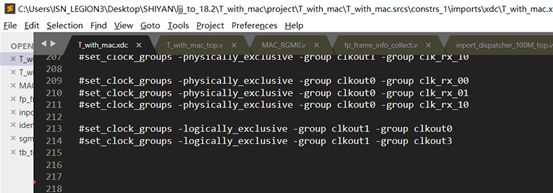

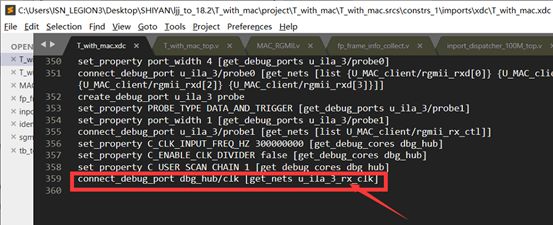

修改完成之后,依然需要保存修改,看到这里没有保存约束文件在214行。

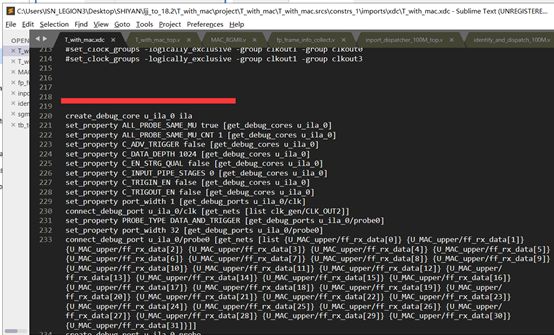

保存之后xdc增加了ila模块的对应约束。

这里对应debug hub 的连接时钟。

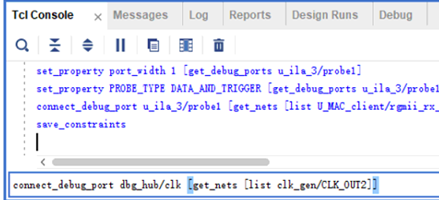

之前说了debug hub时钟保持默认的缺点,这里通过tcl命令进行修改,通过查看ug908文档可以知道推荐的debug hub时钟在100Mhz左右,且至少在JTAG下载速率的2.5倍以上,采样定理嘛,一般jtag速率默认15Mhz,查看代码中时钟生成部分,发现CLK_OUT2也就是mac的用户侧时钟就是100Mhz,所以我们选择debug hub时钟为100Mhz。

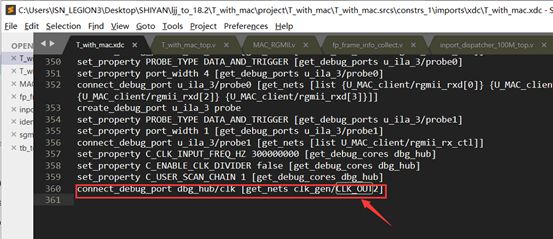

修改完成后,查看xdc确认已经修改了(其实也可以直接通过xdc

修改,但是直接修改xdc软件可能会提示综合过期,让重新综合,而通过tcl则可以直接进行后面的步骤)。

我们再次查看原理图,可以看到debug hub的时钟域已经修改。

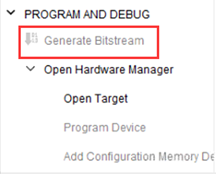

4、生成比特流文件,进行板级调试并抓取信号

直接生成比特文件。

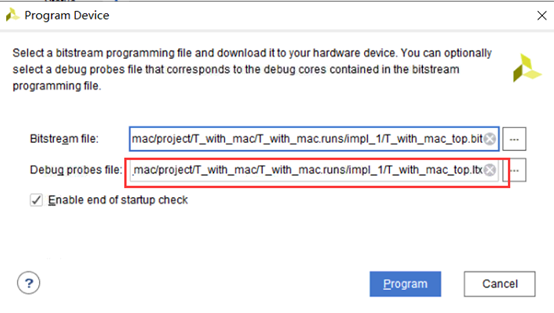

相比较之前的工程版本迁移时的下载界面,红框部分多出了后缀为ltx的文件,即逻辑分析仪的探针文件。

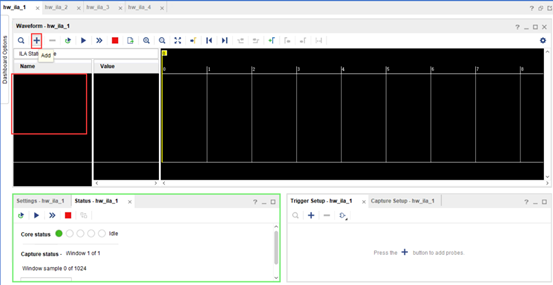

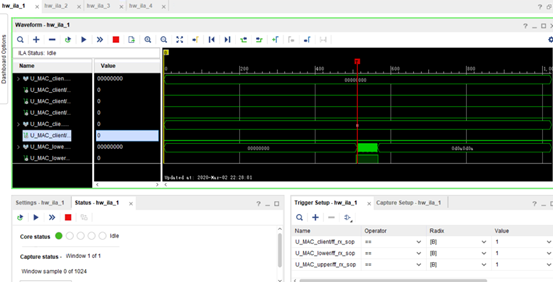

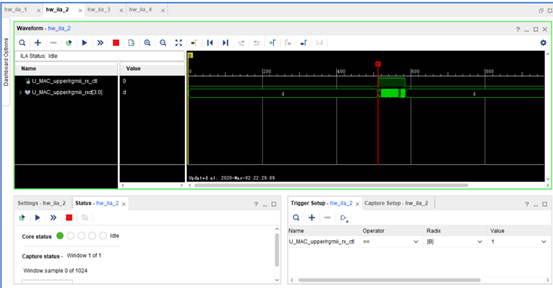

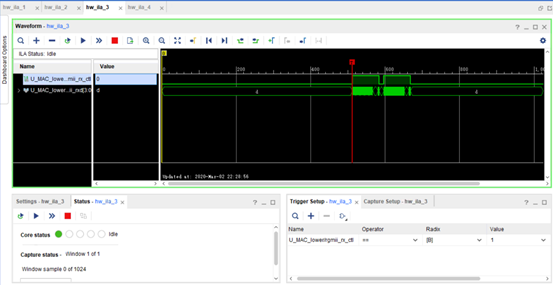

下载完成后会弹出4个dashboard对应着4个不同时钟域的ila模块,可是没有信号,这时可以点击+号进行添加。

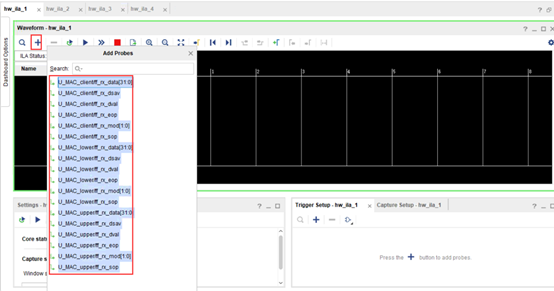

ctrl+a选中所有进行添加。

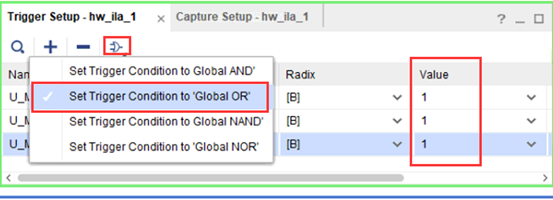

添加完信号后注意右下角的触发条件设置,同样点击+号设置需要添加的信号,这里选则的是帧起始标志sop,并且选择触发条件的关系为或,同时触发值设置为1’b1,之后再点击三角型的 run trigger符号即可。

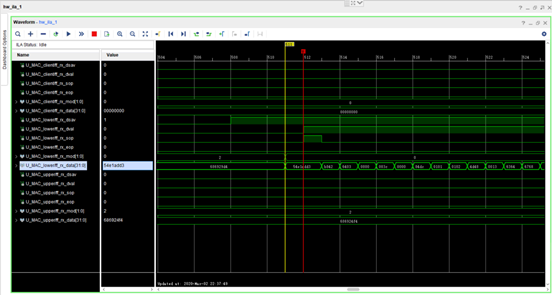

这里lower部分已经有波形了。

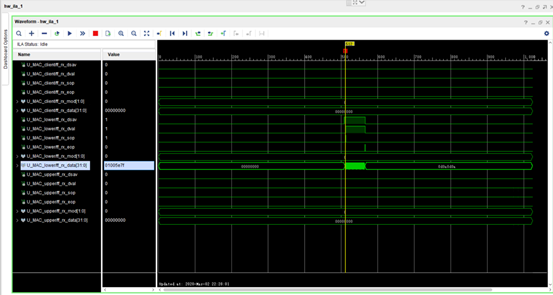

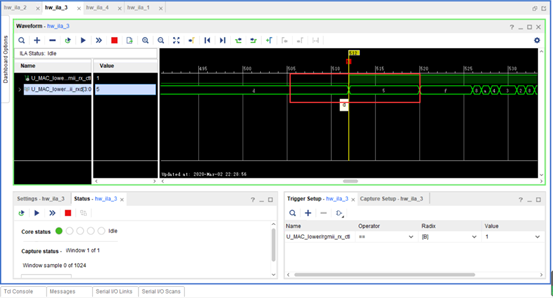

放大看所有的信号。

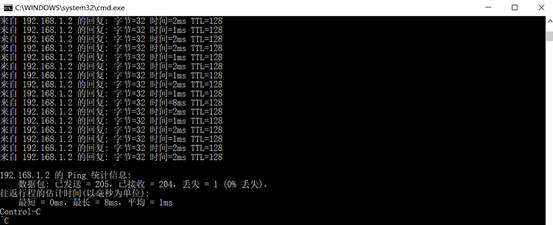

这里发现没有前导码是因为这里的4字节数据已经是进了mac之后经过了8转32的数据了已经去掉了前导码和CRC。但是upper client没有数据,原来是没有ping都没有发怎么有?

结果发现ping了也没有,好气。

注意之前设置的触发条件,是或关系,于是lower的sop信号在当前的1024个钟内比其他的sop先触发,而各个sop的间隔周期大于我们设置的采样深度1024,所以无法同时显示,删除lower触发条件后就有了,当然lower又没有了。

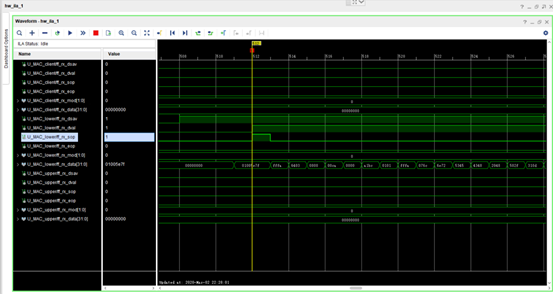

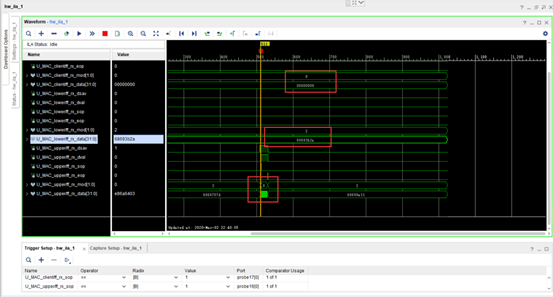

这边按照同样的步骤,添加观察信号、添加设置触发条件、点击run trigger,就能看到波形了,注意放大后的红框部分,有了前导码,按单字节应该是 55 55 55 d5的顺序而这里由于是rgmii只是半字节,所以是 5 5 5 5 5 5 5 d。

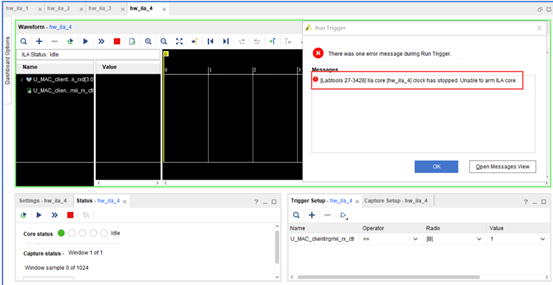

对ila3按同样的步骤操作当我们点击run trigger的时候会发现出现unable to arm ila core的错误,这就是时钟域的问题,由于我们选择的是rgmii_rx_clk这是由phy提供的,但是ila3即例化时的client对应的phy没有插网线,所以也没有时钟,自然无法arm ila core。

这里特意为了对比不同时钟域的选择对于ila的影响,其实也可以将lower upper client的ila时钟域都设置成用户侧即CLK_OUT2因为这个时钟一直存在,这样即使ila3对应的模块的网口没有插网线,在dashboard上显示也会有全0 的数据,就和ila0 一样,可以翻到前面去看看,这里的lower upper client的ff_rx_data[31: 0]来自三个独立的例化模块,但是也可以放到同一个时钟域。表达的不太好实践一下就能知道了。

审核编辑:汤梓红

-

vivado ILA在线调试求助2017-12-11 0

-

vivado在线调试2017-12-20 0

-

玩转Zynq连载5——基于Vivado的在线板级调试概述2019-05-24 0

-

玩转Zynq连载33——基于Vivado的在线逻辑分析仪板级调试2019-10-28 0

-

玩转Zynq连载36——[ex55] 基于VIO在线板级调试的AXI GP总线读写实例2019-11-21 0

-

Vivado中综合,实现,编程和调试工程可能会出现的问题及解决方案2021-07-31 0

-

Vivado中使用debug工具步骤与调试技巧2017-11-17 60233

-

使用Vivado 2016.3中IBERT调试的好处及步骤2018-11-20 5779

-

如何使用Vivado Logic Analyzer与逻辑调试IP进行交互2018-11-30 3398

-

如何使用Vivado在设备启动时进行调试2018-11-22 4443

-

如何升级Vivado工程脚本2022-08-02 1850

-

ISE工程升级到Vivado及板级信号调试2023-01-30 4371

-

Vivado Design Suite用户指南:编程和调试2023-09-13 238

-

Vivado设计套件用户指南:编程和调试2023-09-13 240

-

Vivado Design Suite 用户指南:编程和调试2023-10-25 898

全部0条评论

快来发表一下你的评论吧 !