AMD可以把内存堆在CPU上吗?

描述

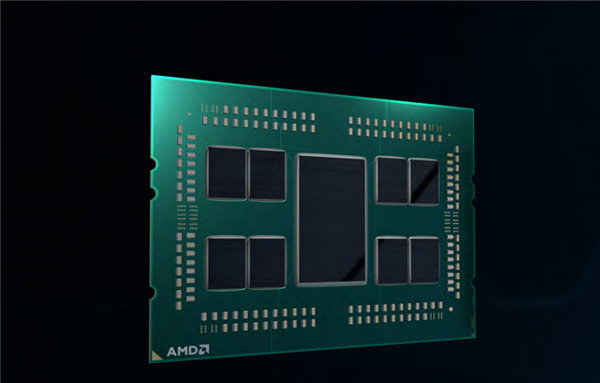

先进制程工艺进度缓慢的情况下,多芯片整合封装成了半导体行业的大趋势,各家不断玩出新花样。

ISSCC 2023国际固态威廉希尔官方网站 大会上,AMD提出了多种新的整合封装设想,其中之一就是在CPU处理器内部,直接堆叠DRAM内存,而且是多层堆叠。

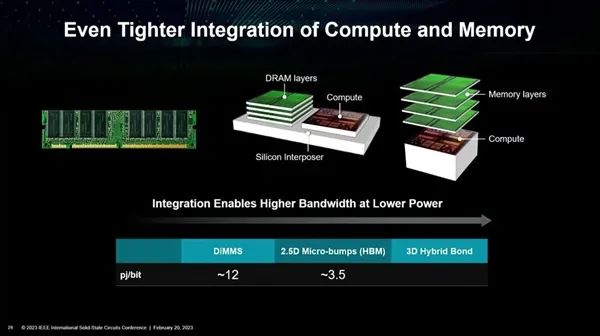

一种方式是CPU计算模块、DRAM内存模块,并排封装在硅中介层上,而另一种方式就是在计算模块上方直接堆叠内存模块,有点像手机SoC。

AMD表示,这种设计可以让计算核心以更短的距离、更高的带宽、更低的延迟访问内存,而且能大大降低功耗,2.5D封装可以做到独立内存功耗的30%左右,3D混合键合封装更是仅有传统的1/6。

如果堆叠内存容量足够大,主板上的DIMM插槽甚至都可以省了。

当然,AMD的这种设想仅面向服务器和数据中心领域,桌面上不会这么做,否则就无法升级了。

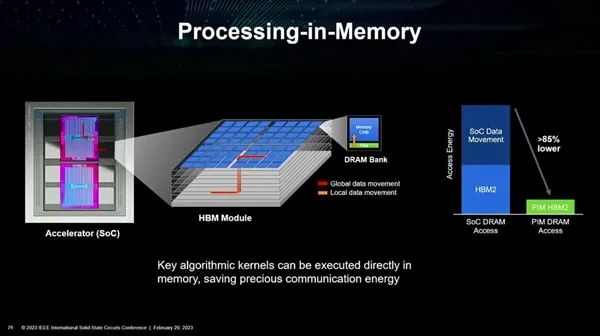

AMD甚至考虑在Instinct系列加速卡已经整合封装HBM高带宽内存的基础上,在后者之上继续堆叠DRAM内存,但只是一层,容量不会太大。

这样的最大好处是一些关键算法内核可以直接在整合内存内执行,而不必在CPU和独立内存之间往复通信传输,从而提升性能、降低功耗。

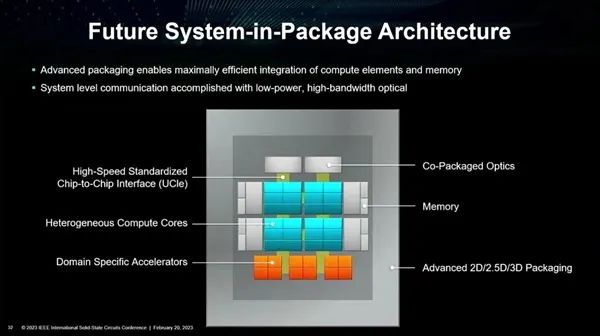

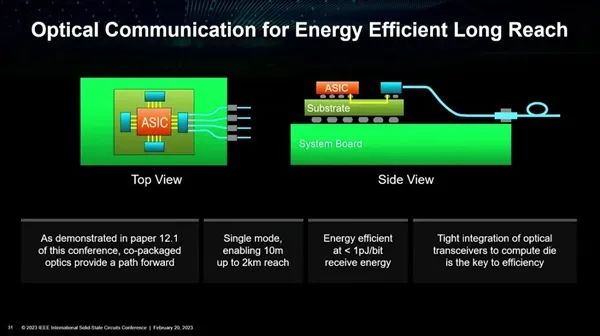

另外,AMD还设想在2D/2.5D/3D整合封装芯片的内部,除了CPU+GPU混合计算核心,还集成更多模块,包括内存、统一封装光网络通道物理层、特定域加速器等等,并引入高速标准化的芯片间接口通道(UCIe)。

尤其是引入光网络通道,可以大大简化网络基础架构。

我们知道,AMD最近两年的CPU及GPU显卡已经转向了chiplets小芯片架构设计,每个芯片由不同的模块组成,可以降低芯片生产难度,提高良率,控制好成本。

AMD的芯片代工主要由台积电完成,不过小芯片封装主要是靠国内的芯片封测公司通富微电。

通富微电表示,通过在多芯片组件、集成扇出封装、2.5D/3D等先进封装技术方面的提前布局,可为客户提供多样化的Chiplet封装解决方案,并且已为AMD大规模量产Chiplet产品。

通富微电还提到,目前,大多数世界前20强半导体企业和绝大多数国内知名集成威廉希尔官方网站 设计公司都已成为通富微电的客户。

通过并购,公司与AMD形成了“合资 合作”的强强联合模式,建立了紧密的战略合作伙伴关系;

AMD完成对全球FPGA龙头赛灵思的收购,实现了CPU GPU FPGA的全方位布局,双方在客户资源、IP和技术组合上具有高度互补性,有利于AMD在5G、数据中心和汽车市场上进一步迈进。

公司是AMD最大的封装测试供应商,占其订单总数的80%以上,未来随着大客户资源整合渐入佳境,产生的协同效应将带动整个产业链持续受益。

顺便看看新工艺。

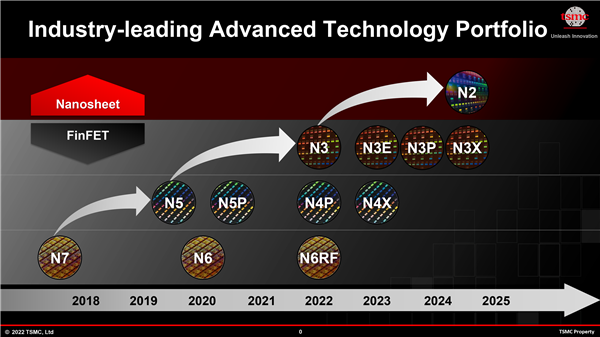

在3nm工艺上,虽然三星在去年6月份抢先宣布量产,晚了半年的台积电却后发先至,因为他们拿到了最重要的客户——苹果订单,而且首批的3nm产能是苹果包圆的,其他厂商都要靠后,甚至2023年都有可能是苹果独占。

目前苹果用的是第一代3nm,也就是N3工艺,相比于5nm工艺,3nm工艺的逻辑密度将增加60%,相同速度下功耗降低30-35%,这是世界上最先进的技术。

其他厂商要等第二代3nm,也就是N3E工艺,对比N5同等性能和密度下功耗降低34%、同等功耗和密度下性能提升18%,或者可以将晶体管密度提升60%,密度比N3还缩水一些,但是成本也低。

那苹果包圆的3nm工艺现在进展到底如何?消息人士透露,位于南科18B的3nm晶圆厂现在已经可以做到日投片量1000片,超过1000片的产量很重要,通常意味着芯片真正进入了量产阶段。

有关台积电及三星的3nm良率一直都是个谜,此前的传闻说是三星的3nm良率仅有10-20%,台积电的3nm良率可达70-80%,然而后者的良率也太高了,又被戳穿实际上只有不到50%良率。

不过随着投片量超过1000片晶圆,台积电3nm良率争议应该可以告一段落了,至少用于生产已经没什么大问题了。

审核编辑:刘清

-

【原创】堆内存的那些事2021-07-12 0

-

关于RT-Thread的动态内存堆管理简析2022-04-06 0

-

无法在AMD Ryzen CPU上运行OpenVINO trade怎么解决?2023-08-15 0

-

从外观上识别内存2009-12-17 2748

-

Java开发者必须了解的堆外内存技术2018-07-01 3786

-

两种常见的内存管理方法:堆和内存池2018-05-31 13651

-

AMD发威 美光、华硕拿下内存超频世界第一2019-11-27 868

-

CPU参数、主板设置里的内存频率有啥区别2020-09-09 7394

-

把进程绑定到某个 CPU 上运行是怎么实现?2021-07-02 2414

-

什么是堆内存?堆内存是如何分配的?2021-07-05 9993

-

AMD要在CPU上堆叠DRAM内存,新一代捆绑销售诞生?2023-02-24 2763

-

什么是堆内存?存储方式是什么样的?2023-06-22 1182

-

堆栈内存和堆内存之间的区别2023-08-07 726

-

jvm配置堆内存初始值参数2023-12-05 776

全部0条评论

快来发表一下你的评论吧 !