一文详解封装互连技术

电子说

描述

任何一个电子元件,不论是一个三极管还是一个集成威廉希尔官方网站 (Integrated Circuit, IC),想要使用它,都需要把它连入威廉希尔官方网站 里。一个三极管,只需要在源极、漏极、栅极引出三根线就可以了,然而对于拥有上百或上千个引脚的超大规模集成威廉希尔官方网站 (Very Large Scale Integration Circuit, VLSI)来说,靠这种类似于手动把连线插到面包板的过程是不可能的。直接把IC连接到 (未经封装的集成威廉希尔官方网站 本体,裸片,Die)威廉希尔官方网站 中也是不可能实现的,因为裸片极容易收到外界的温度、杂质和外力的影响,非常容易遭到破坏而失效。

所以电子封装的主要目的就是提供芯片与其他电子元器件的互连以实现电信号的传输,同时提供保护,以便于将芯片安装在威廉希尔官方网站 系统中。

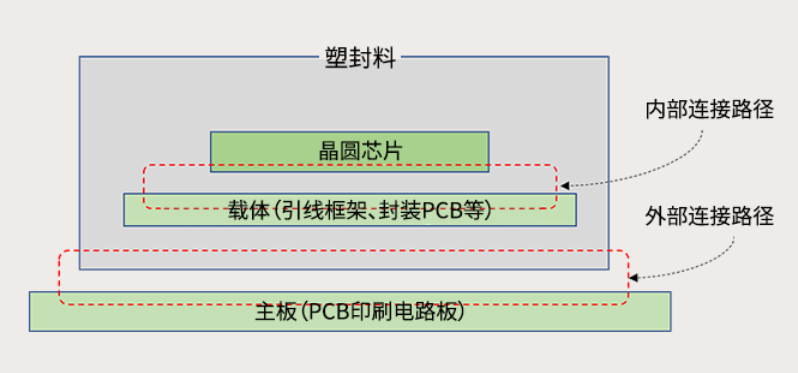

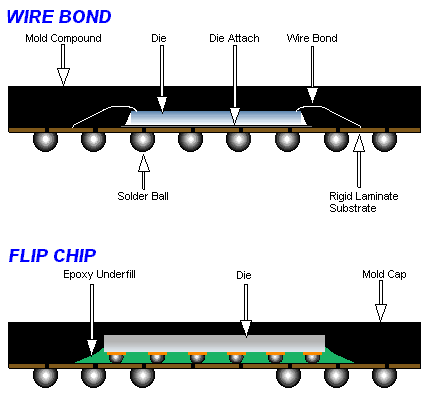

一般的半导体封装都类似于下面的结构,将裸片安装到某个基板上,裸片的引脚通过内部连接路径与基板相连,通过塑封将内部封装好后,基板再通过封装提供的外部连接路径与外部威廉希尔官方网站 相连,实现内部芯片与外界的连接,就像上面两个图一样,裸Die和封装内部复杂的连接等都埋在里面,封装好后就是对外就是一些规整的引脚了。

不论是多复杂的封装,从黑盒的角度来看其实现的基本功能都是一样的,最简单的就是封装一个分立器件,给出几个引脚;复杂一点想要封装具有多个I/O接口的IC,以及多个IC一起封装,在封装的发展过程中也发展出了很多封装类型和很多技术,比如扇出技术、扇入技术这些。这些概念和缩写非常多,尤其是当谈到先进封装(Advanced Packaging)的时候,为了实现高密度集成以及快速信号传输这些需求,不得不在每一个地方都发展一些新的技术,很多情况下会把它们都并入到先进封装技术里来介绍,这有时候会引起一些困惑,这里主要整理一下IC封装里的互连技术。在IC封装种几种典型的互连技术包括引线键合(Wire Bonding,WB)、载带自动焊(Tape-automated Bonding,TAB)、倒装芯片(Flip Chip,FC)、晶圆级封装(Wafer-Level Packaging,WLP)、以及硅通孔(Through Silicon Via,TSV)。像模块化设计一样,同一种封装类型中也可能采用不同的互连技术,比如常用在手机芯片里的BGA封装有引线键合形式和倒装形式,不同的互连技术也可能同时出现在一个复杂封装中。

封装互连技术

引线键合

引线键合是最经典使用最广泛的互连技术,使用金属线,利用热、压力、超声波能量将金属引线与基板焊盘紧密焊合,从而实现芯片与基板间的电气互连和芯片间的信息互通。

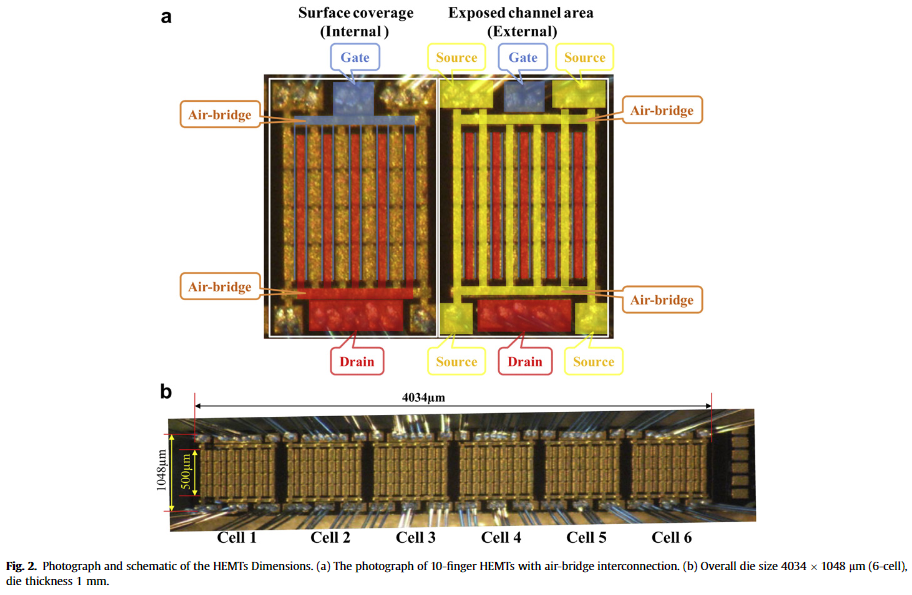

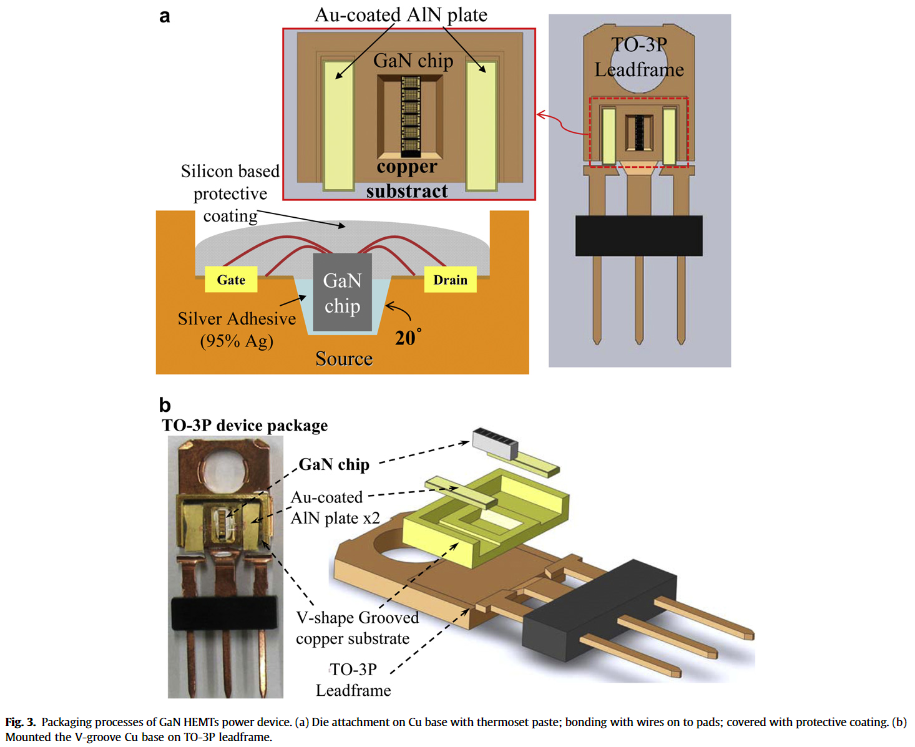

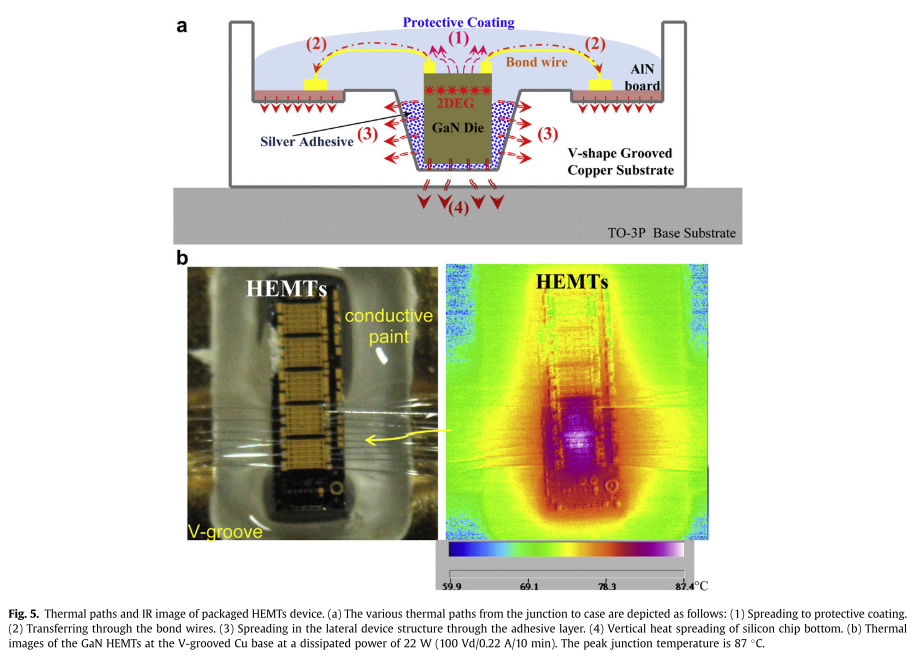

在GaN器件的封装中,引线键合也是最常采用的互连技术。以GaN HEMTs的某个典型封装为例,(Applied thermal engineering 51.1-2 (2013): 20-24.),内部裸Die的部分就是连到一起的6组每组10个finger的GaN晶体管,共计60个晶体管构成了一个多栅GaN器件。

通过引线键合,把这60个晶体管的栅极和漏极,统一连接到栅极pad和漏极pad上,这两个pad再分别和左右两边的引脚相连,源极的部分和中间一整片引脚相连,最后封装好后对外界体现出来的,就是一个三端子的HEMT黑盒,这种长着三个引脚的封装形式称为晶体管外形封装(Transistor Outline,TO)。

中间的GaN Die部分,就是文章里常说的近结区域(Near-junction Region),整个GaN器件起到作用的部分就是这里。

载带自动焊

从上面的动画里也能看出来,引线键合必须对每一个触点分别打线,效率比较低,一个改进的想法就是只操作一次,就能同时连好所有的线。TAB技术就是先根据裸片的I/O接口分布,制作一条特制的载带,载带可以被看成是最早的柔性威廉希尔官方网站 ,在有机薄膜上,裸片引脚的对应位置提前加工好金属比如铜引脚,然后只要把载带贴到裸片上,一次性就实现了所有接口的连接。

倒装芯片

像上面一样,在标准封装中,芯片正面朝上贴装到基板上,通过线来将芯片与基板上对应结点相连接。相对地,在倒装技术中,不再通过连线实现裸片和基板的相连,而是将裸片倒过来放置,通过金属焊球直接实现连接,这种方案减小了信号传输的距离,提高了信号传输速度。

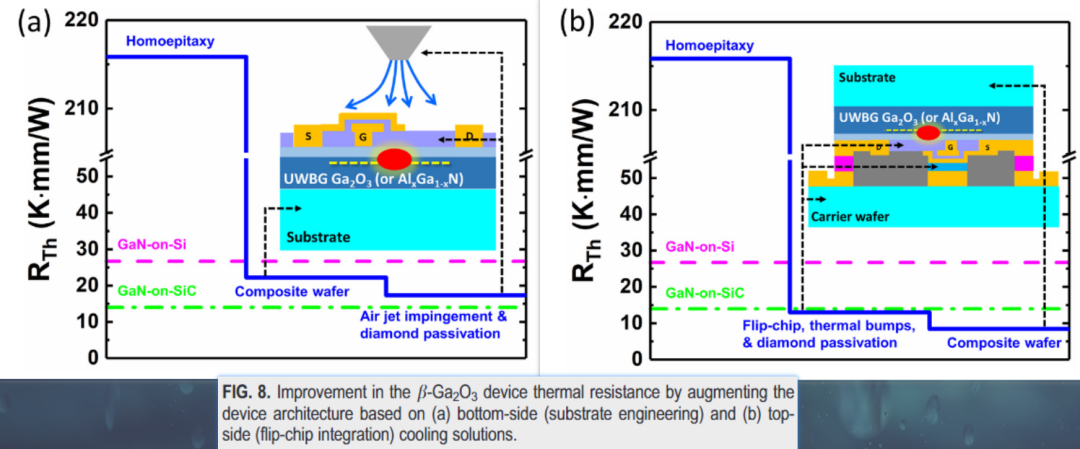

倒装对传热也有一定的帮助(Applied Physics Letters* 119.17 (2021): 170501.),传统封装是把衬底贴到封装上,这时候下部的导热路径太长,上部的导热路径太短,把裸片倒过来放,让下面贴到封装上,把衬底放到上面,下面可以继续加一些热泵或者塞一些高热导率的填充物把热点连到扩热板上,上方的衬底也可以换成高热导率材料,这时候两条路径都可以实现热量输运。

晶圆级封装

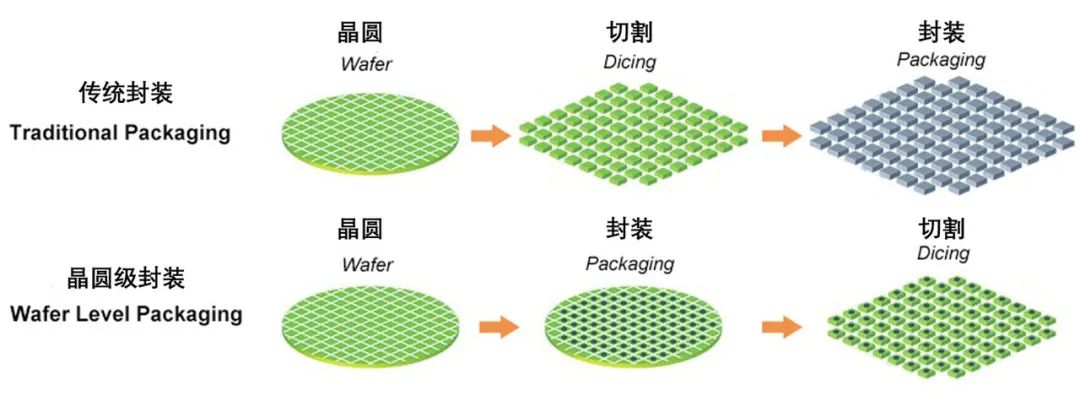

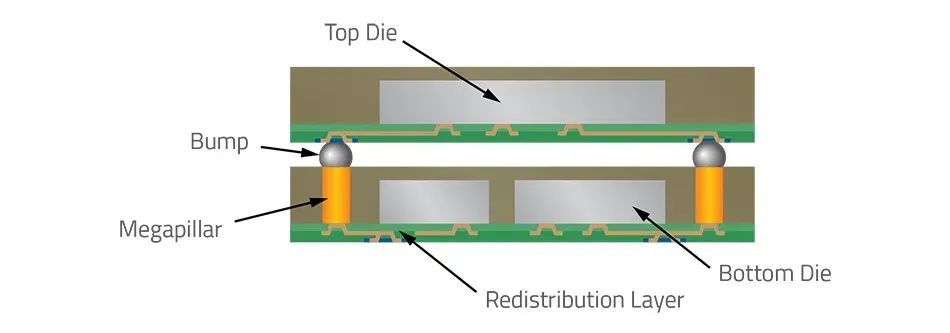

晶圆级封装实际上是一种封装类型,但是为了互连,封装中存在重布线层(Redistribution Layer),通过焊球进行连接。在洁净室的IC制造分为两道工序,前道工序(Front End of Line,FEOL)负责形成CMOS晶体管结构,在金属互连层沉积之前的工序都可归为FEOL;在晶体管结构加工完毕了,需要进行金属布线来给晶体管进行供电并实现信息交换,这部分属于后道工序(Back End of Line,BEOL)。在后道工序结束后,把做好的晶圆交给封测厂,封测厂进行晶圆测试,把晶圆切割成单个芯片,然后再进行对每一个芯片进行单独封装,这部分工序一般称为(back-end process,or post-fab)。fab就是fabrication的缩写,IC fabrication,在集成威廉希尔官方网站 领域fab指的就是晶圆厂,post-fab,就是晶圆厂之后的事了。晶圆级封装就是在晶圆的状态就对芯片进行封装,封装好了以后再切割成单个芯片,保护层以及对外的威廉希尔官方网站 连接接口在切割前就已经完成。这种封装方式可以做到几乎和裸片一样的封装尺寸,且由于连线较短,信号传输速度也较高,同时也能降低工业成本以及缩短生产周期。

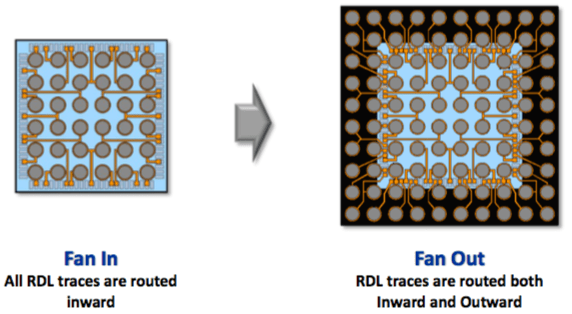

晶圆级封装又可以分为扇入型晶圆级封装(FIWLP)和扇出型晶圆级封装(FOWLP)。裸片上存在IO接口,但是这些IO接口的位置可能不太好,对于某些复杂的封装工艺这些接口可能很难与封装的接口相连接,于是RDL工艺就诞生了,RDL是一层金属互连线,与裸片的IO接口相连,重新排布这些IO接口的位置,以便裸片更容易地与载体相连接。

扇入(Fan In,FI)就是在原芯片尺寸内部将所需要的IO接口重排布完成,封装尺寸基本等于芯片尺寸,在IO接口数量比较小的情况下可以采用这种技术。而当IO接口数量很大,在现有芯片的尺寸内已经放不下这些锡球了,就可以扇出(Fan Out,FO)技术,通过特殊的填充材料人为扩大芯片的封装尺寸,在扩充后的整个范围内走线和排布IO。

FIWLP就是对晶圆上的每个芯片做Fan In封装,FOWLP就是先把整个晶圆上的不同芯片切下来,然后把他们整体移植到一个更大的晶圆上,然后对更大的晶圆做晶圆级封装。

硅通孔

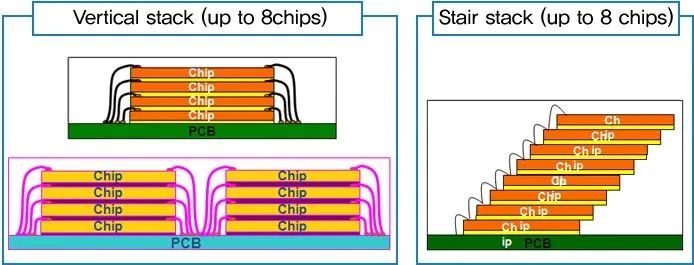

想要将很多芯片叠起来,实现他们之间的互联,可以采用下面这个方案,每一层都通过引线键合连到最下面的基板上,通过基板来实现芯片间的互连。

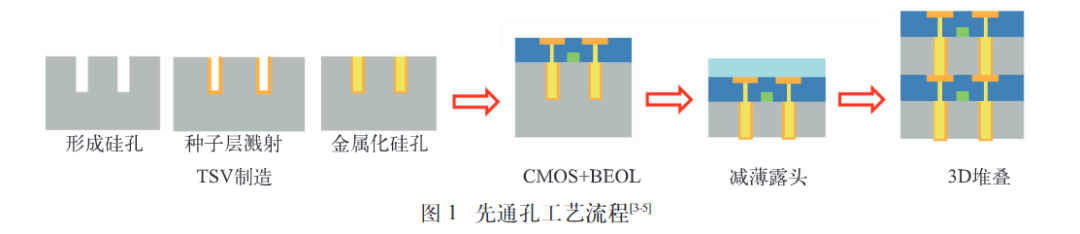

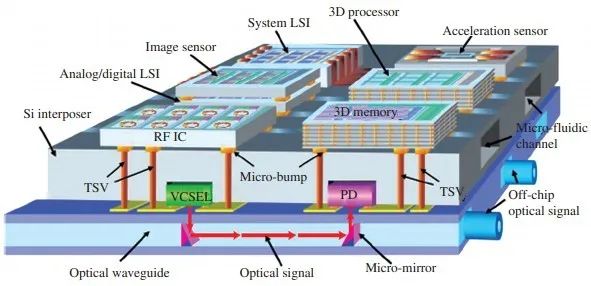

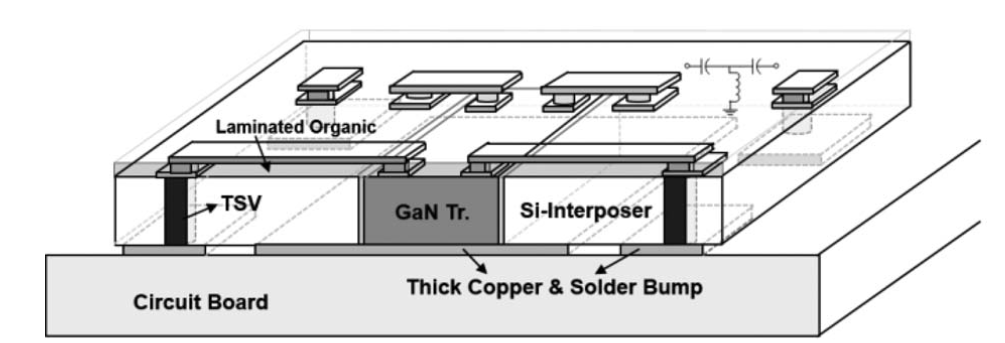

但是这种方案没有很好地利用垂直空间,引线太多且比较长,信号传输比较慢。一个想法就是把堆叠的芯片之间相互垂直联通,于是TSV就产生了,把裸片放在硅中介层(Si interposer)上,加工一些列的贯通孔,在孔中沉积铜、钨等导电物质,覆盖结构的顶部,实现通过硅通孔的垂直电气导通,实现堆叠芯片间的互联。TSV的引入使得裸片之间可——+以直接互连,而不需要通过大量的引线在基板上再实现互连,可以提高更高密度的集成、以及更快的信息传输速度。

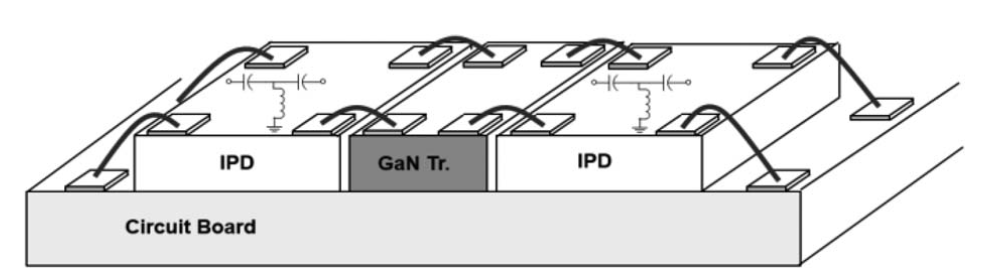

GaN Hybrid-IC 也有采用TSV来替代打线来构造回路(Microw. Opt. Technol. Lett., 59: 1087-1092.)。

审核编辑:汤梓红

- 相关推荐

- 集成威廉希尔官方网站

- 三极管

- 封装

- 互连技术

- GaN

-

芯片封装键合技术各种微互连方式简介教程2012-01-13 0

-

一文详解pcb和smt的区别2023-10-08 3371

-

一文详解pcb地孔的作用2023-10-30 1665

-

请问Ultrascale FPGA中单片和下一代堆叠硅互连技术是什么意思?2020-04-27 0

-

IGBT功率模块封装中先进互连技术研究进展2022-05-06 688

-

一文详解精密封装技术2022-12-30 1667

-

一文详解封装制程工艺2023-02-06 6227

-

一文详解半导体封装的封装互连技术2023-02-20 1672

-

一文详解分立元件门威廉希尔官方网站2023-03-27 3194

-

一文详解封装互连技术2023-04-03 5170

-

BGA和CSP封装技术详解2023-09-20 2460

-

一文详解pcb不良分析2023-11-29 1173

-

一文详解pcb的msl等级2023-12-13 9704

-

一文详解pcb的组成和作用2023-12-18 1553

-

一文详解硅通孔技术(TSV)2024-01-09 16916

全部0条评论

快来发表一下你的评论吧 !