为便携式CPU内核供电

描述

为CPU和其他高密度逻辑提供电力从来都不是一件容易的事,尽管一段时间以来,技术似乎最终会降低计算任务所需的功率。尽管技术进步很快,但对计算能力不断增长的需求似乎吸收了所有改进并要求更多。这种对功率的需求在笔记本电脑中尤为明显,尽管每瓦可用的计算能力大幅增长,但其电池寿命的延长充其量是增量的。

无论这种性能停滞不前是由于需要跟上技术的步伐,还是反之亦然,便携式系统中对更高电源电流的需求迫使设计人员熟悉新的电源技术。本文将探讨其中的一些新技术。

不断缩小的几何尺寸一直压低CPU、DSP和其他大规模逻辑器件的电源电压。目前在+1.5V至+2.5V范围内,这些电压应该很快就会达到1V。高效产生如此低的电压可能是一个问题,特别是对于 10A 及以上的输出电流。

与大多数电子设计一样,有效的电源必须协调许多相互冲突的目标,包括成本和组件数量、效率和热行为、威廉希尔官方网站 尺寸和瞬态性能(对负载阶跃的响应等)。电池寿命仅是便携式(电池供电)系统的问题,但废热(以及效率)是电池和交流供电系统的主要问题。

更严格的负载调整率 + 更快的响应 = 一场失败的战斗

当今的 CPU 内核需要非常严格的负载调节。直到最近,主要的CPU制造商都要求这样做。但是,电源电流和时钟频率会随着电源电压的下降而上升,这对电源提出了很高的要求,尤其是在负载阶跃行为方面。满足这些日益严格的性能限制的难度和成本不断增加,促使人们重新思考电源设计。作为更高负载电流和更大负载瞬变的一个结果,在处理器周围涌现的电容器“农场”增加了设计的尺寸和成本。

这些问题,以及即使是最快的开关模式稳压器也无法处理由突然负载阶跃引起的瞬时输出降这一事实,迫使人们改变思维(和规格)。输出电容必须完成所有工作,以应对当今CPU速度的阶跃响应。此外,更严格的负载调节规格导致更高的开环增益,需要更多的输出电容来保持稳定性。因此,很明显,某种放宽负载调节要求的方法将在减少组件数量和其他方面获得丰厚的回报。

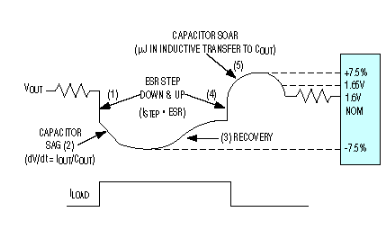

典型DC-DC转换器对负载阶跃的响应(图1)有五个基本要素:

瞬时压降,其幅度等于负载电流阶跃的增加乘以输出电容的等效串联电阻(ESR)。

瞬时压降后,在DC-DC转换器响应之前可能会出现下降,其中电容器电压随着电容器提供负载电流而下降。

电压恢复间隔,当电感接通以源出负载电流并补充输出电容时。

当负载被移除时,“ESR升压”(逆转瞬时下降的影响)。

一些过冲,因为存储在第一个电感脉冲中的能量(在负载下降之后)被传递到输出电容。

元件 2、3 和 5 可以通过精心设计和明智地选择 DC-DC 控制器来最小化。但是,瞬时电压阶跃(1和4)不能降低,除非降低输出电容的ESR。快速稳压器响应可以在初始步骤后更快地拉高输出,但不能阻止初始压降本身。即使是最快的DC-DC转换器(例如MAX1711,响应时间不到100ns)对于600MHz及以上CPU时钟引起的负载瞬变来说也太慢了。

图1.该波形说明了瞬态负载阶跃的主要分量。

电压定位

很明显,鞭打DC-DC转换器的不切实际的瞬态行为是没有希望的。600MHz CPU在MAX60的1711ns响应时间内产生100个时钟周期。如果电源电压总是下降 ESR库特× I加载步骤并在那里停留几个时钟周期,输出是否恢复到其标称值是否重要?从CPU的角度来看,这并不重要。然而,从电源的角度来看,这很重要。

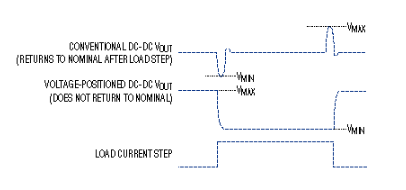

电源更希望负载下的电压永远不会恢复到“标称值”。这样,当负载被移除时,可以容纳近两倍的瞬态电压上升。同样,施加负载时允许两倍的瞬态跌落。图2显示了电压转换器响应负载阶跃的不同方式。

图2.由于电压定位稳压器不会在每个负载阶跃后尝试将输出电压恢复到中心“标称值”,因此它们允许更大的瞬态偏移。这种额外的裕量也降低了功耗和输出电容数量。

这些考虑因素催生了一种新的CPU电源规格(参见图1中的灰色框)。标称电压为1.6V,但负载相关压降可以将其降低7.5%(按照当前的CPU标准相当草率)。当负载从满负载降至零时,它也可以上升 7.5%(仅限短期脉冲)。稳态下的输出电压不得超过1.65V,包括噪声和纹波。这些数字有助于最大限度地减少电容器数量,同时大幅延长电池寿命并减少热量。

要充分利用 CPU 电源的更宽限制,您可以为给定电源定义电压/负载配置文件。该特性允许您实现受控形式的负载抑制(有时称为电压定位),其中输出电压定位为负载电流的函数。电压定位允许输出下降,并且不会浪费能量和金钱试图支撑它。相反,输出设置为随着负载电流的增加以定义的方式下降。与蛮力方法相比,这种方法对瞬态问题提供了更优雅的响应(暴力方法提供的好处有限,但需要DC-DC转换器具有更大的电容和更快的速度)。

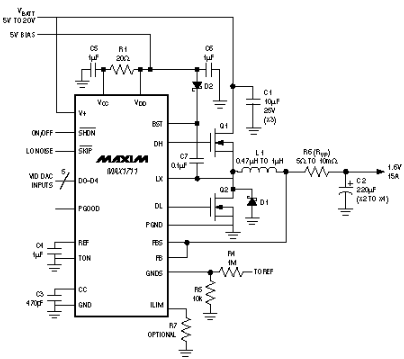

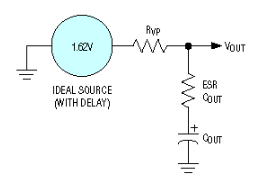

电压定位功能可以添加到许多不超过三个电阻的 DC-DC 控制器中(图 3)。R4和R5为设定输出电压增加一个小的正失调,将其从标称1.6V(在本例中)提高到1.62V。R6 (R副总裁) 与输出串联,与输出电容的最差情况 ESR 匹配。R的效果副总裁是插入一个定义的、与负载相关的压降。

图3.这种高效的 15A 稳压电源可通过增加三个电阻器轻松转换为电压定位设计:R4、R5 和 R6 (R副总裁).

| IOUT(A) | C1(µF) | L1(µH) | R6(RVP, mohm) | R7 | C2(µF) | Q1 | Q2 |

| 7 | (2) 10 | 1 | 10 | ILIM = VCC | (2) 220 | IRF7807 | IRF7805 |

| 10 | (3) 10 | 0.68 | 8 | ILIM = VCC | (3) 220 | IRF7811 | IRF7809 |

| 12 | (3) 10 | 0.47 | 7 | 220 kΩ | (4) 220 | IRF7811 | IRF7809 |

| 15 | (4) 10 | 0.47 | 5 | 210 kΩ | (4) 220 | IRF7811 | IRF7809* |

C1 = 陶瓷电容器,C2 = 松下 SP 系列:EEFUEOE221R。

*对于连续 15A 负载,由于 IR2 的热限制,请使用 (7811) IRF2 或 (7805) IRF7809。

如果RVP与滤波电容的ESR匹配,则输出下降初始负载阶跃降(ESR×ILOAD),只要负载保持不变,输出就会保持在该电平。降低负载会导致电压电平上升(ΔI×ESR)。在最后一次电感放电和控制器的100ns响应之前(但在允许的7.5%限制内)短暂的瞬态脉冲之后,直流电平再次保持在由空载电压(在本例中为1.62V)减去ILOAD×RZ定义的水平。参见图 4。

图4.图3威廉希尔官方网站

的阶跃响应说明了电压定位输出的优势。

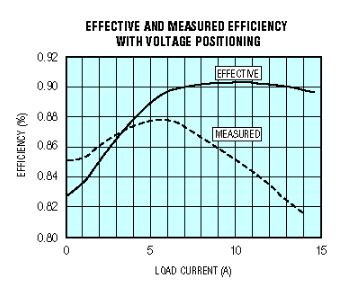

与输出串联增加5mΩ会降低效率。但是,它也会降低CPU在重负载下的工作电压,从而降低功耗并延长电池寿命。与传统(非定位)稳压器相比,电压定位设计可将 CPU 耗散降低 1.38W,总功耗降低 0.4W(图 5、6)。

图5.这个简化的模型说明了电压定位的基础知识。对负载阶跃(图2)的理想“方波”电压响应发生在R副总裁等于 ESR(C 的有效串联电阻外).

图6.尽管增加了输出电阻会降低转换效率,但电压定位设计可降低电源和CPU内部的功耗。

有效效率

由于这种改进是以牺牲转换效率为代价的,因此提出一个新术语来比较电压定位威廉希尔官方网站 与传统(非定位)威廉希尔官方网站 可能会有所帮助。该术语“有效效率”是非电压定位设计中与电压定位设计的性能相等的效率。

要确定电压定位稳压器的有效效率,首先以常规方式[(VOUT × IOUT)/(VIN × IIN)]测量其效率,然后将负载建模为每个效率数据点的电阻(RLOAD = VOUT/IOUT)。接下来,使用非定位输出电压(INP = VNP/RLOAD,在本例中为 VNP = 1.6V)计算每个 RLOAD 数据点的输出电流。然后计算每个INP数据点的有效效率,即非定位功率输出(VNP×INP)除以测量的电压定位功率输入(VOUT×IOUT)。请注意,超过100%的有效效率在数学上是可能的,但尚未实现。

图 7 显示了典型 CPU 电源的这种改进有多显著。为了匹配电压定位带来的好处,满载时的传统设计需要将效率提高近8%。

图7.这些图显示,在满负载时,电压定位的CPU电源具有8%的优势。传统设计需要 90% 的转换效率才能与提供 82A 电流的电压定位设计的 14% 效率相匹配。

-

嵌入式CPU卡在医用便携式监护仪中的应用2010-02-25 854

-

便携式示波器的技术原理和应用场景2024-10-24 0

-

用于便携式及无线应用的便携式电源管理2012-08-16 0

-

便携式UPS储能电源的简介和应用2018-09-06 0

-

怎么利用嵌入式CPU卡设计医用便携式监护仪?2019-08-22 0

-

基于嵌入式CPU卡的医用便携式监护仪怎么实现?2019-10-10 0

-

便携式UPS电源的相关资料推荐2021-11-16 0

-

便携式白噪声发生器的资料分享2022-06-29 0

-

三输入电源为3.3v便携式设备供电2009-04-27 360

-

三输入电源为3.3V便携式设备供电2009-04-30 373

-

便携式CPU内核的供电问题2009-04-30 429

-

便携式电池供电医疗设备中钽电容的使用2010-10-20 1626

-

MAX761 三输入电源为3.3V便携式设备供电2016-08-18 652

-

便携式产品的供电设计2022-07-11 324

-

便携式电池系统2018-04-24 1005

全部0条评论

快来发表一下你的评论吧 !