Vivado综合参数设置

描述

如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项的功能。本文将要介绍一下Vivado的综合参数设置。

一、Vivado综合参数介绍

在Vivado中,默认情况下,综合器会根据指定的目标芯片和设定的优化策略来产生最优的威廉希尔官方网站 实现方案。常用的选项都可以在下图菜单中设置。

1、flatten_hierarchy

这个参数决定了Vivado综合工具将如何控制层次结构,一般默认为rebuilt,主要有以下3个参数选项:

(1)full

表示采用完全展平层次结构,只留下顶层。只保留顶层层次,执行边界优化 。

(2)none

表示采用不展平层次结构, 综合后的输出具有与原始RTL相同的层次结构,且不执行边界优化 。

(3)rebuilt

表示允许综合工具展平层次结构,然后根据原始RTL重建层次结构。 此值允许跨边界优化的QoR优势,最终层次结构与RTL类似,便于分析。

2、gated_clock_conversion

控制综合工具的转换时钟逻辑能力,使用门控时钟转换还需要使用RTL属性才能工作。

3、fsm_extraction

控制状态机的编码方式综合方式,默认值为auto,此时vivado会自动推断最佳的编码方式,它有以下几个选项:关闭、sequential、独热码、自动等等,其设定的FSM编码方式优先于HDL代码中定义的方式。

4、fsm_encoding

设置针对某个状态机设定编码方式,综合属性 -fsm_coding的优先级高于-fsm_extraction,但如果HDL代码中已经定义了编码方式,该设定将无效。

5、 Keep_equivalent_registers

设置是否保留等效寄存器,equivalent registers也就是等效寄存器,共享输入数据的寄存器。 勾选时,等效寄存器不会合并; 不勾选时,等效寄存器会被合并。

6、resource_sharing

设置算术运算通过资源共享来优化设计资源,默认值为auto。

7、control_set_opt_threshold

设置是否开启控制集的优化,以减少控制集的个数,但会增加LUT资源消耗。 触发器的控制集由时钟信号、复位/置位信号和使能信号构成,通常只有{clk,set/rst,ce}均相同的触发器才可以被放置在一个SLICE中,但开启这个参数后3个触发器会被放置到同一个SLICE中。

8、no_lc

是否开不允许出现LUT整合。 通过LUT整合可以降低LUT的资源消耗,但也可能导致布线拥塞。 因此,xilinx建议,当整合的LUT超过了LUT总量的15%时,应考虑勾选-no_lc,关掉LUT整合。

9、shreg_min_size

影响移位寄存器的实现方式,默认值为3。 当HDL代码描述的移位寄存器深度大于此设定值时,将采用“触发器+SRL+触发器”的方式实现,其中SRL由LUT实现。

10、bufg

控制综合时推断出来的BUFG数量。 当综合过程中看不到设计网表中的其他BUFG时,Vivado设计工具会使用此选项,可以推断出指定的数量,并跟踪在RTL中实例化的BUFG数量。 例如,如果bufg选项设置为12并且在RTL中实例化了三个BUFG,则该工具最多可以推断出9个BUFG。

11、fanout_limit

设置全局信号高扇出数目,但当HDL代码中有MAX_FANOUT时,该属性失效。

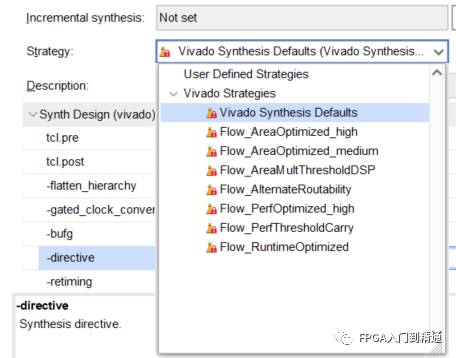

12、directive

设置不同的优化策略,主要选项参数如下:

- Default,默认设置。

- RuntimeOptimized,执行最短时间的优化选项,会忽略一些RTL优化来减少综合运行时间。

- AreaOptimized_high/medium,执行一些通用的面积优化。

- AlternateRoutability,使用算法提高布线能力,减少MUXF和CARRY的使用。

- AreaMapLargeShiftRegToBRAM,将大型的移位寄存器用块RAM来实现。

- AreaMultThresholdDSP,会更多地使用DSP块资源。

- FewerCarryChains,位宽较大的操作数使用查找表(LUT)实现,而不用进位链。

13、max_bram

设定当前工程的最大块RAM数量,通常在设计中有黑盒或第三方网表时使用,默认设置为-1时,表示使用当前芯片的最大块RAM数量。

max_uram:指定ultra ram最大使用个数。 max_bram_cascade_height:指定bram最大级联数。 max_uram_cascade_height:指定uram最大级联数。

14、max_dsp

设定当前工程的胡最大块DSP的数量。 与max_ram一样。

15、cascase_dsp

控制sum DSP块输出中的加法器,默认为auto。 auto表示使用块内置加法器链计算DSP输出的总和。 tree强制在结构中(Fabric)实现总和。

16、tcl.pre和tcl.post

在综合之前和之后立即运行的Tcl文件

二、重要选项介绍

1、Report Setting

设置是否开启综合资源消耗报告,默认开启即可,如果不需要看,可以关闭。

2、Setting设置中的Strategy

这里可选不同优化策略设计,使得设计满足相应的需求,如下图所示:

(1) “速度优化”:使时钟频率最快。 面积和功耗可能更大。

(2) “平衡优化”:在速度和面积之间取得平衡。

(3) “面积优化”:使元素数量最少,但可能会影响时钟速度和功耗。

(4) “功耗优化”:降低功耗。

三、HDL代码设置综合属性

1、srl_style

srl_style可设定移位寄存器的不同实现方式,主要有以下几种方式:

(* srl_style = “srl_reg” ),实现移位寄存器为SRL + FF结构。

( srl_style = “reg_srl” ),实现移位寄存器为FF + SRL结构。

( srl_style = “reg_srl_reg” ),实现移位寄存器为FF + SRL + FF 结构。

( srl_style = “register” ),实现移位寄存器为纯FF结构。

( srl_style = “srl” *),实现移位寄存器为纯SRL结构。

其中SRL可以有效减小面积,相比级联寄存器的结构性能要更好,如果再加了FF,时序性能更好。

2、ram_style和rom_style

定义存储器实现方式,主要有以下几种方式:

(*ram_style = "block" *),表示用Block RAM实现

(*ram_style = "reg" *),表示用寄存器实现

(*ram_style = "distributed" *),表示用分布式 RAM实现

(*ram_style = "uram" *),表示用uram实现

3、use_dsp48

定义实现这部分算术运算使用dsp资源进行实现,常用形式为:( use_dsp48=“yes” )。

(*use_dsp48=“yes”*) reg test;

4、dont_touch

dont_touch可以防止相关内容被逻辑优化,常用形势为:( dont_touch =“yes” )

(*dont_touch =“yes”*) reg test;

5、max_fanout

设置当前信号的最大扇出数目,常用形式为:(* max_fanout = “20”*)

(*MAX_FANOUT = 50 *) reg test;

-

PMAC_参数设置2016-04-26 1060

-

pmsm电机的pid参数设置的方法学习资料分享2018-04-11 1397

-

变频器的参数设置及缺陷的处理2020-09-23 1646

-

变频器功能参数设置2023-01-31 10662

-

变频器参数设置2023-04-07 1034

-

变频器设置面板及参数设置方法2023-04-10 926

-

Vivado布线和生成bit参数设置2023-05-16 4647

-

变频器参数设置方法2023-07-11 5392

-

串口屏LUA教程3-系统参数设置2021-04-29 614

-

变频器的常用参数设置2023-12-29 3846

-

汇川变频器参数设置2024-01-11 7594

-

东元驱动器参数设置步骤及注意事项2024-04-12 1988

-

变频器的基本参数设置2024-06-07 1409

-

金田变频器怎么调参数设置2024-06-18 3600

-

变频器参数设置技巧介绍2024-06-28 1307

全部0条评论

快来发表一下你的评论吧 !