PCI Express突飞猛进:与PCIe 6.0实现高带宽互连

描述

PCI-SIG®发布了PCI Express®规范PCIe® 6.0的最新修订版。凭借 64GT/s 原始数据速率物理层,可通过 256 通道配置实现高达 16 GB/s 的数据传输。通过此次发布,PCIe 继续满足行业对高带宽和低延迟互连的需求,其潜力可以通过依赖存储 (NVMe) 和一致性 (CXL) 协议加以利用。

PCIe 6.0 的带宽比 PCIe 5.0 翻了一番,这是通过摆脱差分信号并使用成熟的 PAM4 调制和灰度编码技术来实现的。此外,智能前向纠错和重放技术可在链路伙伴之间提供低延迟传输。

与上一代相比,该规范继续保持与现有设备发现和软件生态系统的向后兼容性,并在每一层中进行了大量改进。

大量更改位于数据链路层中,包括 Flit 序列号、信用流控制和 Flit 结构定义。

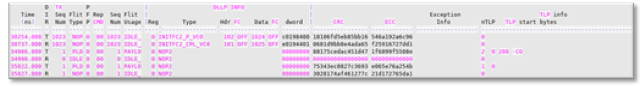

新的 256B Flit 模式,加上高效打包,分配给 TLP、DLLP、CRC 和 ECC。下面的快照捕获了 Synopsys 验证 IP 事务日志中的 Flit 交换事务。如下所示,交换带有 NOP 的 Flit 或带有或不带有 DLLP 的有效负载。

引入的链路层更改旨在修复序列号滚动更新和共享/专用积分的问题。为了解决序列号翻转问题,具有有效负载的 Flit 的序列号递增;所有其他 Flit 都使用与上一个 Flit 相同的序列号。为了帮助促进这一点,更新了 Flit 用法以指示有和没有有效负载的 Flit。共享积分机制经过调整,可防止 1 个 VC 主导所有共享积分。在 Flit 模式下,共享积分是“默认”,专用积分仅在需要时使用。使用共享/专用配额的 TLP 之间的区别使用 Flit 模式前缀进行管理。

由于灰色编码和预编码规则的变化,物理层的变化带来了一定程度的向后不兼容。更新了以 64GT/s 执行环回均衡和以 64GT/s 进入合规性的 LTSSM 规则。其他 LTSSM 更改包括在 Flit 模式下向恢复状态添加新的状态转换,以及对 64GT/s 均衡过程的调整。

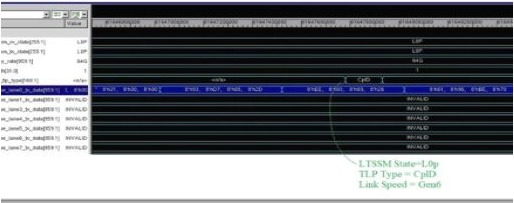

下面是 VIP 波形的快照,说明了在链路伙伴之间启用完全均衡的情况下,速率更改为 PCIe 6.0。

新的节能状态 L0p 仅适用于 Flit 模式。L0p 是 LTSSM 的传统 L0 状态的一部分,使用配置的链路宽度来节省功耗。下面的快照描述了链路宽度配置为 0 通道的 L1p 过渡。即使在这种状态下,数据传输也会继续发生。

PCIe 堆栈关键层的更新也带来了从 IP 扩展到 SoC 再到系统的 PCIe 6.0 设计的功能验证方面的一些挑战。

审核编辑:郭婷

-

华为WiMAX业务突飞猛进 与对手仍有差距2008-10-05 0

-

国外PCIE的书籍《pci express system architecture》2017-06-06 0

-

PCI Express的基本工作原理2009-10-23 1307

-

IDT推出新系列PCI Express (PCIe) 系统互2008-10-28 741

-

IDT宣布推出PCI Express Gen2 系统互连交换2010-02-11 858

-

射频识别(RFID)半导体市场未来几年将突飞猛进2011-02-05 976

-

GaN——如何让RF功率放大器带宽和功率突飞猛进2018-03-13 2049

-

AI助力语音识别技术获得突飞猛进的发展2019-09-09 667

-

全球区块链市场到2023年将实现突飞猛进的增长2019-11-26 669

-

Linux5.11开始围绕PCI Express6.0进行早期准备2020-12-17 1631

-

PCIe 6.0的新变化与新挑战2022-04-13 4872

-

使用多代 PCIe 构建高性能互连2022-07-21 1678

-

如何破解PCIe 6.0带来的芯片设计新挑战?2023-01-19 928

-

PCIe 6.0入门之什么是 PCIe 6.02023-05-22 6451

-

示波器带宽要求解析2023-11-03 2035

全部0条评论

快来发表一下你的评论吧 !