UCIe为后摩尔时代带来什么?

描述

随着摩尔定律的失效,芯片集成度的提高遇到了困难。英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)于上世纪60年代提出,芯片集成度每18-24个月就会翻一番,性能也会提升一倍,这被称为摩尔定律。我们可以将摩尔定律比作一辆不断升级的汽车。每个18到24个月,这辆汽车就会升级换代,增加更多的功能和性能。比如,引擎会变得更强大,车身会更加轻便,空气动力学也会更加优化,使得这辆汽车更加高效和安全。同时,这辆汽车的制造成本也在不断降低,使得更多的人们能够拥有它。

随着晶体管尺寸的不断缩小,到了14/7纳米以下,芯片制造面临着一系列问题。第一是散热的问题,由于晶体管尺寸的缩小,芯片的尺寸也变得越来越小,这导致芯片内部的热量密度增加。同时,芯片内部的威廉希尔官方网站 也变得更加复杂,这使得散热问题更加困难。因此,需要更高效的散热技术来避免芯片过热导致性能下降甚至损坏,例如通过优化晶体管布局和材料选择来降低功耗和热量产生。

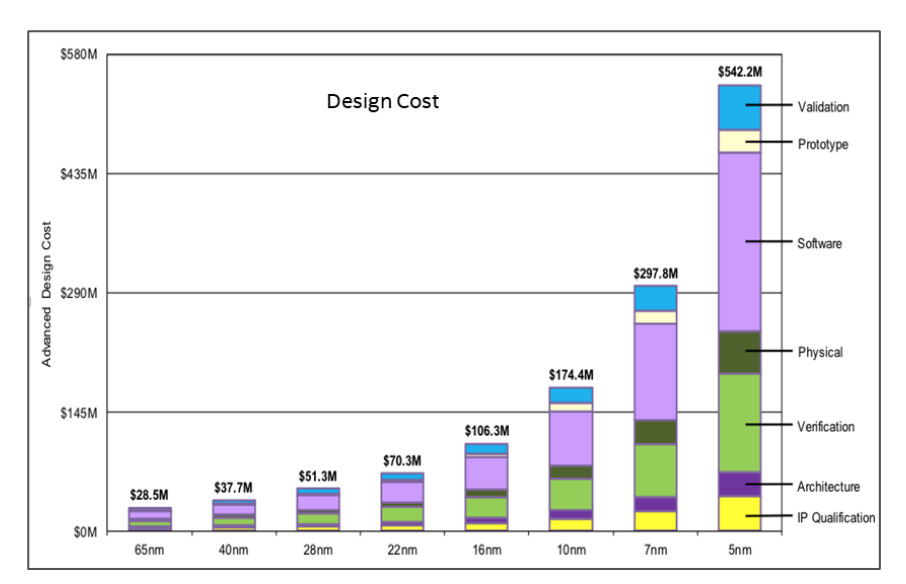

另外,芯片制造还面临着良率问题。在芯片制造过程中,晶体管数量的增加和密集度的提高会增加芯片出现问题的概率。即使只有一个晶体管出现问题,整个芯片也可能无法正常工作。这会导致制造商的成本增加。据统计,制造65nm芯片的成本为2850万美元,而制造7nm的成本则需要近3亿美元,而到了5nm,这个成本还需要再次翻倍。此外,芯片制造的良率也受到晶圆大小的影响,晶圆越大,晶体管密度增加,晶圆上的芯片数量越多,良率也越低。因此,需要进行严格的测试来确保芯片的质量和可靠性。随着芯片的集成度和复杂度的不断提高,芯片制造的难度和成本不断增加,因此芯片的良率和测试也变得越来越重要。

这些问题使得制造商难以继续遵循摩尔定律的速度提高芯片的集成度和性能,因此需要采用新技术和新方法来解决这些问题。

不同工艺节点下的设计成本

(Source: IBS, as cited in IEEE Heterogeneous Integration Roadmap)

在后摩尔时代,Chiplet技术成为了重要的解决方案。Chiplet技术可以将不同或相同功能的芯片集成在一起,实现更高的计算和处理能力,同时也可以提高芯片的良率,并降低成本和风险。Chiplet技术的优势之一是可以将不同制造工艺的芯片集成在一起。举例来说,如果需要高性能的CPU和GPU,可以选择使用5纳米或3纳米的工艺来制造,而对于一些IO和power等威廉希尔官方网站 ,可以使用成熟的工艺来制造,以降低成本和风险。这种做法的好处在于可以根据不同的需求选择不同的工艺,从而提高芯片的性能和灵活性,同时也可以降低成本和风险。

然而,Chiplet的发展面临着一个重要的瓶颈,即互连问题。

为了实现不同芯片之间高速、可靠互连,以实现数据传输和共享,Chiplet技术中采用了PCIe、BOW等接口标准。然而,这些标准并不是专为Chiplet设计的,或未定义完整的协议及封装等标准。这导致了芯片制造商之间的互操作性问题,限制了Chiplet技术的发展和应用。为了解决这个问题,通用Chiplet互联技术UCIe(Universal Chiplet Interconnect Express)标准应运而生。

UCIe是一个开放的行业互连标准,旨在为芯片制造商提供一种通用的芯片互连标准,以降低芯片互连的成本和风险,并促进Chiplet技术的生态系统拓张和推广。UCIe标准可以实现小芯片之间的封装级互连,具有高带宽、低延迟、经济节能的优点。该标准定义了完整的协议和封装,可以支持高速、可靠的芯片互连,并提供了灵活的拓扑结构和配置选项,以满足不同应用场景的需求。UCIe标准的开放性和通用性使得它可以被广泛应用于各种不同的计算领域,包括云端、边缘端、企业、5G、汽车、高性能计算和移动设备等,以满足对算力、内存、存储和互连不断增长的需求。通过采用UCIe标准,芯片制造商可以实现更高的计算和处理能力,同时也可以降低芯片制造的成本和风险。

UCIe标准是一种通用的芯片互连标准,其主要特点包括高带宽和低延迟、灵活性和可扩展性、可靠性以及生态系统完整性。高带宽和低延迟可以提高芯片的性能和效率,使其能够更好地满足不同应用场景的需求。灵活性和可扩展性可以支持不同的拓扑结构和配置选项,以满足不同应用场景的需求。可靠性可以确保芯片互连的可靠性和稳定性,从而提高芯片的可靠性和稳定性。生态系统完整性可以促进芯片制造商之间的合作和互操作性,推动其推广和普及。

UCIe标准是芯片设计和产业发展的一大亮点,它将为Chiplet的发展和应用带来更多的创新和机遇。未来,我们可以期待UCIe标准在数据中心、人工智能、云计算等领域发挥更加重要的作用,为我们的生活带来更多的便利和创新。

芯耀辉作为中国接口IP领军企业,于Chiplet早期就开始研究和开发相关技术,后又作为首批IP供应商于2022年4月加入UCIe组织,并率先推出了完整的Chiplet D2D解决方案,包括物理层、控制器和封装,能够更好地满足不同行业和应用的需求。同时,芯耀辉积极参与了中国首个原生Chiplet标准的制定,该标准由中国集成威廉希尔官方网站 领域相关企业和专家共同主导,由工信部中国电子工业标准化技术协会于2022年12月审核发布。芯耀辉作为重点贡献企业,积极参与该标准的制定,为推动Chiplet的发展和应用作出了突出贡献。

此中国首个原生Chiplet标准,既定义了并口,也定义了串口,其协议层的自定义数据包格式与UCIe保持兼容,且在封装上的标准主要采用国内可实现的技术,可直接使用国内已有生态开发及落地Chiplet技术。所以,芯耀辉的参与和贡献加速了UCIe标准的推广和应用,还为后摩尔时代的芯片设计提供了一个完整的、可落地的Chiplet解决方案。随着技术的不断发展和创新,Chiplet将会在数据中心、人工智能、云计算等领域扮演越来越重要的角色。我们相信,有了UCIe标准的支持和芯耀辉等企业的积极参与,Chiplet将会迎来更加广阔的发展前景。Chiplet技术的不断发展和创新将为推动数字经济和智能化社会的发展作出更大的贡献。

审核编辑:汤梓红

-

根据“后摩尔时代”芯片行业如何发展?2017-06-27 0

-

IC在后摩尔时代的挑战和机遇2010-02-21 1227

-

后摩尔定律时代的骨干网挑战2011-02-28 1308

-

后摩尔时代集成威廉希尔官方网站 产业特性及发展趋势2021-01-10 10397

-

吴汉明以《后摩尔时代的芯片挑战和机遇》发表了演讲2021-06-17 2061

-

重磅演讲:持续推进摩尔时代的IC设计艺术2021-11-16 4971

-

聚焦后摩尔时代,后摩尔时代集成威廉希尔官方网站 产业如何突破2022-04-08 1578

-

如何调节后摩尔时代的架构计算之争2022-06-13 1242

-

普莱信智能孟晋辉出席CSPT 2022,共探后摩尔时代的封装技术2022-11-16 1025

-

后摩尔时代,十大EDA验证技术趋势展望2023-01-04 458

-

重磅:Keysight官宣加入UCIe联盟2023-02-22 602

-

后摩尔时代,从有源相控阵天线走向天线阵列微系统2023-05-18 849

-

SiP封装技术将制霸“后摩尔时代”?利尔达首款SiP模组应运而生!2022-07-20 925

-

后摩尔时代芯片互连新材料及工艺革新2023-08-25 924

全部0条评论

快来发表一下你的评论吧 !