有关FPGA的问答集锦

描述

本文整理自2023年6月12日~6月18日,本公众号【FPGA算法技术交流群】的相关问答。相关问题的解答和交流来自群成员,仅作参考。

问

FPGA做IC的原型验证,速度大概跑多少?很多ASIC运行主频远远高于FPGA,仿真能cover住吗?

答

FPGA主要用来做功能验证,一些接口确实需要那么高那就上,其他的不需要。Emulator可用并行计算时序的方式来仿真,更加接近仿真,但比仿真快得多。Emulator大概几M的速度,Prototype大概10到100M。流片之前尽可能去模拟他的功能和性能,最接近的就是FPGA原型验证。

问

PHY怎么验证到位?正确性由谁来保证呢?

答

原型验证的PHY也不一定和ASIC的一致,保证通路即可。另外有些PHY可以用FPGA自带的PHY IP来模拟。任何验证手段都是互相补充,最终达到完备性。

模拟的器件会有模拟端来验证,数字的基本功能都会先在Simulation保证,纯数字就代表可综合。模拟的就会抽可综合的模型来替换。模拟的设计在模拟端保证,和数字集成到一起的时候就会模拟数字化。

PHY有单独的IP,接口协议都是统一的。例如PCIe、DDR4、Ethernet等。Simulation和Emulator都有相应的PHY model,FPGA阶段也可以用原厂的PHY板,但有时没必要,因为高速接口都是标准的,所以可能会用别的ip去代替,然后和真实device连接,保证通路,软件测试通过就可以。

如果是数模混合芯片,设计过程中数字可以把RTL或后端输出的网表,导入给模拟工程师做模拟域的仿真。反过来模拟也可以出verilog模型给数字工程师在数字域仿真。

问

2MHz ,2V Vpp,放大到10vpp,应该选用多大的运放?如何计算带宽?

答

如果是电压反馈运放,建议选择20M以上,理论计算10M以上即可。而且应该是全功率带宽,不能只看小信号带宽。如果是电流反馈型,选个5M估计足够,另外就是电流驱动能力。带宽的话,运放指标主要是增益带宽积,开环增益和开环带宽的乘积。

问

有个问题请教一下,FPGA芯片怎么能把10k的时钟扩到100M?

答

MMCM和PLL的输入下限分别是10M和19M,设计思路可能需要和团队一起商讨一下。

问

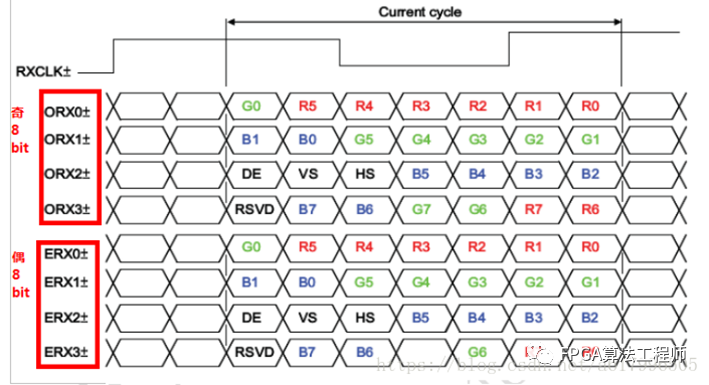

请教一个LVDS接收问题。需要考虑如何将数据和时钟对齐。但是LVDS视频流没有同步码,大家是怎么处理同步?

答

有两种方法,要么数据里边有特殊字符,要么有其它信道传输同步信息。对于视频图像,一般都会有接口协议,行、场同步信号。

de就是同步信号,hs是行同步,vs是场同步。把视频流用显示器显示出来,然后通过修改skew然后找到图像由坏变好和由好变坏的临界点,然后中间位置就是最稳定的,一般调整90°就行。还有一些芯片自备prn码调试这个skew。其实对于这种VESA格式的视频流,还有更简单的方式,直接调用Xilinx的selectio ip核。采用DDR模式就能采下来。

如果用不了DDR模式,可参考Xilinx的Xapp585,就是这种时序的例程。里面收发都有,还有gearbox例程,教你怎么样将8bit或者4bit转为7bit。

此外,对于接收数据,Xapp524讲这个,需要做个状态机,找到delay调整值,每次上电之前等这个状态机稳定了再开始拿数据。但是这个设计是不考虑系统温升对IO的影响的,如果可靠性要求高,需要隔一段时间校准一下IO的delay。

问

有没有逻辑优化的一些资料?

答

推荐高亚军老师的《AMD FPGA设计优化宝典》,VHDL版已上市,verilog版据说即将出版。

此外,《高级FPGA设计:结构、实现和优化》也可以看看。

问

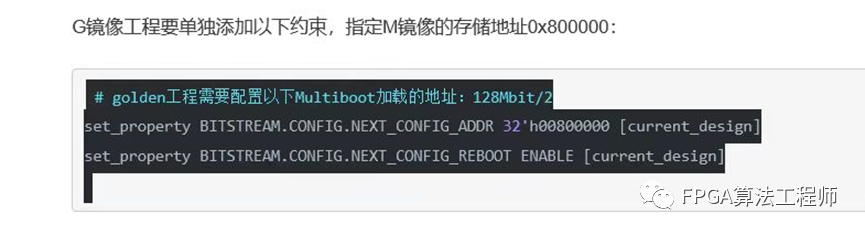

这个镜像地址是根据flash确定的吗?

答

golden起始地址必须是0,upgrade是800-000,16M flash空间的一半。

问

输入输出双向的端口(inout),我直接定义为输出端口(output)使用,大家有这样用过嘛?会有问题嘛?

答

FPGA的user IO,威廉希尔官方网站 结构是双向的。然后我们根据需要,声明位input/output或者inout。外部I2C器件,把scl定义为output,可以正常访问。如果是zynq的PS I2C,要声明为双向,sda要设置为双向。如果PS的I2C拉到EMIO,那么SCK也要设为双向。尽管就PS一个主设备。

问

求问,Vivado里FFT和LTE FFT的IP核有啥区别呢?

答

LTE FFT要收费,但是支持1536点。LTE FFT说白了就是额外支持3*2^k点数的变换。Vivado里DFT点数支持1536,可以使用统一的2048点FFT实现所有带宽模式的处理。

问

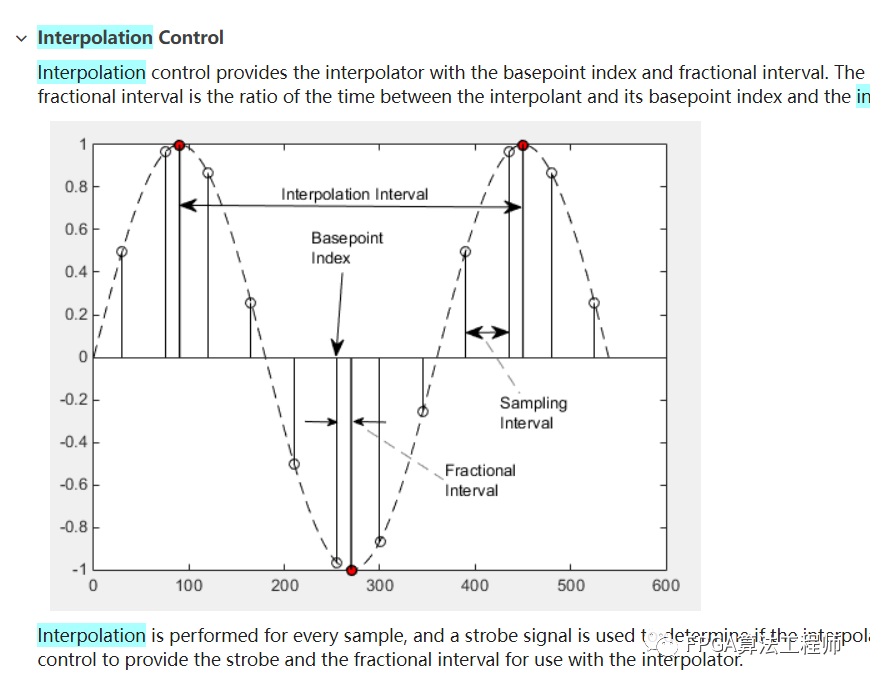

8184点数据,怎么均匀下采样到2048个数据啊?采样时钟的8.184M,1ms相干积分。

答

设计算法时候需要考虑硬件实现,AD采了样,DFE中滤波,可以再来个法罗插值找最佳采样点。符号定时同步,可以参考一下Michael Rice的《Digital Communications:A Discrete-Time Approach》中的第8章:Symbol Timing Synchronization。此外,也可参考一下Umberto Mengli的《Synchronization Techniques for Digital Receivers》。

问

AXI4,AXI4-Lite,AXI-Stream这三个在应用上怎么考虑选择?

答

AXI4包含3种类型的接口: (1)AXI4:主要面向高性能地址映射通信的需求; (2)AXI4-Lite:是一个轻量级的,适用于吞吐量较小的地址映射通信总线; (3)AXI4-Stream:面向高速流数据传输。

第一个有突发,第二个无突发,第三个无地址。在仿真时,Vivado 模板 AXI-Lite Master和AXI-Lite Slave连上仿真,AXI4可以和MIG连着仿真。Xilinx 有个AXI Verification IP ,就四步骤:1.引入两个package,2.声明agent,3.用new还是start 函数,即创建和挂载,4.写一些task。可以参考官方的例程。

此外,可以看一下本公众号之前的一篇文章,点击链接《AMBA协议规范(一)》可跳转原文阅读。

问

FFT后实部,虚部的bit位宽是如何确定的?

答

Xilinx的IP,一般在处理IQ信号时,都是虚部在高位,实部在低位。IP配置时,在左侧栏,能显示FFT的输入和输出位宽,和定点格式。FFT的输出位宽和输入也有关系,配置的时候注意。此外,DFE和ADC的IQ数据位宽和实部、虚部,将决定FFT的输入。

问

flash读写,一般是大端还是小端?如果是QSPI,读写一个字节比如3E,是先3还是先E啊?

答

看QSPI的协议规定,注意位序。

问

mcs文件固化,读写flash是跟bin文件还是mcs文件对得上?

答

理论上,mcs和bin 都可以,习惯用bin。

问

FPGA需要这样的一个场景,MUX选择是从6个时钟中选择1个,并且时钟频率都不低(有没有合理使用BUFGMUX的方案,我目前能想到的是利用多级BUFGMUX来实现)?

答

不建议切时钟,而是逻辑设计中做跨时钟处理,切时钟可靠性不好做。如果硬要这么设计,试一下Vivado的MMCM动态配置功能。

审核编辑:汤梓红

-

PROTEL应用常见问题及问答集2012-08-04 0

-

手机RF设计问答大全2012-08-09 0

-

fpga精选问答集锦2012-12-20 0

-

运放经典问答集萃及其最新工业和科技趋势2015-03-18 0

-

航顺芯片问答集2018-09-13 0

-

高速PCB设计入门概念问答集2009-09-26 479

-

PCB设计经典问答集2010-04-03 496

-

高速PCB设计入门知识问答集2008-07-17 979

-

PCB电镀知识问答集锦2009-03-20 1032

-

PCB Layout and SI设计问答集锦2009-04-15 1397

-

CAXA经验谈问答集2009-10-18 1924

-

购买iphone问答集汇2010-02-02 313

-

电阻器的种类及其特性问答集汇2010-03-04 576

-

特瑞仕 | 线性稳压IC网络研讨会问答集锦,请查收~2023-06-17 361

全部0条评论

快来发表一下你的评论吧 !