关于RISC-V你需要知道的大事儿

描述

最近都在弄全志以及平头哥的risc-v ,如果有正在用的小伙伴欢迎入群交流答疑,不用的或者没弄过的勿入,谢谢!

RISC-V里面的细节特别多,如果你不是专门从事处理核心或者工具链开发的没必要了解那么细致。

RISC-V作为处理器领域的新秀频繁出现于学术与产业新闻。

2022年6 月 21 日,RISC-V 国际组织宣布了 2022 年的首批四项规格和扩展的批准 ——RISC-V 高效跟踪(E-Trace)、RISC-V 主管二进制接口(SBI)、RISC-V 统一可扩展固件接口(UEFI)规格,以及 RISC-V Zmmul 纯乘法扩展。

什么是RISC-V?

RISC-V, 其中文名称是第五代精简指令集(Reduced Instruction Set Computing)。该指令集是由加州大学伯克利分校发布的一套用于处理器的指令集。

2010年,该学校的研究团队准备做一个CPU,但是Intel和ARM高昂的授权费用让他们下决心自己做一套开源的指令集。于是经过了几个月的努力,后来就有了RISC-V。该指令集一经推出就受到了广泛关注,后来成立了RISC-V基金会,专门负责RISC-V的维护与推广。

2. 什么是指令集,指令集与处理芯片之间有什么关系?

处理器是一块芯片。而芯片并不会自己工作,需要有人告诉它该做什么操作。例如告诉芯片下个操作做加法,这就是一条指令。

在人类社会中指令基本上是以语言或者声音的形式存在,而在计算机系统中,指令是以二进制数存在的。一个芯片指令的合集就叫指令集。指令集规定了二进制数的格式、寻址方式、操作类型等。市面上常见的指令集有PC机常用的X86指令集、ARM的指令集等等。

一般来讲,先有指令集,才会有芯片来支持指令集。所以指令集可以说是芯片的早期蓝图。指令集类似一种标准,定义了芯片支持的功能。而芯片是一个实物,实现指令集定义的功能。所以你常听的RISC-V处理器,实际上是支持了RISC-V指令集的处理器芯片。

3. 为什么RISC-V在国内如此受关注?

RISC-V作为较新的指令集,技术上是有一定的优势,其实最大的原因是这个指令集是开源免费的,基于这套指令集设计的芯片无论用于科研和商业均无需给Intel和ARM上税。目前市面上常见的指令集都是要收费的,例如华为麒麟芯片,就购买了ARM家的指令集。这些有指令集知识产权的公司均为国外公司,非常不利于我国实现关键芯片的自主可控。

目前,国内外已经有非常多的RISC-V核心RTL代码,好多是开源的,如果你感兴趣可以下载一个研究研究。如果用于商用,国内外也有许多商业公司提供稳定的RISC-V IP核心。例如国外的SiFive公司、Microsemi公司、国内的阿里平头哥、芯来科技等公司。

4. RISC-V技术上有什么优势?

技术优点总结起来就一句话:短小精悍、扩展性强。处理器发展了非常多年,里面的坑坑洼洼都被研究的清清楚楚,但是由于ARM和X86的指令集一路走来,需要兼容的东西多,包袱越来越重,导致指令集越来越复杂。

RISC-V吸取了这些经验后指令集每个功能都被安排的明明白白,所以够精简。RISC-V最基础的指令数目仅仅有40多条

5. RISC-V指令集与芯片目前还有哪些问题?

最大的问题是RISC-V作为一个开源的指令集架构,其相关的编译器、开发环境、甚至成品芯片等相关生态仍然还在建立之中,生态不够强大,大规模应用还需要一个过程。

6. RISC-V指令集里有什么?

RISC-V作为一个模块化的指令集,其指令集分成了若干模块。又分为32bit和64bit版本。所以叫RV32, RV64。

7. RISC-V的核心是如何与AI加速核心集成的?

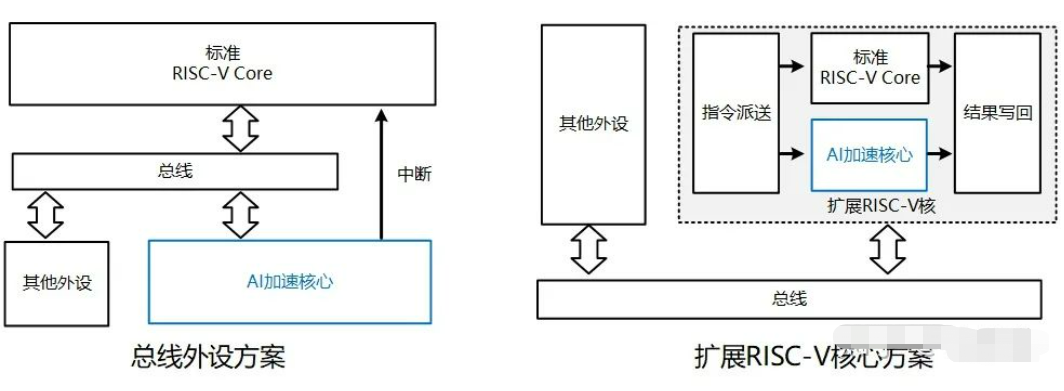

从整体实现方式上来讲,共有两种方式可以实现AI加速核心与RISC-V计算核心的集成。

方法一是总线外设方案,该方案可以直接把AI加速核心当作一个总线高速外设挂载于SOC系统。

方案二是RISC-V指令集独有的办法,扩展RISC-V核心方案。利用RISC-V指令集可扩展的特性,添加专门的AI指令,在设计微内核时加入一个指令派送单元,将AI加速指令直接派送给AI加速核心。

实际上,由于神经网络计算的过程中几乎不需要条件判断等操作,规律的乘加操作占据大多数运行时间,两种实现方案并无本质差别。

扩展RISC-V核心的方案优势在于当总线外设较多时,共用了微内核资源,减少了总线开销。而扩展RISC-V核心方案的缺点是对RISC-V编译工具链要做少许修改,增加额外的工作量。

8. 最后,总结来讲,RISC-V需要了解什么?

RISC-V是一种处理器指令集。

RISC-V处理器指支持RISC-V指令集的芯片。

RISC-V主要优势在于开源免费、短小精炼、扩展性强。

RISC-V目前的问题在于生态不成熟。

RISC-V与加速核心集成有总线方案和扩展指令集方案。

特点:

完全开源

对指令集使用,RISC-V基金会不收取高额的授权费。

架构简单

RISC-V架构秉承简单的设计哲学。体现为:

在处理器领域,主流的架构为x86与ARM架构。x86与ARM架构的发展的过程也伴随了现代处理器架构技术的不断发展成熟,但作为商用的架构,为了能够保持架构的向后兼容性,其不得不保留许多过时的定义,导致其指令数目多,指令冗余严重,文档数量庞大,所以要在这些架构上开发新的操作系统或者直接开发应用门槛很高。

而RISC-V架构则能完全抛弃包袱,借助计算机体系结构经过多年的发展已经成为比较成熟的技术的优势,从轻上路。RISC-V基础指令集则只有40多条,加上其他的模块化扩展指令总共几十条指令。

易于移植Lnix

现代操作系统都做了特权级指令和用户级指令的分离,特权指令只能操作系统调用,而用户级指令才能在用户模式调用,保障操作系统的稳定。

RISC-V提供了特权级指令和用户级指令,同时提供了详细的RISC-V特权级指令规范和RISC-V用户级指令规范的详细信息,使开发者能非常方便的移植linux和unix系统到RISC-V平台。

模块化设计

RISC-V架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一起,从而试图通过一套统一的架构满足各种不同的应用场景。用户能够灵活选择不同的模块组合,来实现自己定制化设备的需要,如RV32IMFDC的指令集,使用Machine Mode(机器模式)与User Mode(用户模式)两种模式。

完整的工具链

对于设计CPU来说,工具链是软件开发人员和cpu交互的窗口,没有工具链,对软件开发人员开发软件要求很高,甚至软件开发者无法让cpu工作起来。在cpu设计中,工具链的开发是一个需要巨大工作量的工作。

如果用RISC-V来设计芯片,芯片设计公司不再担心工具链问题,只需专注于芯片设计,RISC-V社区已经提供了完整的工具链,并且RISC-V基金会持续维护该工具链。当前RISC-V的支持已经合并到主要的工具中,比如编译工具链gcc, 仿真工具qemu等

开源实现

BOOM: Christopher Celio的RV64乱序处理器实现。

成功的流片案例

已经有机构和商业公司流片的案例。可关注RISC-V社区了解具体信息。

社区贡献

完整的工具链维护,大量的开源项目。

最后的最后,我个人是很看好RISC-V的发展前景的。

也许我国在这个领域里会出现下一个Intel或者ARM实现真正的处理器强国梦。但目前阶段RISC-V也确实存在各种各样的问题。

生态不全面等等问题会给商业化带来不小的挑战。

同时,似乎现在都喜欢炒概念,从可穿戴设备到VR/MR/AR,共享经济,再到AI,再到RISC-V,物联网等等。一个又一个风口,如何鉴别哪些是概念哪些真的可以改变世界还是得多学习。

例如RISC-V和AI,我个人觉得从技术角度来讲RISC-V可以给AI加速SOC提供一些灵活度,但是远达不到颠覆AI加速器的程度,只是相比于ARM家的处理器解决了一些痒点而已。

希望国内RISC-V可以稳步发展,不盲目追热点,找准其优势。要么出现一批拳头产品,打破垄断。要么干脆做到旧时王谢堂前燕飞入寻常百姓家,把CPU做成Linux一样彻底开源的东西。

-

RISC-V的MCU关于USB高速通信设计的难点2024-05-27 0

-

为什么选择RISC-V?2020-07-27 0

-

RISC-V你了解多少?2020-08-13 0

-

RISC-V有哪些特点2020-08-25 0

-

RISC-V 生态架构浅析2021-06-18 0

-

RISC-V架构简介2021-07-28 0

-

RISC-V 发展2023-04-14 0

-

关于risc-v启动部分的思考2020-12-28 5558

-

RISC-V有什么软件生态,RISC-V IP在芯片中的应用2021-06-22 4135

-

关于RISC-V 5大潜力和优势2022-10-14 2459

-

关于隔离器件,你需要知道的三件事2022-10-28 518

-

关于步进电机你需要知道的一切2023-03-07 1973

-

关于RISC-V ,这是你需要知道的!2022-11-10 1549

-

RISC-V和RISC-V AI的未来(特邀讲座)2023-07-14 496

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 377

全部0条评论

快来发表一下你的评论吧 !